UMBC A B M A L T F O U M B C I M Y O R T 1 - PowerPoint PPT Presentation

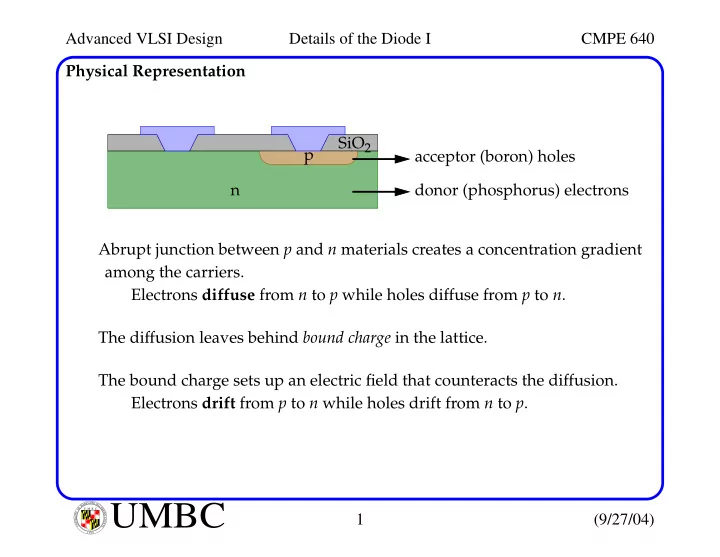

Advanced VLSI Design Details of the Diode I CMPE 640 Physical Representation SiO 2 p acceptor (boron) holes n donor (phosphorus) electrons Abrupt junction between p and n materials creates a concentration gradient among the carriers.

Advanced VLSI Design Details of the Diode I CMPE 640 Physical Representation SiO 2 p acceptor (boron) holes n donor (phosphorus) electrons Abrupt junction between p and n materials creates a concentration gradient among the carriers. Electrons diffuse from n to p while holes diffuse from p to n . The diffusion leaves behind bound charge in the lattice. The bound charge sets up an electric field that counteracts the diffusion. Electrons drift from p to n while holes drift from n to p . L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 Charge Distribution, Electric Field and Electrostatic Potential Hole diffusion Electron diffusion - - + + p n plate - plate + neutral region - - neutral region + + Electron drift p region more heavily Hole drift doped, N A >N D + Charge Density Distance - Electric Field Distance Potential φ 0 Distance L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 Built-In Potential and I-V Characteristics Build-in potential: NAND kT where φ T φ 0 φ T ln = - - - - - - = 26mV at 300K (Thermal V) = - - - - - - - - - - - - - - - - - - q 2 10 carriers/cm3 ni × 10 ni = 1.5 For example: 10151016 1015carriers/cm3 NA = φ 0 = 26 ln - - - - - - - - - - - - - - - - - - - - - - - - - - = 638 mV 20 × 10 1016carriers/cm3 2.25 ND = Forward bias: Raising potential of the p w.r.t n causes current to flow from p to n . Lowers potential barrier and diffusion dominates drift . Minority carriers injected into neutral region and diffuse toward plates. Recombine with majority carrier causing a net flow of current. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 I-V Characteristics Reverse bias: Raising potential of the n w.r.t p causes current to fl ow fr om n to p . Drift dominates diffusion . However, current is small since the number of minority carriers (e.g., electrons in p neutral region) is small. For forward bias, the current is exponentially related to applied bias. Small deviation 1.5 10 0 due to recombination I D (mA) in depletion region. 1.0 I D (A) 10 -5 0.5 2.3 φ T V/decade 10 -10 10 -15 1.0 0.5 V D 0.0 0.2 0.4 0.6 0.8 V D Linear scale Log scale Current increases by a factor of 10 for every 60mV (2.3 φ T ) of forward bias. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 Static Behavior Ideal diode equation: VD φ T ⁄ where I S is a constant: saturation current. ID = IS e – 1 With V D << 0, I D ~= -I S = 10 -17 A/um 2 (actual values are 10 3 higher) Forward Bias: Physical basis for ideal equation: Minority carrier concentration Metal contact to p region Metal contact to n region p n (x) p n (W 2 ) p n0 n p (x) n p0 p-region -W 1 0 x W 2 n-region W n -W p L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 Static Behavior Reverse Bias: Ideal diode equation predicts diode current approaches the saturation current as V D gets much smaller than the thermal voltage. → φ T I D – I S V D » for Concentration of minority carriers at depletion-region approaches 0 under sufficient reverse bias. Minority carrier concentration Metal contact to p region Metal contact to n region p n0 n p0 p n (x) n p (x) p-region -W 1 0 W 2 n-region W n x -W p L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 Static Behavior Simple models of the diode. Left model based on ideal diode but is strongly non-linear and approxi- mated by a simple model on the right. VD φ T ⁄ + + I D ID = IS e – 1 V D + V D V Don - First order approx. - - Ideal diode model For a fully conducting diode, voltage drop across diode is ~0.7V Example: Assume V S = 3V and R S = 10k Ω and I S = 0.5X10 -16. I D Using non-linear model yields: V D R S V D =0.757V and I D =0.224mA + V S - Assuming V D =0.7V yields I D =0.23mA L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 Dynamic Behavior Dynamic behavior determines the maximum operational frequency. It is dependent on how fast charge can be moved around. Two capacitances : Depletion and diffusion . Depletion region and Junction capacitance: Under the ideal model, the depletion region is void of mobile carriers. Its charge is determined by the immobile donor and acceptor ions. Intuitively: Forward bias : Potential barrier is reduced which means that less space charge is needed to produce the potential difference. This corresponds to a reduced depletion-region width. Reverse bias : Potential barrier increased, increase in space charge, wider depletion width. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 Dynamic Behavior Expressions that convey this fact. • Depletion region charge (V D is positive for forward bias): φ 0 N A N D A D 2 ε si q ( ) - - - - - - - - - - - - - - - - - - - - - - - Q j = – V D (1) N A + N D • Depletion-region width : 2 ε si φ 0 N A + N D (2) ( ) W j = W 2 – W 1 = - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - – V D q N A N D • Maximum electric field : where φ 0 N A N D 2 q – 12 ( ) ε si × × 10 - - - - - - - - - - - - - - - - - - - - - - - - - - - - - E j = – V D = 11.7 1.053 F/cm ε si N A + N D The ratio of the n-side versus p-side depletion region width is determined by the doping level ratios: W 2 N A - - - - - - - - - - - - - - - - = - - - - - - - - ( ) – W 1 N D L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 Dynamic Behavior The model (for an abrupt junction): Imagine the depletion region as the dielectric of a capacitor with dielec- tric constant of silicon. And the n- and p-neutral regions act as the capacitor plates: - - + + p n plate plate - + neutral region - - neutral region + + insulator Forward bias, cap increases Reverse bias, cap decreases A small change in the voltage applied to the junction (dV D ) causes a change in the space charge (dQ j ). L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 Dynamic Behavior Depletion layer capacitance: Junction capacitance is easily computed by taking the derivative of equa- tion (1) with respect to V D . For an abrupt junction: ε si q dQ j N A N D C j 0 ) 1 – - φ 0 ( C j = - - - - - - - - - - - = A D - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - – V D = - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - V D φ 0 ⁄ dV D 2 N A + N D 1 – C j0 is the capacitance under zero-bias conditions and is only a function of the physical parameters of the device: ε si q N A N D – 1 - φ 0 ( ) C j 0 = A D - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 2 N A + N D The same result can be obtained using the standard parallel-plate capac- itor equation: A D ε si where W j is given by equation (2). - - - - - - - - C j = W j L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 11 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the Diode I CMPE 640 Dynamic Behavior Junction capacitance plotted as a function of applied voltage bias: 2.0 Strongly non-linear Abrupt junction m = 0.5 C j (fF)/um 2 1.5 Linear junction 1.0 m = 0.33 0.5 C j0 0.0 -4.0 -2.0 0.0 V D Capacitance decreases with an increasing reverse bias. For -5V, the cap. is reduced by more than a factor of 2 over the zero bias case.: – 3 F/ m 2 × 10 = 2 C j 0 0.5 um 2 then a reverse bias of -2.5V yields AD = 0.9 fF um 2 ) 0.5 um 2 φ 0 ( ⁄ ( ) = 0.64 V = 0.45 fF L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 12 (9/27/04) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![1 Mor M. Peretz, Switch-Mode Power Supplies [5-4] Transistor turn off - parasitics L main](https://c.sambuz.com/1020425/1-s.webp)