1

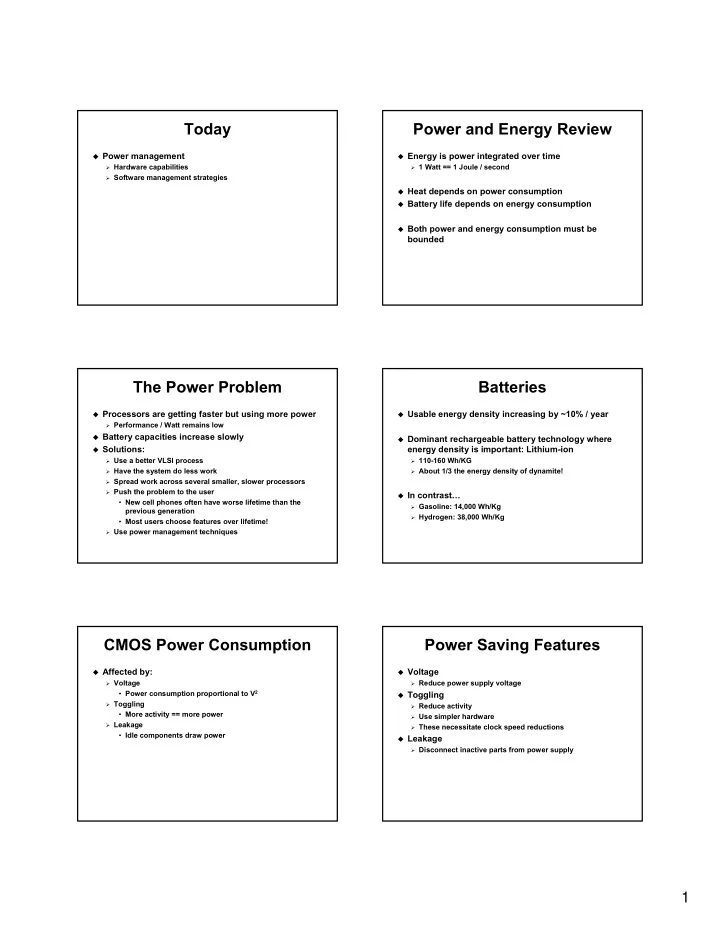

Today

Power management

Hardware capabilities Software management strategies

Power and Energy Review

Energy is power integrated over time

1 Watt == 1 Joule / second

Heat depends on power consumption Battery life depends on energy consumption Both power and energy consumption must be

bounded

The Power Problem

Processors are getting faster but using more power

Performance / Watt remains low

Battery capacities increase slowly Solutions:

Use a better VLSI process Have the system do less work Spread work across several smaller, slower processors Push the problem to the user

- New cell phones often have worse lifetime than the

previous generation

- Most users choose features over lifetime!

Use power management techniques

Batteries

Usable energy density increasing by ~10% / year Dominant rechargeable battery technology where

energy density is important: Lithium-ion

110-160 Wh/KG About 1/3 the energy density of dynamite!

In contrast…

Gasoline: 14,000 Wh/Kg Hydrogen: 38,000 Wh/Kg

CMOS Power Consumption

Affected by:

Voltage

- Power consumption proportional to V2

Toggling

- More activity == more power

Leakage

- Idle components draw power

Power Saving Features

Voltage

Reduce power supply voltage

Toggling

Reduce activity Use simpler hardware These necessitate clock speed reductions

Leakage

Disconnect inactive parts from power supply