Synchronous logical networks I Digital Systems M 1 Asynchronous - PowerPoint PPT Presentation

Synchronous logical networks I Digital Systems M 1 Asynchronous network problems The behaviour depends on the feedback delays with all related possible malfunctionings (different delays) The behaviour depends on the input hazards (which

Synchronous logical networks I Digital Systems M 1

Asynchronous network problems • The behaviour depends on the feedback delays with all related possible malfunctionings (different delays) • The behaviour depends on the input hazards (which in any case can’t be exactly concurrent) and prevents the detection of repeated input sequences (i.e. the sequence 00-00-11-01 is the same as 00-11-01) SOLUTION • An «artificial» input concurrency detection and forced and controlled feedback delays 2

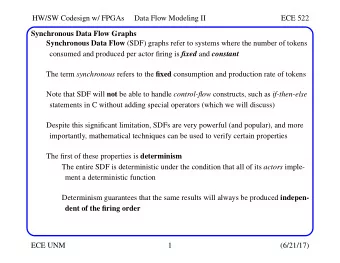

Synchronism signal Z 0..m X 0..n Combinatorial Y 0..k s/r 0..k network FF SR 0..k τ Synchronism signal • If the pulse is short enough and less than the combinatorial network delay (that is the combinatorial network minimum delay) the new s/r 0..k produced by the combinatorial network do not reach the blocking AND before the AND outputs are zeroed making the SR FF stable ( the SR FF with both inputs zero doesn’t change status) . Only during the following τ pulse the new FF outputs values are transmitted to the combinatorial network with no feedabck effets again. Forced feedback alignment. • It must be noticed that this way the combinatorial networks inputs too are forcibly «aligned» as far as the status is concerned. No «race» problems (but for the output in the Mealy case) • The outputs are almost perfectly aligned (that is they are synchronous) if the sequential machine is Moore type (the outputs depend only from the state variables) and the FFs switch concurrently (which is very likely) 3

Synchronism signal • The synchronism signal is always referred to as clock • Normally the clock signal is a regular repetitive square (or rectangular) wave of T period (but not necessarily) T Clock • A SR FF with a clock signal is referred to as synchronous SR (which in the real systems is never used) • What problems arise with the clock signal of the figure ? The pulse duration should be extremely narrow since a combinatorial network can consist even of a single wire and in this case the delay is only the wire propagation delay! In practice it cannot be implemented 4

The synchronous FFs • There are several synchronous FFs but nowadays only the DFF is used whose behaviour was previously analysed as an asynchronous network but which here is used as a synchronous FF (in its 74xx74 version) D Q D !Q CK • The DFF has this name name because D stands for Delay. In fact the output Q follows the input D with a T period delay (if the input signal is synchronous – that is is generated concurrently with the clock – respecting however setup and hold times – for instance by a network controlled by other DFFs using the same clock) or in presence of the first clock rising edge. • The triangle on the clock input (CK) indicates that the FF is edge triggered that is it switches on the positive edge of the clock The signals !CL(ear) and !PR(eset) D PR Q act asynchronously that is D !Q immediately, independently from the CK CL clock 5

The DFF switches ONLY during the transition of CK fro 0 o 1. This corresponds to the very short pulse τ seen before. If the transition is fast enough the combinatorial network cannot react before the CK transition is finished Z 0..m X 0..n Combinatorial Y 0..k y 0..k network D 0..k D 0..k Q 0..k Q 0..k CK CK Clock FFD 0..k The clock of the DFF must switch from 0 to 1 only when the combinatorial network is stable (quiet). The transfer of the DFF input to its outputs (transition time) must fast enough to grant the the new D inputs generated by the combinatorial network because of the new values of Y i arrive after the end of the CK transition. Then there is a solid time period for the combinatorial network to reach a new stable state. The period of the CK must be in any case greater than the time required by the combinatorial network to reach its stable state. 6

Let’s consider the DFF D Q D Q DFF Q* QN CK CK CK D Q 7

entity DFF_1 is Port ( D : in std_logic ; CK : in std_logic ; Q : out std_logic; QN : out std_logic ); end DFF_1; architecture Behavioral of DFF_1 is begin process_FF: process(CK,D) begin if (CK'event) and (CK='1') then Q <= D; QN <= not(D); -- Careful! QN <= not(Q) must not be used !!!!!! -- otherwise QN switch would not be concurrent with Q end if; end process process_FF; end Behavioral; “if (CK'event) and (CK='1')” means that the switch occurs in presence of an edge of CK and the final value is 1 (CK=1). Rising edge ! 8

DFF with Set and Reset (VHDL) A_SET A_SET D D Q Q DFF Q* QN CK CK A_RES A_RES Asynchronous commands A_SET and A_RES have precedence over the other inputs • The two signals must not be activated concurrently (nonsense) • In our case we want to model the DFF so as A_RES has precedence over A_SET • 9

entity DFF_asynchronous_commands is Port ( CK : in std_logic; D : in std_logic; A_SET : in std_logic; A_RES : in std_logic; Q : out std_logic; QN : out std_logic); end DFF_asynchronous_commands; architecture Behavioral of DFF_asynchronous_commands is begin Process_FF: process(CK, A_SET, A_RES, D) begin -- positive logice if (A_RES='1') then Q <='0'; QN <='1'; elsif (A_SET = '1') then -- only if A_RES inactive Q <='1'; QN <='0'; elsif (CK='1') and (CK'event) then Q <= D; QN <= not(D); end if; end process process_FF; end Behavioral; 10

Both asynchronous Asynchronous Asynchronous commands active Reset Set (A_RES=1, A_SET=1): (A_RES=1, (A_RES=0, asynchronous reset has A_SET=0) A_SET=1) higher priority (see VHDL) Positive logic ! 11

In Vivado the DFF (as other basic components can be found as ready_to_use elements. In tools=>language templates it is possible to find it. Each template depends on the type of the used device (artix in this example) 12

VHDL source ------------------------------------------------------------------------------ ---- -- FDCE : In order to incorporate this function into the design, -- VHDL : the following instance declaration needs to be placed -- instance : in the architecture body of the design code. The -- declaration : instance name (FDCE_inst) and/or the port declarations -- code : after the "=>" assignment maybe changed to properly -- : connect this function to the design. All inputs must be -- : connected. -- Library : In addition to adding the instance declaration, a use -- declaration : statement for the UNISIM.vcomponents library needs to be -- for : added before the entity declaration. This library -- Xilinx : contains the component declarations for all Xilinx -- primitives : primitives and points to the models that will be used -- : for simulation. library IEEE; use IEEE.STD_LOGIC_1164.ALL; 13

-- NB If you want to use the VHDL functions as FDCE you must use UNISIM library UNISIM; use UNISIM.VComponents.all; entity Source is Port ( Q: out std_logic; C: in std_logic; CE: in std_logic; CLR: in std_logic; D: in std_logic ); end Source; -- FDCE: Single Data Rate D Flip-Flop with Asynchronous Clear and -- Clock Enable (posedge clk). -- Artix-7 -- Xilinx HDL Language Template, version 2016.4 architecture Behavioral of Source is begin FDCE_inst : FDCE generic map ( INIT => '0') -- Initial value of register ('0' or '1') port map ( Q => Q, -- Data output C => C, -- Clock input CE => CE, -- Clock enable input CLR => CLR, -- Asynchronous clear input D => D -- Data input ); end behavioral; 14

VHDL test library IEEE; use IEEE.STD_LOGIC_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values --use IEEE.NUMERIC_STD.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx leaf cells in this code library UNISIM; use UNISIM.VComponents.all; entity Test is end Test; architecture Behavioral of Test is component source Port ( Q: out std_logic; C: in std_logic; CE: in std_logic; CLR: in std_logic; D: in std_logic ); end component; signal Q: std_logic := '0'; signal C: std_logic := '0'; signal CE: std_logic := '0'; signal CLR: std_logic := '0'; signal D: std_logic := '0'; 15

begin uut: Source PORT MAP ( D => D, C => C, Q => Q, CE => CE, CLR => CLR ); stim_proc: process begin wait for 20 ns; D <= '1'; CE <= '1'; wait for 20 ns; C <= '1'; wait; end process; end Behavioral; 16

VHDL behavioural simulation 17

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![h ( t ) h [ n ] x ( t ) y ( t ) x [ n ] y [ n ] Examples System : a process in which input](https://c.sambuz.com/1014128/h-t-h-n-s.webp)