Summary Summary I Iterative flow Iterative flow vs vs. stepwise - PDF document

Gain Gain-based synthesis based synthesis enabler for correct enabler for correct-by by-construction design construction design Patrick Patrick Groeneveld Groeneveld (patrick patrick@magma @magma-da da.com) .com) Magma

Gain Gain-based synthesis based synthesis enabler for ‘correct enabler for ‘correct-by by-construction’ design construction’ design Patrick Patrick Groeneveld Groeneveld (patrick patrick@magma @magma-da da.com) .com) Magma Design Automation Magma Design Automation Cupertino, CA Cupertino, CA Patrick Groeneveld DAC'2000 1 Summary Summary I Iterative flow Iterative flow vs vs. stepwise refinement . stepwise refinement I Derivation of a simple delay model Derivation of a simple delay model I Gain based delay optimization Gain based delay optimization I Building a tool flow around this model Building a tool flow around this model I Standard cell library issues Standard cell library issues I Getting timing during routing Getting timing during routing I Recommendations Recommendations I latest slides at http:// latest slides at http://cas cas.et. .et.tudelft tudelft.nl nl/~ /~patrick patrick/closure /closure Patrick Groeneveld DAC'2000 2

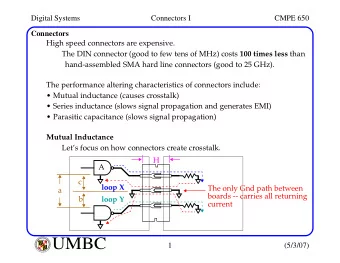

Preliminaries Preliminaries I Timing closure: Obtaining a feasible layout of a circuit Timing closure: Obtaining a feasible layout of a circuit that meets the given timing specification. that meets the given timing specification. I Objective: Obtain closure as fast and effortless as Objective: Obtain closure as fast and effortless as possible. possible. I Assumptions: Assumptions: N ASIC design style. ASIC design style. N Standard cell abstraction. Standard cell abstraction. N Static CMOS. Static CMOS. I Neglect other design issues Neglect other design issues 3 Patrick Groeneveld DAC'2000 Interconnect parasitics Interconnect parasitics (C and R) (C and R) I Speed is entirely determined by Speed is entirely determined by parasitics parasitics I Parasitics Parasitics are tiny are tiny I Parasitics Parasitics depend on the depend on the exact exact layout layout I Therefore they are hard or impossible to estimate, Therefore they are hard or impossible to estimate, especially before placement. especially before placement. Patrick Groeneveld DAC'2000 4

Timing Uncertainty Timing Uncertainty Gate Gate-to to-gate delay depends on: gate delay depends on: • Wire length (unknown during synthesis) Wire length (unknown during synthesis) • The layer of the wire (determined during routing) The layer of the wire (determined during routing) • The configuration of the neighboring wires: The configuration of the neighboring wires: distance, near/far (unknown before detailed routing) distance, near/far (unknown before detailed routing) • Timing window and slope of the neighboring wires. Timing window and slope of the neighboring wires. 5 Patrick Groeneveld DAC'2000 Meeting timing gets harder Meeting timing gets harder q Flip Flip Flip Flip d flop flop q flop flop q Flip Flip d Flip Flip flop flop flop flop q q Flip Flip flop flop q 5 5 ns ns max max Patrick Groeneveld DAC'2000 6

Timing is a result of the placement Timing is a result of the placement I The bad news: the worst timing sets the clock speed! The bad news: the worst timing sets the clock speed! s slack C dream C real slack 7 Patrick Groeneveld DAC'2000 Prediction vs reality Prediction vs reality circuit does circuit does not work not work number of number of nets nets -100% 100% +100% +100% fastest/best fastest/best slowest/worst slowest/worst Average, Average, wireload model, wireload model, what you what you designed for designed for Real delay - predicted delay Real delay predicted delay Patrick Groeneveld DAC'2000 8

The end of the wire load model The end of the wire load model I Model is used in Model is used in coventional coventional synthesis tools synthesis tools I It guesses load based on the number of pins of the It guesses load based on the number of pins of the net net I The average is correct but... The average is correct but... 9 Patrick Groeneveld DAC'2000 Today’s Conventional Flow Today’s Conventional Flow RTL I Synthesis does not Synthesis does not Logic Synthesis Logic Synthesis accurately model accurately model interconnect interconnect Placement I Cell sizes fixed before Cell sizes fixed before placement. placement. Multiple Routing I Place & route unable Place & route unable iterations to meet timing goal to meet timing goal Extraction Timing Analysis Met You must iterate! You must iterate! timing? NO GDSII Patrick Groeneveld DAC'2000 10

The trial and error iteration The trial and error iteration logic synthesis place & route 11 Patrick Groeneveld DAC'2000 Methodology Problems Methodology Problems I To avoid endless iterations, the design must be ‘on To avoid endless iterations, the design must be ‘on the safe side’ the safe side’ I Iterations are very slow and may not converge Iterations are very slow and may not converge I You’re never sure if you’ll make it You’re never sure if you’ll make it I Only a painful trial and error process reports design Only a painful trial and error process reports design feasibility. feasibility. Patrick Groeneveld DAC'2000 12

Ways to attack timing closure Ways to attack timing closure I Iterate through SPEF or internally Iterate through SPEF or internally I Post Post-placement optimization (ECO) placement optimization (ECO) I Partition the design into smaller pieces Partition the design into smaller pieces N Variation in wire length will decrease Variation in wire length will decrease N Better timing closure on each block if #gates < 50,000 Better timing closure on each block if #gates < 50,000 I Gain Gain-based synthesis based synthesis 13 Patrick Groeneveld DAC'2000 Hierarchy Hierarchy I Make problems smaller Make problems smaller I Structure makes the problem Structure makes the problem better manageable better manageable I Solve sub Solve sub-problems problems independently independently I Enables efficient re Enables efficient re-use use I Enables consistent verification Enables consistent verification Patrick Groeneveld DAC'2000 14

Physical hierarchy and timing closure Physical hierarchy and timing closure I Wires need to slalom around blocks or traverse Wires need to slalom around blocks or traverse through or over blocks through or over blocks I How to set pin locations? How to set pin locations? I Where to put the buffers? Where to put the buffers? I Automatic floor planning problem is unsolved Automatic floor planning problem is unsolved I Large hidden inefficiency Large hidden inefficiency 15 Patrick Groeneveld DAC'2000 Physical hierarchy is a necessary evil Physical hierarchy is a necessary evil macro macro 2,000,000 2,000,000 20 x approx 20 x approx. 100,000 . 100,000 standard cells flat? standard cells flat? standard cells standard cells I If you can do it, do it as flat If you can do it, do it as flat macro as possible! as possible! 4 blocks of 500,000 4 blocks of 500,000 I Also do Also do datapath datapath flat flat standard cells? standard cells? Patrick Groeneveld DAC'2000 16

Conventional layout synthesis Conventional layout synthesis s slack C dream C real slack 17 Patrick Groeneveld DAC'2000 Gain- -based synthesis: based synthesis: Gain s slack C dream C real Patrick Groeneveld DAC'2000 18

Focus for timing closure Focus for timing closure I Combine logical and physical worlds. Combine logical and physical worlds. I Crisp: focus on the main effect, skip irrelevant details Crisp: focus on the main effect, skip irrelevant details I Enable blazingly fast optimization Enable blazingly fast optimization I Compact: Memory efficient for tomorrow’s 50M gate chip Compact: Memory efficient for tomorrow’s 50M gate chip 19 Patrick Groeneveld DAC'2000 Good practices, bad practices Good practices, bad practices Use a simple model, and adapt reality to it. Use a simple model, and adapt reality to it. I At each step, freeze a single constraint, postpone decisions on At each step, freeze a single constraint, postpone decisions on others. others. I Allow sufficient freedom in future steps to fulfill all remainin Allow sufficient freedom in future steps to fulfill all remaining g I constraints. constraints. Bail out early if there’s no use continuing Bail out early if there’s no use continuing I Fix multiple objectives at once. Fix multiple objectives at once. I Iterate. Iterate. I Indulge in ‘accurate’ models Indulge in ‘accurate’ models I Attempt to be optimal Attempt to be optimal I Patrick Groeneveld DAC'2000 20

Is ‘Optimal’ optimal?? Is ‘Optimal’ optimal?? Contacts in layout have Contacts in layout have parasitic resistance and parasitic resistance and affect reliability affect reliability 8 contacts 8 contacts Optimal Optimal with contact minimization: with contact minimization: 0 contacts 0 contacts There are still 8 contacts! There are still 8 contacts! 21 Patrick Groeneveld DAC'2000 Compromises Compromises I Flexible Flexible-die design is better: die design is better: N Guarantee routing completion Guarantee routing completion N Until the last moment we can trade Until the last moment we can trade-off delay for area. off delay for area. I Fixed Fixed-die design instead die design instead N Need to guess initial utilization. Need to guess initial utilization. I This could result in an iteration. This could result in an iteration. Patrick Groeneveld DAC'2000 22

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.