Signal Integrity Simulation and Equivalent Circuit Modeling - PowerPoint PPT Presentation

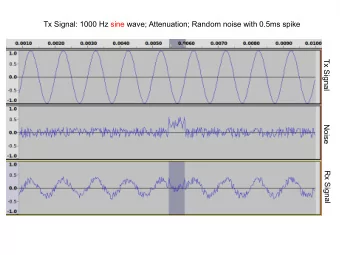

NTU Signal Integrity Simulation and Equivalent Circuit Modeling Tzong-Lin Wu Department of Electrical Engineering National Taiwan University Taipei, Taiwan wtl@cc.ee.ntu.edu.tw Outline NTU Introduction Signal Integrity Simulation in

NTU Signal Integrity Simulation and Equivalent Circuit Modeling Tzong-Lin Wu Department of Electrical Engineering National Taiwan University Taipei, Taiwan wtl@cc.ee.ntu.edu.tw

Outline NTU � Introduction � Signal Integrity Simulation in SPICE A case Study: Driver Board of TFT Display Panel � TDR Concept and Layer Peeling Technique (one port) � Macro-model Synthesis for Coupled Discontinuities of Signal Path (two-port) � Challenge of SI Modeling for Real PCB and Package � Summary

Introduction NTU � With rapidly increased clock rate and denser interconnect layout, noise caused by the discontinuities can be a critical factor to degrade the signal integrity (SI) of circuit systems. 0.025 � Example: Via coupling 0.02 0.015 V ) t l Signal rising time o step v 100ps ( 0.01 50ps T Coupling D 20ps T 10ps V V 0.005 TDT 0 -0.005 0 2E-011 4E-011 6E-011 8E-011 1E-010 1.2E-010 t (s) 3

Introduction NTU Extracting SPICE-compatible models for those discontinuities are essential. Benefits: 1. More convenient integration with chip circuits under SPICE environment. 2. Better accuracy with higher order of equivalent circuits. GND Power 4

Time Controller (T-CON) Case Study: Driver Board of TFT Display Driver IC Driver PCB NTU

Case Study: Driver Board of TFT Display NTU � Objectives of this project: � Signal integrity modeling for the driver PCB and compare with the measured results. � Approaches: � Establishing SPICE-compatible model for all interconnects and doing SI simulation on HSPICE. � IC I/O Buffer Model � SPICE model � IBIS model

Case Study: Driver Board of TFT Display NTU -- HSPICE Approach Step 1: Trace all interconnects from driver (T-CON) to receiver (driver IC) Differential line TCON (with GND) via1 Differential line (no GND) via3 via3 via2 FPC FPC FPC Driver IC Driver IC Driver IC

Case Study: Driver Board of TFT Display NTU -- HSPICE Approach Step 2: Extract SPICE Compatible models for each partitioned interconnects by Ansoft Q3D (Differential signals) Differential line (no GND) Differential line (with GND) GND

Case Study: Driver Board of TFT Display NTU -- HSPICE Approach Step 2: Extract SPICE Compatible models for each partitioned interconnects by Ansoft Q3D (Differential Via Holes) Differential line TCON via1. via2. (with GND) via1 Differential line (no GND) via3 via3 via2 FPC FPC FPC Driver IC Driver IC Driver IC

Case Study: Driver Board of TFT Display -- HSPICE Approach NTU Via Macro-model (type 1) 3 4 1 via1. 2 3 1 2 4

Case Study: Driver Board of TFT Display -- HSPICE Approach NTU Via Macro-model (type 2) via2.

Case Study: Driver Board of TFT Display -- HSPICE Approach NTU Step 2: Extract SPICE Compatible models for each partitioned interconnects by Ansoft Q3D (Flexible PCB) Differential line TCON (with GND) via1 Differential line (no GND) via3 via3 via2 FPC FPC FPC Driver IC Driver IC Driver IC

Case Study: Driver Board of TFT Display -- HSPICE Approach NTU Differential • Line pitch : 0.028mm • Substrate : polyimide ( ε r 3.5) line • Thickness : 0.038mm Substrate : polyimide

Case Study: Driver Board of TFT Display -- HSPICE Approach NTU Step 4: Comparison between modeling and measurement Case1 : Open circuit for the receiver side (Driver IC) Using SPICE and IBIS models for transmitted side (T-CON) TCON Differential line Measuring Probes (IBIS . spice) TCON (with GND) via1 Differential line (no GND) via2 via3 via2 via3 100 Ω 軟板 軟板 軟板 軟板 open open open open

Case Study: Driver Board of TFT Display -- HSPICE Approach NTU Step 4: Comparison between modeling and measurement Case1 : Open circuit for the receiver side (Driver IC) Using SPICE and IBIS models for transmitted side (T-CON) 0.2 0.15 0.1 0.05 0 -0.05 -0.1 -0.15 Spice IBIS -0.2 measurement

Case Study: Driver Board of TFT Display -- HSPICE Approach NTU Step 4: Comparison between modeling and measurement Case2 : Using IBIS model for the receiver side (Driver IC) Using SPICE and IBIS models for transmitted side (T-CON) TCON Differential line 訊號觀測點 (IBIS . spice) TCON (with GND) via1 Differential line (no GND) 100 Ω via2 via3 via2 via3 軟板 軟板 軟板 軟板 Driver IC Driver IC Driver Driver Driver Driver (IBIS) (IBIS) (IBIS) (IBIS)

Case Study: Driver Board of TFT Display -- HSPICE Approach NTU Step 4: Comparison between modeling and measurement Case2 : Using IBIS model for the receiver side (Driver IC) Using SPICE and IBIS models for transmitted side (T-CON)

Outline NTU � Introduction � Signal Integrity Simulation in SPICE A case Study: Driver Board of TFT Display Panel � TDR Concept and Layer Peeling Technique (one port) � Macro-model Synthesis for Coupled Discontinuities of Signal Path (two-port) � Challenge of SI Modeling for Real PCB and Package � Summary

TDR basic theory NTU V V step r Coaxial cable Time-Domain DUT Reflectometry (TDR) V TDR = + V V V T DR st e p r ( ) ( ) = + = + Γ ⋅ Γ = − + V V V (1 ) V Z Z / Z Z TDR step r step L 0 L 0 Γ = open circuit 1 2 V step 2 d cable t Γ = load circuit 0 V step 19 short circuit Γ = − 1 0

TDR theory NTU V V step r Coaxial cable Time-Domain DUT Reflectometry (TDR) V TDR = + V V V T DR st e p r V step Z Z 0 0 capacitive dip 0 C V Z Z step 0 0 inductive peak L 20 2005/6/18 0

21 TDR theory Fig. Source: HP TDR NTU

Layer Peeling Technique (LPT) NTU ( ) V t Z ( ) Z Z I t Z Z + s 1 2 i 1 i T T T T d d d d x x x x x + V ( ) t 2 3 1 i i 1 in a − a + a − i j , 1, j i j , b + b − b − i j , i j , 1, j − + = + a a a + + i j , 1 i 1, j i j , ( ) ( ) + − − b + + + = + − − ⎡ ⎤ ⎡ ⎤ + Z a b Z a b − − + + − Γ = b − ⎡ ⎤ i j , 1 Z Z − a a ( ) 1 i 1 i i 1 i i i b b Γ ≡ = − i ,1 i j , = − Γ i j , i i 1 + + ⎢ ⎥ ⎢ ⎥ i 2 Z i 1, j i j , 1 ⎢ ⎥ 1 2 ( ) ( ) 1 1 − + 1 i Z Z − − − Γ + + − = − + i − Z Z a ⎢ ⎥ ⎣ ⎦ ⎢ ⎥ a b a 1 b 0 b 2 b ⎣ ⎦ ⎣ ⎦ − i i i i i i 1 i ,1 i i j , i j , Z Z − ← Δ → i 1 i X X X X 22 1 2 3

Begin Layer Peeling Technique (LPT) NTU = = Z 50, i 1 0 − = − a a V ⇒ 1, j 1 TDR − = − V b b in 1, j 1 − + Γ b 1 Γ = = i ,1 i Z Z − − − Γ i i i 1 1 a i ,1 i ( ) V t Z ( ) I t Z Z Z Z + s 1 2 1 i i T T T T ⎡ + ⎤ ⎡ − ⎤ − Γ d − ⎡ ⎤ d d d a a x x ( ) 1 1 x x x + V ( ) t i j , = − Γ i j , ⎢ ⎥ i ⎢ ⎥ 1 2 3 2 i i 1 1 2 ⎢ ⎥ in − Γ + i − ⎣ ⎦ ⎢ ⎥ 1 ⎢ ⎥ a − b b ⎣ ⎦ ⎣ ⎦ a + a − i i j , i j , i j , 1, j i j , i=i+1 b + b − b − i j , i j , 1, j = − − = + � + a a j 1,2,3, , N i a + i 1, j i j , + i j , 1 + = − − = + � b j 1,2,3, , N i b b + + + i 1, j i j , 1 i j , 1 Z 1 Z Z 0 2 i=N? ← Δ → X X X X 23 2005/6/18 1 2 3 End

Layer Peeling Technique (LPT) NTU V TDR 100 ohm 110 100 0.3 90 ) m h 0.25 80 O 70 ohm VTDR (volt) ( e c 70 n 0.2 a d 60 50 ohm e p m 50 0.15 40 ohm I e n 40 i L 0.1 30 20 0.05 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 24 2005/6/18 t (ns) t (ns)

Outline NTU � Introduction � Signal Integrity Simulation in SPICE A case Study: Driver Board of TFT Display Panel � TDR Concept and Layer Peeling Technique (one port) � Macro-model Synthesis for Coupled Discontinuities of Signal Path (two-port) � Challenge of SI Modeling for Real PCB and Package � Summary

26 shorting vias Broadband Macro-Models of Differential Via Differential via IC IC Through-hole via 2005/6/18 G G S S NTU

Broadband Macro-Models of Differential Via NTU trace1 trace2 V TDR V Anti-Pad TDT Terminatted traces Via-Pad trace3 trace4 V Z Z TDR Port 1 0 0 M V 1 = step R Z L 0 M V 3 TDT Port 2 M 2 27 R L

Step responses and macro-PI model NTU Step response : : incident wave a b : reflected wave i b = m y ( ) t n :stimulative port mn i a m : detected port n y :step response mn Pencil of matrix method i r : residues mn L ∑ mn = − i p : poles i i y ( ) t r exp( p t ) mn mn mn mn = L : mode numbers i 1 mn 28

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.