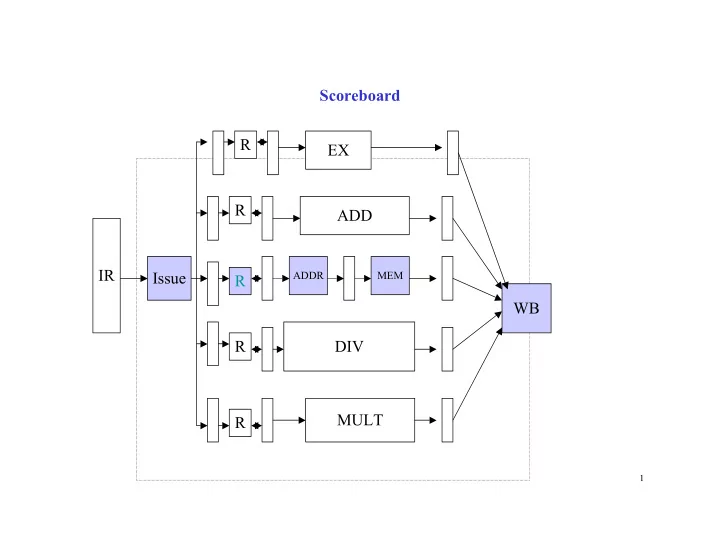

Scoreboard R EX R ADD IR Issue ADDR MEM R WB R DIV MULT - PowerPoint PPT Presentation

Scoreboard R EX R ADD IR Issue ADDR MEM R WB R DIV MULT R 1 1 Scoreboard Algorithm and Implementation Concentrate on Data Hazards only Array REGBusy[ ] one for each register Set to TRUE when an instruction that has that

Scoreboard R EX R ADD IR Issue ADDR MEM R WB R DIV MULT R 1 1

Scoreboard Algorithm and Implementation Concentrate on Data Hazards only Array REGBusy[ ] one for each register • Set to TRUE when an instruction that has that register as destination is issued. Set • to FALSE when the instruction is done and writes result in destination register. Issue Stage: Check instruction in Instruction register; either stall or issue into ISSUE Register Assuming Issue Register is not occupied Assuming Issue Register is not occupied Let f be the id of the FU needed by instruction in IR and d its destination register: if ( REGBusy[ d ] == FALSE ) Issue instruction to Issue Register of FU f; else Stall. if (Issued) Set REGBusy[ d ] to TRUE ; Update Data Flow Graph. 2

Scoreboard Algorithm and Implementation Update Data Flow Graph Maintains dependency information between instructions Instruction I is being issued Assume that I reads source registers S, T and writes destination D 1. Draw an arrow from instruction I to register D 2. Draw either a red or a green arrow from register S to instruction I. If there is no incoming arrow to S: color outgoing arrow green /* no in-flight writer */ else color it red /* in flight writer */ 3. Do the same from register T to instruction I. 3

Example Problem of distinguishing a RAW dependency from a WAR dependency A: DIV.D F0, F2, F4 A: MUL.D F6, F0, F8 B: MUL.D F6, F0, F8 B: DIV.D F0, F2, F4 A F0 F0 Issue A Issue A A A B F0 F0 Issue B Issue B A B 4 B must wait till A writes B must wait till A reads

Scoreboard Algorithm Dispatch stage: Array of flags FUBusy[ ] one for each functional unit. • • Set to TRUE when an instruction is issued to the FU. Cleared when instruction is done. For each instruction I in an Issue Register (Assume I reads registers S and T, and writes D) • If the arrow from S to I and the arrow from T to I are both green • Read registers S and T • Remove arrows from S to I and T to I • Dispatch to FU and set FUBusy[f] to TRUE 5

Scoreboard Algorithm Write stage: From among the completed instructions in EX/WB pipeline registers • • Select instruction I that is SAFE-TO-WRITE (I uses FU f and writes to register d) SAFE-TO-WRITE register d is TRUE • if there are no earlier instructions still wanting to read d SAFE-TO-WRITE if there are no green arrows out of register d • • Write result to register d • Remove arrow from I to d • Change all outgoing arrows from d to green • FUBusy[f] = FALSE; REGBusy[D] = FALSE; 6

Scoreboard Algorithm Notes: An arrow from I to d means instruction I will write register d in the future. • Since no WAW dependent instructions are issued there will be at most one arrow • into a register at any time. In an actual implementation the ID of I is not needed; merely the fact there is a • current writer is sufficient. (Set REGBusy[d] = TRUE) A green arrow from S to I means that I wants to read the current value of register S. • The green informs other instructions not to write to S till I reads it. • A writer will wait till the arrow is removed to avoid a WAR hazard. • A red arrow means that I is waiting for the value that the current writer of register S • will produce. I will wait till the arrow becomes green to avoid a RAW hazard. • When the writer updates S it therefore makes every arrow outgoing from S to • green. 7

Dataflow graph maintained by the Scoreboard An instruction I is identified by the FU it is using • Writer information (in coming arrows) recorded in bit array • REGBusy[Number of Registers] Reader information maintained in a 2-d bit array • DATAFLOW [Number of Registers] [Number of FUs ] DATAFLOW[i][j] = 00 if • • REG[i] is not a source register of instruction j DATAFLOW[i][j] = 10 (RED arrow from REG[i] to instruction j) if • • REG[i] is a source register of instruction j and • An in-flight instruction will write to REG[i] (REGBusy[i] is TRUE) DATAFLOW[i][j] = 11 (GREEN arrow from REG[i] to instruction j) if • • REG[i] is a source register of instruction j and • No in-flight instruction will write to REG[i] (REGBusy[i] is FALSE) 8

Example: Scoreboard Algorithm A: LD F6 , 0(R2) B: LD F2 , 0(R3) C: MULTD F0 , F2 , F4 D: SUBD F8, F6 , F2 E: DIVD F10, F0 , F6 F: LD F6 , 8(R2) Assume ADDR and MEM stages of LD and SD are 1 cycle each • All FP operations take 4 cycles each • Assume 1 cycle each for register read (R) and register write (W) stages • Dependencies RAW between A,D and A,E (F6) • RAW between B,C and B,D (F2) • RAW between C,E (F0) • WAR between E,F (F6) • WAW between A,F (F6) • 9 9

Scoreboard R ADD R ADD IR Issue ADDR MEM R WB R DIV MULT R 10 10

Example: Scoreboard Algorithm A: LD F6, 0(R2) B: LD F2 , 0(R3) A B C 1 I 2 R I A A B B F6 F6 F2 F2 C: MULTD F0, F2 , F4 A B C C C 1 I F4 F4 F0 F0 2 R I I C C 3 ADDR R I I A A B B F6 F6 F2 F2 11 11 C C

Example: Scoreboard Algorithm A: LD F6, 0(R2) B: LD F2, 0(R3) C: MULTD F0, F2, F4 D: SUBD F8, F6, F2 D F8 C A B C D F4 1 I F0 C 2 R I I 3 ADDR R I I A B 4 MEM ADDR R I R I F6 F2 D C D 12 12

Example: Scoreboard Algorithm A: LD F6, 0(R2) A B C D E B: LD F2, 0(R3) C: MULTD F0, F2, F4 1 I D: SUBD F8, F6, F2 I I 2 R E: DIVD F10, F0, F6 3 ADDR R I R I D E 4 MEM ADDR R I ADDR R I 5 W MEM R R I W MEM R R I F8 F10 C A IS SAFE TO WRITE A IS SAFE TO WRITE F4 F0 Writes to WB in first half of cycle Writes to WB in first half of cycle C A removes its arrow to F6 A removes its arrow to F6 in first half in first half Colors outgoing arrow from F6 Green Colors outgoing arrow from F6 Green E B Readers read register in second half of Readers read register in second half of cycle cycle F2 E issues and colors its arrow from issues and colors its arrow from F6 green F6 green in in E F6 second half second half C D D E 13 13

Example: Scoreboard Algorithm B: LD F2, 0(R3) B C D E F C: MULTD F0, F2, F4 D: SUBD F8, F6, F2 2 I E: DIVD F10, F0, F6 I I 3 R F: LD F6, 8(R2) 4 ADDR R I R I D E 5 MEM R R I R R I 6 W R R R I W R R R I F8 F10 C F4 F0 B removes its B removes its arrow to F2 arrow to F2 in first half and in first half and C changes C, D outgoing arrows to green changes C, D outgoing arrows to green E F F2 C C (and also D) sees both its operands ready (and also D) sees both its operands ready F6 (green outgoing arrows). Reads operands (green outgoing arrows). Reads operands and moves to EX stage at end of the cycle at end of the cycle and moves to EX stage C D D E 14 14

Example: Scoreboard Algorithm C: MULTD F0, F2, F4 C D E F D: SUBD F8, F6, F2 E: DIVD F10, F0, F6 3 I F: LD F6, 8(R2) I I 4 R 5 R R I R I D E 6 R R R I R R I 7 * -- R R * -- R R F8 F10 C F4 F0 C, D remove outgoing arrows C, D remove outgoing arrows E F F2 F6 E 15 15

Example: Scoreboard Algorithm C: MULTD F0, F2, F4 C D E F D: SUBD F8, F6, F2 E: DIVD F10, F0, F6 3 I F: LD F6, 8(R2) I I 4 R 5 R R I R I D E 6 R R R I R R I 7 * -- R R * -- R R F8 F10 C 8 * -- R ADDR * -- R ADDR F4 F0 E F F2 F6 E 16 16

Example: Scoreboard Algorithm C: MULTD F0, F2, F4 C D E F D: SUBD F8, F6, F2 E: DIVD F10, F0, F6 3 I F: LD F6, 8(R2) I I 4 R 5 R R I R I D E 6 R R R I R R I 7 * -- R R * -- R R F8 F10 C 8 * -- R ADDR * -- R ADDR F4 9 * -- R MEM MEM * -- R F0 10 * -- R W W * -- R E F F2 F6 F in in WB stage but in in WB stage but is is NOT SAFE-TO-WRITE NOT SAFE-TO-WRITE F due to WAR hazard with E (green arrow out of F6) due to WAR hazard with E (green arrow out of F6) E 17 17

Example: Scoreboard Algorithm C: MULTD F0, F2, F4 C D E F D: SUBD F8, F6, F2 E: DIVD F10, F0, F6 3 I F: LD F6, 8(R2) I I 4 R 5 R R I R I D E 6 R R R I R R I 7 * -- R R * -- R R F8 F10 C 8 * -- R ADDR * -- R ADDR F4 9 * -- R MEM * -- R MEM F0 F2 10 * -- R W * -- R W E F 11 W W R W W W R W C, D are SAFE-TO-WRITE; C, D are SAFE-TO-WRITE; F is not safe F is not safe F6 Assume Assume C C is chosen to write; is chosen to write; Makes arrow out of F0 green. Makes arrow out of F0 green. E will read its operands in E will read its operands in E second half of cycle second half of cycle 18 18 1 1

Example: Scoreboard Algorithm C: MULTD F0, F2, F4 C D E F D: SUBD F8, F6, F2 E: DIVD F10, F0, F6 3 I F: LD F6, 8(R2) I I 4 R 5 R R I R I D E 6 R R R I R R I 7 * -- R R * -- R R F8 F10 8 * -- R ADDR * -- R ADDR F4 9 * -- R W * -- R W F0 10 * -- R W * -- R W E F 11 W W R W W W R W F2 F6 C, D are SAFE-TO-WRITE; F is not safe C, D are SAFE-TO-WRITE; F is not safe E 19 19 Assume Assume C C is chosen to write; Makes arrow out of F0 is chosen to write; Makes arrow out of F0 green. E will read its operands in second half of cycle green. E will read its operands in second half of cycle

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.