Processor Organization and Performance Chapter 6 S. Dandamudi - PDF document

Processor Organization and Performance Chapter 6 S. Dandamudi Outline Introduction Instruction set design issues Operand types Number of addresses Addressing modes 3-address machines Instruction types 2-address

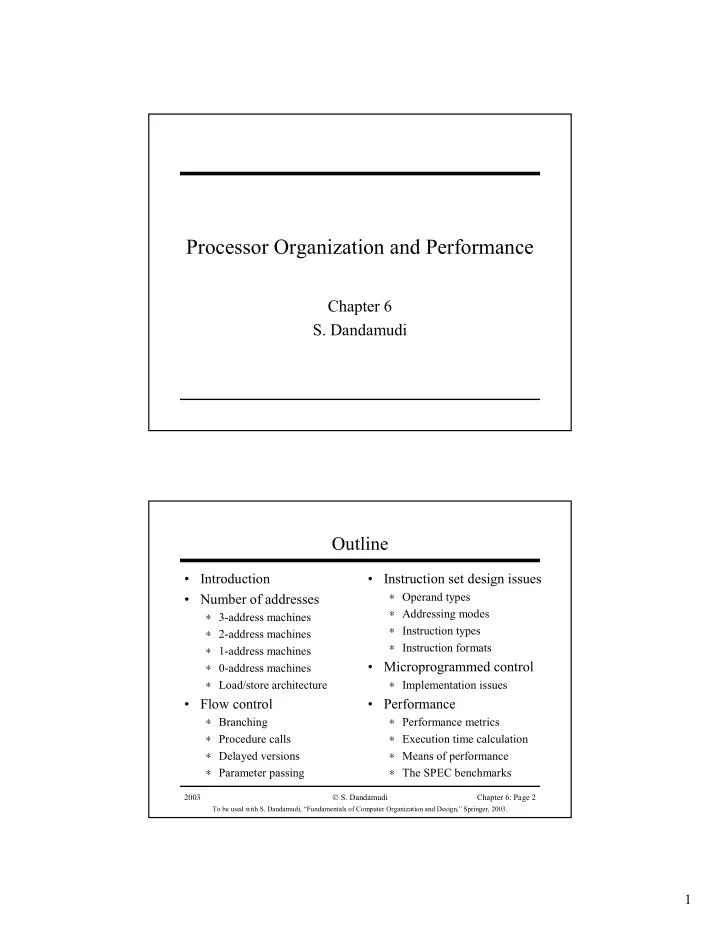

Processor Organization and Performance Chapter 6 S. Dandamudi Outline • Introduction • Instruction set design issues ∗ Operand types • Number of addresses ∗ Addressing modes ∗ 3-address machines ∗ Instruction types ∗ 2-address machines ∗ Instruction formats ∗ 1-address machines • Microprogrammed control ∗ 0-address machines ∗ Load/store architecture ∗ Implementation issues • Flow control • Performance ∗ Branching ∗ Performance metrics ∗ Procedure calls ∗ Execution time calculation ∗ Delayed versions ∗ Means of performance ∗ Parameter passing ∗ The SPEC benchmarks 2003 S. Dandamudi Chapter 6: Page 2 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 1

Introduction • We discuss three processor-related issues » Instruction set design issues – Number of addresses – Addressing modes – Instruction types – Instruction formats » Microprogrammed control – Hardware implementation – Software implementation » Performance issues – Performance metrics – Standards 2003 S. Dandamudi Chapter 6: Page 3 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Number of Addresses • Four categories ∗ 3-address machines » 2 for the source operands and one for the result ∗ 2-address machines » One address doubles as source and result ∗ 1-address machine » Accumulator machines » Accumulator is used for one source and result ∗ 0-address machines » Stack machines » Operands are taken from the stack » Result goes onto the stack 2003 S. Dandamudi Chapter 6: Page 4 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 2

Number of Addresses (cont’d) • Three-address machines ∗ Two for the source operands, one for the result ∗ RISC processors use three addresses ∗ Sample instructions add dest,src1,src2 ; M(dest)=[src1]+[src2] sub dest,src1,src2 ; M(dest)=[src1]-[src2] mult dest,src1,src2 ; M(dest)=[src1]*[src2] 2003 S. Dandamudi Chapter 6: Page 5 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Number of Addresses (cont’d) • Example ∗ C statement A = B + C * D – E + F + A ∗ Equivalent code: mult T,C,D ;T = C*D add T,T,B ;T = B+C*D sub T,T,E ;T = B+C*D-E add T,T,F ;T = B+C*D-E+F add A,T,A ;A = B+C*D-E+F+A 2003 S. Dandamudi Chapter 6: Page 6 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 3

Number of Addresses (cont’d) • Two-address machines ∗ One address doubles (for source operand & result) ∗ Last example makes a case for it » Address T is used twice ∗ Sample instructions load dest,src ; M(dest)=[src] add dest,src ; M(dest)=[dest]+[src] sub dest,src ; M(dest)=[dest]-[src] mult dest,src ; M(dest)=[dest]*[src] 2003 S. Dandamudi Chapter 6: Page 7 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Number of Addresses (cont’d) • Example ∗ C statement A = B + C * D – E + F + A ∗ Equivalent code: load T,C ;T = C mult T,D ;T = C*D add T,B ;T = B+C*D sub T,E ;T = B+C*D-E add T,F ;T = B+C*D-E+F add A,T ;A = B+C*D-E+F+A 2003 S. Dandamudi Chapter 6: Page 8 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 4

Number of Addresses (cont’d) • One-address machines ∗ Uses special set of registers called accumulators » Specify one source operand & receive the result ∗ Called accumulator machines ∗ Sample instructions load addr ; accum = [addr] store addr ; M[addr] = accum add addr ; accum = accum + [addr] sub addr ; accum = accum - [addr] mult addr ; accum = accum * [addr] 2003 S. Dandamudi Chapter 6: Page 9 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Number of Addresses (cont’d) • Example ∗ C statement A = B + C * D – E + F + A ∗ Equivalent code: load C ;load C into accum mult D ;accum = C*D add B ;accum = C*D+B sub E ;accum = B+C*D-E add F ;accum = B+C*D-E+F add A ;accum = B+C*D-E+F+A store A ;store accum contents in A 2003 S. Dandamudi Chapter 6: Page 10 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 5

Number of Addresses (cont’d) • Zero-address machines ∗ Stack supplies operands and receives the result » Special instructions to load and store use an address ∗ Called stack machines (Ex: HP3000, Burroughs B5500) ∗ Sample instructions push addr ; push([addr]) pop addr ; pop([addr]) add ; push(pop + pop) sub ; push(pop - pop) mult ; push(pop * pop) 2003 S. Dandamudi Chapter 6: Page 11 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Number of Addresses (cont’d) • Example ∗ C statement A = B + C * D – E + F + A ∗ Equivalent code: push E sub push C push F push D add Mult push A push B add add pop A 2003 S. Dandamudi Chapter 6: Page 12 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 6

Number of Addresses (cont’d) 2003 S. Dandamudi Chapter 6: Page 13 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Load/Store Architecture • Instructions expect operands in internal processor registers ∗ Special LOAD and STORE instructions move data between registers and memory ∗ RISC and vector processors use this architecture ∗ Reduces instruction length 2003 S. Dandamudi Chapter 6: Page 14 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 7

Load/Store Architecture (cont’d) • Sample instructions load Rd,addr ;Rd = [addr] store addr,Rs ;(addr) = Rs add Rd,Rs1,Rs2 ;Rd = Rs1 + Rs2 sub Rd,Rs1,Rs2 ;Rd = Rs1 - Rs2 mult Rd,Rs1,Rs2 ;Rd = Rs1 * Rs2 2003 S. Dandamudi Chapter 6: Page 15 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Number of Addresses (cont’d) • Example ∗ C statement A = B + C * D – E + F + A ∗ Equivalent code: load R1,B mult R2,R2,R3 load R2,C add R2,R2,R1 load R3,D sub R2,R2,R4 load R4,E add R2,R2,R5 load R5,F add R2,R2,R6 load R6,A store A,R2 2003 S. Dandamudi Chapter 6: Page 16 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 8

Flow of Control • Default is sequential flow • Several instructions alter this default execution ∗ Branches » Unconditional » Conditional » Delayed branches ∗ Procedure calls » Delayed procedure calls 2003 S. Dandamudi Chapter 6: Page 17 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Flow of Control (cont’d) • Branches ∗ Unconditional » Absolute address » PC-relative – Target address is specified relative to PC contents ∗ Example: MIPS » Absolute address j target » PC-relative b target 2003 S. Dandamudi Chapter 6: Page 18 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 9

Flow of Control (cont’d) 2003 S. Dandamudi Chapter 6: Page 19 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Flow of Control (cont’d) • Branches ∗ Conditional » Jump is taken only if the condition is met ∗ Two types » Set-Then-Jump – Condition testing is separated from branching – Condition code registers are used to convey the condition test result » Example: Pentium code cmp AX,BX je target 2003 S. Dandamudi Chapter 6: Page 20 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 10

Flow of Control (cont’d) » Test-and-Jump – Single instruction performs condition testing and branching » Example: MIPS instruction beq Rsrc1,Rsrc2,target � Jumps to target if Rsrc1 = Rsrc2 • Delayed branching ∗ Control is transferred after executing the instruction that follows the branch instruction » This instruction slot is called delay slot ∗ Improves efficiency 2003 S. Dandamudi Chapter 6: Page 21 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Flow of Control (cont’d) • Procedure calls ∗ Requires two pieces of information to return » End of procedure – Pentium � uses ret instruction – MIPS � uses jr instruction » Return address – In a (special) register � MIPS allows any general-purpose register – On the stack � Pentium 2003 S. Dandamudi Chapter 6: Page 22 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 11

Flow of Control (cont’d) 2003 S. Dandamudi Chapter 6: Page 23 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. Flow of Control (cont’d) Delay slot 2003 S. Dandamudi Chapter 6: Page 24 To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003. 12

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.