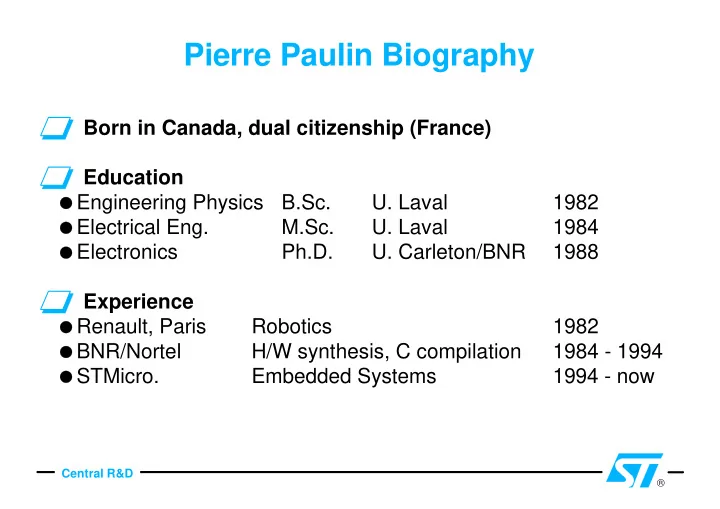

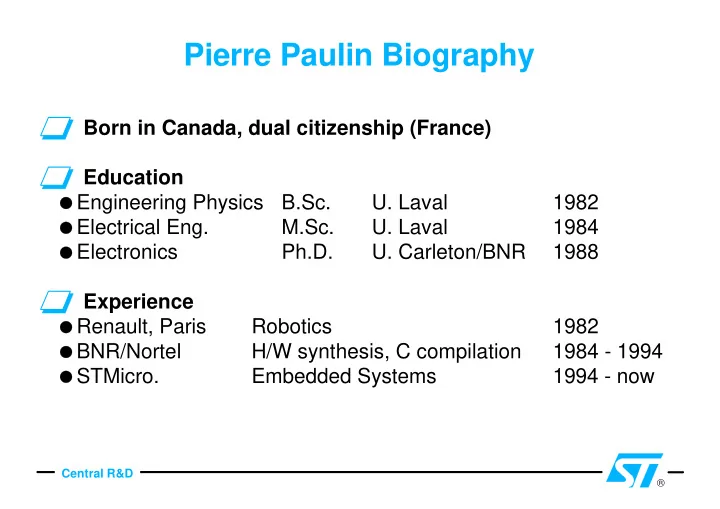

Pierre Paulin Biography Born in Canada, dual citizenship (France) Education Engineering Physics B.Sc. U. Laval 1982 Electrical Eng. M.Sc. U. Laval 1984 Electronics Ph.D. U. Carleton/BNR 1988 Experience Renault, Paris Robotics 1982 BNR/Nortel H/W synthesis, C compilation 1984 - 1994 STMicro. Embedded Systems 1994 - now Central R&D

Towards Application-Specific Architecture Platforms: Embedded Systems Design Automation Technologies Pierre Paulin Director, Embedded Systems Technology Central R&D STMicroelectronics

STMicroelectronics Franco-Italian origin (formerly SGS-Thomson Microelectronics) International company now, but with strong roots in Europe Central R&D

STMicroelectronics POSITIVES French cuisine Driving german cars SWEDEN FINLAND on german highways NORWAY ESTONIA Italian passion LATVIA DENMARK LITHUANIA BELARUS Swiss sense of organization NETHERLANDS IRELAND UNITED KINGDOM POLAND GERMANY UKRAINE BELGIUM LUXEMBOURG CZECH English courtesy REPUBLIC SLOVAKIA MOLDOVA LIECHTENSTEIN AUSTRIA HUNGARY FRANCE ROMANIA SWITZERLAND SLOVENIA CROATIA Canadian real estate BOSNIA & SERBIA HERZEGOVINA SAN MONACO BULGARIA MARINO MONTENEGRO PORTUGAL ITALY ANDORRA MACEDONIA VATICAN ALBANIA SPAIN CITY U.S. stock options GREECE MALTA Central R&D

STMicroelectronics NEGATIVES U.S. stock options (one week later) Canadian weather SWEDEN FINLAND French courtesy NORWAY ESTONIA LATVIA DENMARK LITHUANIA Driving french cars BELARUS on London motorways NETHERLANDS IRELAND UNITED KINGDOM POLAND GERMANY UKRAINE BELGIUM LUXEMBOURG CZECH REPUBLIC English food SLOVAKIA MOLDOVA LIECHTENSTEIN AUSTRIA HUNGARY FRANCE ROMANIA SWITZERLAND SLOVENIA CROATIA BOSNIA & SERBIA Swiss passion HERZEGOVINA SAN MONACO BULGARIA MARINO MONTENEGRO PORTUGAL ITALY ANDORRA MACEDONIA VATICAN ALBANIA SPAIN CITY Italian sense of GREECE organization MALTA Central R&D

Outline Introduction Part I: System design platforms Sample design platform: ST set-top box ASAP: Application-Specific Architecture Platform Which platform components? H/W vs FPGA vs AS-Processors vs GP-Processors Platform design automation challenges Part II: ST platform automation technologies ST system design environment ST embedded software development tools Central R&D

Bridging the Process / Design Gap Design complexity (transistor System Level count) Entry Process capability HW-SW +50% / year Methodologies Platforms, IP Reuse RTL design RTL-to-layout capability Flow +20% / year Year Source : ST 96 97 98 99 2000 2001 2002 Central R&D

System Design Technology Strategy Complement ST's rich, heterogeneous process technology offer with tools/methods supporting it at architecture and system design levels Domain-specific tools: DSP, control/protocol, real-time System Level Executable specifications, system validation Entry DO THE RIGHT THING Processors, memories, logic, datapaths, analog, RF, A/D HW-SW Virtual prototype, Architecture exploration, codesign Methodologies Platform-based design Platforms, High performance S/W compilation IP Reuse DO THE THING RIGHT, FAST RTL-to-layout Flow Logic, analog, DRAM, SRAM, Flash, High-speed, Power DO IT IN ON A SINGLE CHIP! Process capabilities Central R&D

Part I: System Design Platforms STMicroelectronics

ST Platform Example: Set-top box, DVD Development of complete IP foundation and design platform Front-end, demux Std/High-def MPEG2 video/audio, Display, 2D/3D graphics RISC, AS-DSP, smart card, I/O MPEG Multi-channel/ Dolby AC-3 5.1 channels : DACs STi5518 STV0299 DBS OMEGA TUNER QPSK Rx PAL/NTSC VCR Smart Cards Led to ST world leadership position MPEG2 audio/video decoder -> 30 million chips sold Digital satellite set-top box chips-> Over 70% market share Central R&D

Platform Approach = Fast Derivatives STi7000 family HD/3D HD decoding, HD display, Capable OpenCable 3D graphics, High quality display OMEGA2 Web Interactive 2D/3D graphics, Hard-Disk Drive, MediaWeb, DISH Player, DVB-MHP, DIRECTV++, UK Cable Multiple demux, Java, WinCE OMEGA1 DVB Interactive Still image plane, BSkyB, Canal+, ONdigital, TPS BLT engine, Enhanced display MediaOne, US Cable DCT2K, Explorer 2K OMEGA Integrated Audio/Video, Demux Basic Pay TV DISH, DIRECTV Micro, On-screen Display ST Digital TV Product Families Central R&D

Application-Specific Architecture Platform (ASAP) Reconfigurable Executable system Platform Template specification Config uProg DSP, MCU I/O proc. MMedia Standard Domain-specific processor Processors languages System-oriented Derivative Mapping Predefined set of C/C++ environments standard IP - Std. Processors - Memory Fixed Silicon with - Busses IEEE 1394 high programmability: - S/W on general purpose Set of optional IP's and domain-specific - Specialized S/W processors MPEG2 processors ST40 decoder - Microprogrammable - Hardwired IP I/O processing - I/O Programmable - FPGA coprocessors Platform Instance Central R&D

Platform Example: Set-top Box Platform MPEG2 Standard ROM/Flash DRAM/SRAM I/O blocks 2D graphics video Template decoder Glue Logic D/A, A/D Configurable STBus ASIC Field Standard Display 3D Audio Control Prog. coprocessor Processor I/O blocks DSP MCU Proc. Analysis of application requirements Derivation to specific platform instance F/W Firewire MPEG2 SRAM ROM iEEE 1394 decoder Glue audio, video Logic Platform Configured STBus D/ A Instance Display Audio Control RS-232 coprocessor DSP MCU Central R&D

Platforms: Divide and Conquer Application IP System week function GSM, UMTS Set-top box, DVD, HDTV xDSL modem, Internet switch System-level expertise Car multimedia S/W expert SmartCard Platform Hard-Disk Drive programming Platform "Insulation" H/W-S/W Platform IP MPEG2 RAM architecture Wireless terminals decoder month Multimedia, Graphics Domain-specific Domain-specific cores: platform expertise 2D ST40 graphics AS-MCU, AS-DSP, Network Proc. Fast platform derivatives Microarchitecture "Insulation" RTL Component IP year Commodity cores: Layout DSP, MCU, RISC, Bus A/D, D/A, I/O, Analog Component expertise Flat Panels Process differentiators Libraries: Cells, memories, I/O (BICMOS, RFCMOS, eDRAM, eFlash, OTP) Central R&D

Platform Architecture Definition Application Platform Requires combination of four competences Short Time-To-Market Long Platform Lifetime 3 year Standard Memory IP Amortize increasing H/W Processors coprocessor NRE costs e.g. mask set 250 -> 500 K$ Process Technology IP Components Central R&D

Which Platform Components ? Application IP week GSM, UMTS Set-top box, DVD, HDTV xDSL modem, Internet switch Car multimedia SmartCard Hard-Disk Drive Platform "Insulation" Platform IP MPEG2 RAM Wireless terminals decoder month Multimedia, Graphics Domain-specific cores: 2D ST40 graphics AS-MCU, AS-DSP, Network Proc. Microarchitecture "Insulation" Component IP year Commodity cores: DSP, MCU, RISC, Bus A/D, D/A, I/O, Analog Flat Panels Libraries: Cells, memories, I/O Central R&D

Design Platform Component Options Low design cost High design cost High flexibility Low flexibility High power/operation Low power/operation Lower speed High speed Medium part cost Lowest part cost ASIP Structured RTL FPGA FPGA & Config. DSP Analog GPP (General H/W Custom Flow Processor Processor MCU Purpose Processor Central R&D

Processor Evolution Case Study ASIP Structured RTL Config. DSP FPGA GPP (General Custom Flow Processor MCU Purpose Processor MPEG2 Audio MPEG1 ASIP DSP ASIC 1992 1995 2000 Central R&D

Component Usage Trends ASIP Structured RTL FPGA & Config. DSP FPGA GPP (General Custom Flow Processor Processor MCU Purpose Processor 1990's 2000's Central R&D

Embedded Processor Market Share 30.8 B$ (9.1B parts) 17% 5.2 B$ 32 bit MPU/MCU Average price ~ $15 1.4 B$ 32 bit DSP (flt) 4% 29% 8.8 B$ 16-24 bit DSP (int) 13.5 B$ 8-16 bit MCU (4.2B parts) + 16-24 bit DSP 32 bit MPU/MCU 1.4 B$ 10% = 80% 2002 revenues 5.7 B$ 16 bit MCUs 19% 32 bit DSP (flt) 0.4 B$ 95% 2002 volume 2.9 B$ 16-24 bit DSP (int) 21% 16 bit MCUs 20% 2.7 B$ Average price < $3 31% 9.6 B$ 8 bit MCUs 8 bit MCUs 6.2 B$ 46% Source: InStat 1998 Dataquest 1998 2002 1997 Central R&D

Competitive Differentiation % of Product Functionality Performance/Cost/Power Differentiation Analog ASIP, DSP RTL FPGA RISC, H/W Config. MCU H/W H/W GPP (General Processor Purpose Processor Appplication IP reuse Algorithms Executable System specification Key application Low-power/ Differentiators knowledge high-speed design Processor Tools for S/W Rapid prototyping Architecture productivity Central R&D

Recommend

More recommend