Overview Memories Strictly Structured VHDL Introduction to - PowerPoint PPT Presentation

Overview Memories Strictly Structured VHDL Introduction to Structured VLSI Design VHDL IV Joachim Rodrigues Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH,

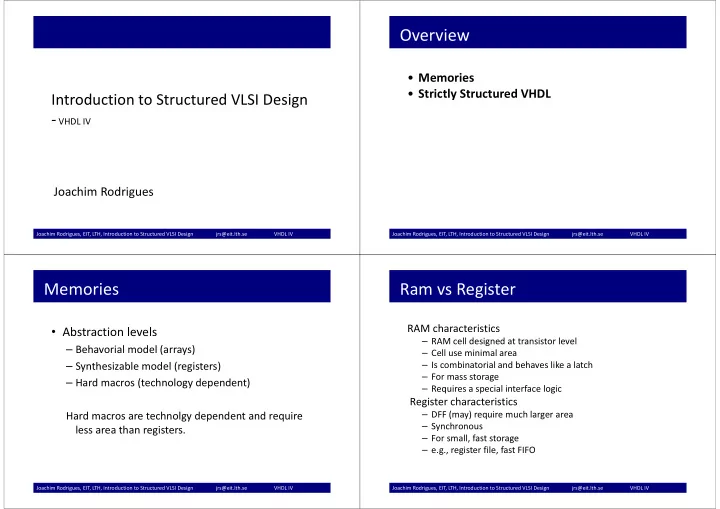

Overview • Memories • Strictly Structured VHDL Introduction to Structured VLSI Design ‐ VHDL IV Joachim Rodrigues Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Memories Ram vs Register RAM characteristics • Abstraction levels – RAM cell designed at transistor level – Behavorial model (arrays) – Cell use minimal area – Is combinatorial and behaves like a latch – Synthesizable model (registers) – For mass storage – Hard macros (technology dependent) – Requires a special interface logic Register characteristics – DFF (may) require much larger area Hard macros are technolgy dependent and require – Synchronous less area than registers. – For small, fast storage – e.g., register file, fast FIFO Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV

RAM ‐ Single Port RAM ‐ dual port LIBRARY ieee; USE work.ram_package.ALL; USE ieee.std_logic_1164.ALL; ENTITY ram_dual IS USE ieee.numeric_std.ALL; PORT (clock1, clock2 : IN std_logic; Dual Port: Concurrent data : IN word; Read and Write ENTITY ram IS write_address, read_address : IN address_vector; GENERIC ( ADDRESS_WIDTH : integer := 4; DATA_WIDTH : integer := 8 ); we : IN std_logic; q : OUT word ); PORT ( clock : IN std_logic ; data : IN std_logic_vector (DATA_WIDTH - 1 DOWNTO 0); END ram_dual; Dual-port RAMs write_address, read_adress : IN std_logic_vector (ADDRESS_WIDTH - 1 DOWNTO 0); we : IN std_logic ; ARCHITECTURE rtl OF ram_dual IS Are very expensive in area q : OUT std_logic_vector (DATA_WIDTH - 1 DOWNTO 0) ); SIGNAL ram_block : RAM; and should be avoided !! END ram; SIGNAL read_address_reg : address_vector; ARCHITECTURE rtl OF ram IS TYPE RAM IS ARRAY (0 TO 2 ** ADDRESS_WIDTH - 1) OF BEGIN PROCESS (clock1) Dual port functionality may std_logic_vector (DATA_WIDTH - 1 DOWNTO 0); BEGIN IF (clock1'event AND clock1 = '1') THEN be realized by a hybrid IF (we = '1') THEN ram_block(write_address) <= data; A single word may be single-port RAM. ram_block : RAM; END IF ; read or written BEGIN PROCESS (clock,we) END IF ; Read on pos edge and write BEGIN during one clock cycle. END PROCESS; on neg edge. IF (clock'event AND clock = '1') THEN IF (we = '1') THEN PROCESS (clock2) ram_block( to_integer (unsigned(write_address))) <= data; BEGIN END IF; IF (clock2'event AND clock2 = '1') THEN q <= ram_block( to_integer (unsigned(read_address))); q <= ram_block(read_address_reg); END IF; read_address_reg <= read_address; END PROCESS; an adress is always positiv END IF; END rtl; END PROCESS; END rtl; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV ROM Register File library IEEE; use IEEE.std_logic_1164.all; Behavioral 16x4 ROM model Registers are arranged as an 1 ‐ d array entity rom_rtl is port (ADDR: in INTEGER range 0 to 15; • Each register is accessible with an address DATA: out STD_LOGIC_VECTOR (3 downto 0)); end rom_rtl; • Usually 1 write port (with write enable signal) architecture XILINX of rom_rtl is • May have multiple read ports subtype ROM_WORD is STD_LOGIC_VECTOR (3 downto 0); type ROM_TABLE is array (0 to 15) of ROM_WORD; constant ROM: ROM_TABLE := ROM_TABLE'( ROM_WORD'("0000"), ROM_WORD'("0001"), ROM_WORD'("0010"), ... begin DATA <= ROM(ADDR); -- Read from the ROM For a real hard macro (ASIC), a end XILINX; file that holds the coefficients need to submitted to the ASIC Vendor. Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV

Register File cont’d Register File cont’d • Register array: 4 ‐ word register file w/ 1 write port – 4 registers and two read ports – Each register has an enable signal • Write decoding circuit: – 0000 if wr_en is 0 – 1 bit asserted according to w_addr if wr_en is 1 • Read circuit: – A mux for each read port Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Strictly Structured VHDL “Gaisler’s method” is a design methodology (code style), which can be summarized as: Strictly Structured VHDL – Use records – Use synchronous reset ‐ GAISLER’S METHOD – Apply strong hierarchies Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV

Realization of FSMs ‐ behavorial Strictly Structured VHDL architecture implementation of state_machine is type state_type is (st0, st1,st2, st3); -- defines the states type reg_type is record • How is it done? output : STD_LOGIC_VECTOR (m-1 downto 0); state : state_type; end record; Signal r ,rin : reg_type; begin – Local signals (r, rin) are stored in records and contain all combinational : process (input,reset,r) -- Combinational part variable v : reg_type; registered values. begin v : = r; -- Setting the variable – All outputs are stored in a entity specific record type case (r.state) is -- Current state and input dependent when st0 => if (input = ”01”) then declared in a global interface package – enables re ‐ use. v.state := st1; v.output := ”01” end if; – Use a local variable (v) of the same type as the registered when ... when others => v.state := st0; -- Default values. v.output := ”00”; end case; – reset handling moves to combinational part. if (reset = ’1’) then -- Synchronous reset v.state := st0; -- Start in idle state end if; rin <= v; -- update values at register input output <= v.output; -- Combinational output --output <= r.output; -- Registered output end process; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Realization of FSMs ‐ sequential Strictly Structured VHDL ‐ Advantages Adding a signal in traditional style • Add port in entity declaration • Add signal to sensitivity list synchronous : process (clk)– This part is always, always the same DUT begin • Add port in component declaration if clk’event and clk = ’1’ then • Add port in component instantiation r <= rin; end if; end process; end architecture; Adding a signal in Strictly Structured VHDL methodology DUT • Add element in record declaration Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV

Structured VHDL Structured VHDL ‐ Stored signals Obvious Advantages Adding a stored signal in traditional style • Readability • Add two signals (current, next) Comb • Less written code • Add signal to sensitivity list • Maintainance and re ‐ useability • Add reset value • Update on clock edge Current Next Hidden Advantages • Synthesizable Adding a signal in Structured VHDL methodology • Synchronous reset • Add element in declaration record • No need to update sensitivity lists Comb • Faster simulation (less concurrent statements) r rin Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Structured VHDL Realization of FSMs ‐ Example architecture implementation of state_machine is library IEEE;use library IEEE; type state_type is (st0, st1,st2, st3); -- defines the states IEEE.STD_LOGIC_1164.all; type reg_type is record use IEEE.STD_LOGIC_1164.all; output : STD_LOGIC_VECTOR (m-1 downto 0); Use work.global_interface.pkg; state : state_type; library global_interface is new_signal : std_logic; input_type is record entity state_machine is end record; -- Type record port (clk : in STD_LOGIC; Signal r ,rin : reg_type; newsignal : std_logic; reset : in STD_LOGIC; begin end record; input : in input_type; end; combinational : process (input,reset,r) -- combinational part output : out output_type; variable v : reg_type; end state_machine; begin v : = r; -- Setting the variable case (r.state) is -- Current state and input dependent when st0 => if (input = ’1’) then v.state := st1; state_machine v.output := ”01” input_type output_type end if; when ... when others => v.state := st0; -- Default v.output := ”00”; end case; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL IV

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.