Overview Motivation and introduction Functional model of a memory - PDF document

10/28/2014 Overview Motivation and introduction Functional model of a memory ECE 553: TESTING AND A simple minded test and its limitations TESTABLE DESIGN OF Fault models DIGITAL SYSTES DIGITAL SYSTES March tests and

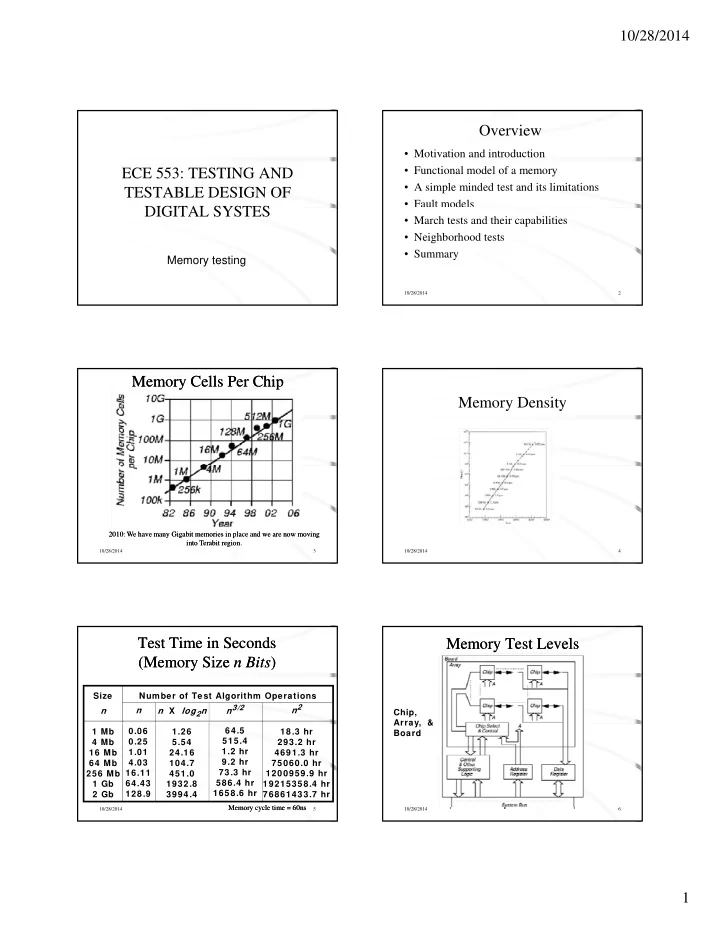

10/28/2014 Overview • Motivation and introduction • Functional model of a memory ECE 553: TESTING AND • A simple minded test and its limitations TESTABLE DESIGN OF • Fault models DIGITAL SYSTES DIGITAL SYSTES • March tests and their capabilities • Neighborhood tests • Summary Memory testing 10/28/2014 2 Memory Cells Per Chip Memory Cells Per Chip Memory Density 2010: We have many Gigabit memories in place and we are now moving 2010: We have many Gigabit memories in place and we are now moving into Terabit region. into Terabit region. 10/28/2014 3 10/28/2014 4 Test Time in Seconds Test Time in Seconds Memory Test Levels Memory Test Levels (Memory Size n Bits ) (Memory Size n Bits ) Size Number of Test Algorithm Operations n 3/2 n 2 n n n X log 2 n Chip, Array, & Array & 64.5 1 Mb 0.06 1.26 18.3 hr Board 515.4 4 Mb 0.25 5.54 293.2 hr 1.2 hr 16 Mb 1.01 24.16 4691.3 hr 9.2 hr 64 Mb 4.03 104.7 75060.0 hr 16.11 73.3 hr 256 Mb 451.0 1200959.9 hr 64.43 586.4 hr 1 Gb 1932.8 19215358.4 hr 128.9 1658.6 hr 2 Gb 3994.4 76861433.7 hr Memory cycle time = 60ns Memory cycle time = 60ns 10/28/2014 5 10/28/2014 6 1

10/28/2014 Functional Model Functional Model Simplified Functional Model Simplified Functional Model 10/28/2014 7 10/28/2014 8 Functional Faults Functional Faults A simple minded test Fault Functional fault for cell := 0 to n - 1 (or any other order) do SAF a Cell stuck SAF b Driver stuck write 0 to A [cell]; SAF c Read/w rite line stuck d Chip-select line stuck read A [cell]; { Expected value = 0} SAF SAF e Data line stuck write 1 to A [cell]; f Open circuit in data line SAF read A [cell]; { Expected value 1 } read A [cell]; { Expected value = 1 } CF g g Short circuit betw een data lines CF h Crosstalk betw een data lines end for; AF i Address line stuck AF j Open circuit in address line AF k Shorts betw een address lines What does this test achieve? AF l Open circuit in decoder What kind of faults does it detect and it AF m Wrong address access fault coverage? AF n Multiple simultaneous address access o Cell can be set to 0 (1) but not to 1 (0) TF NPSF p Pattern sensitive cell interaction 10/28/2014 9 10/28/2014 10 Stuck-at Faults Stuck-at Faults • Condition : For each cell, must read a 0 and a 1. Reduced Functional Faults Reduced Functional Faults Fault SAF Stuck-at fault TF Transition fault CF Coupling fault NPSF Neighborhood Pattern Sensitive fault 10/28/2014 11 10/28/2014 12 2

10/28/2014 Transition Faults Transition Faults Coupling Faults Coupling Faults • Cell fails to make 0 1 or 1 0 transition • Coupling Fault (CF): Transition in bit j causes • Condition : Each cell must undergo a transition unwanted change in bit i • 2-Coupling Fault : Involves 2 cells, special case of k- and a transition, and be read after such, before Coupling Fault undergoing any further transitions. d i f th t iti – Must restrict k cells to make practical • Inversion and Idempotent CFs -- special cases of 2- Coupling Faults • Bridging and State Coupling Faults involve any # of cells, caused by logic level • Dynamic Coupling Fault (CFdyn) -- Read or write on j forces i to 0 or 1 < /0> transition fault 10/28/2014 13 10/28/2014 14 March Test Notation March Test Notation March Test Notation (Continued) March Test Notation (Continued) r0 -- Read a 0 from a memory location r1 -- Read a 1 from a memory location • -- Complement the cell contents w0 -- Write a 0 to a memory location y • -- Increasing memory addressing w1 -- Write a 1 to a memory location -- Decreasing memory addressing • -- Write a 1 to a cell containing 0 • -- Either increasing or decreasing -- Write a 0 to a cell containing 1 10/28/2014 15 10/28/2014 16 Address Decoder Faults (ADFs) Address Decoder Faults (ADFs) MATS+ March Test MATS+ March Test M0: { March element (w0) } • Address decoding error assumptions: for cell := 0 to n - 1 (or any other order) do – Decoder does not become sequential write 0 to A [cell]; – Same behavior during both read & write M1: { March element (r0, w1) } for cell := 0 to n - 1 do • Multiple ADFs must be tested for read A [cell]; { Expected value = 0} • Decoders have CMOS stuck-open faults write 1 to A [cell]; M2: {March element (r1, w0) } for cell := n – 1 down to 0 do read A [cell]; { Expected value = 1 } write 0 to A [cell]; 10/28/2014 17 10/28/2014 18 3

10/28/2014 Proof Illustration Proof Illustration Combinations that must be tested Combinations that must be tested Theorem 9.2 Theorem 9.2 • A March test satisfying conditions 1 & 2 detects all address decoder faults. Conditions for proof Conditions for proof • ... Means any # of read or write operations • Before condition 1 must have wx element • Before condition 1, must have wx element – x can be 0 or 1, but must be consistent in test Condition March element 1 (rx, …, w x ) 2 (r x , …, w x) 10/28/2014 19 10/28/2014 20 Sufficiency Proof Sufficiency Proof Necessity Proof Necessity Proof • Faults A and B : Detected by SAF test • Removing rx from Condition 1 prevents A or B • Fault C : Initialize memory to h ( x or x ). Subsequent fault detection when x read March element that reads h and writes h detects • Removing rx from Condition 2 prevents A or B fault detection when x read fault detection when x read Fault C Fault C. • Removing rx or wx from Condition 1 misses fault – Marching writes h to A v . Detection: read A w D2 – Marching writes h to A z . Detection: read A y • Removing rx or wx from condition 2 misses fault • Fault D : Memory returns random result when D3 multiple cells read simultaneously. Generate fault by • Removing both writes misses faults C and D1 writing A x , Detection: read A w or A y ( or marches) 10/28/2014 21 10/28/2014 22 Irredundant March Tests Irredundant March Tests Irredundant March Test Irredundant March Test Summary Summary Algorithm Description MATS { (w 0); (r0, w 1); (r1) } MATS+ { (w 0); (r0, w 1); (r1, w 0) } CF Algorithm SAF AF TF CF CF SCF Linked MATS++ { (w 0); (r0, w 1); (r1, w 0, r0) } dyn in id Faults MARCH X { (w 0); (r0, w 1); (r1, w 0); (r0) } MATS All Some MARCH { { (w 0); (r0, w 1); (r1, w 0); ( ); ( , ); ( , ); MATS+ MATS+ All All All All C— (r0, w 1); (r1, w 0); (r0) } MATS++ All All All MARCH A { (w 0); (r0, w 1, w 0, w 1); (r1, w 0, w 1); MARCH X All All All All (r1, w 0, w 1, w 0); (r0, w 1, w 0) } MARCH C— All All All All All All All MARCH A All All All All Some MARCH Y { (w 0); (r0, w 1, r1); (r1, w 0, r0); (r0) } MARCH Y All All All All Some MARCH B { (w 0); (r0, w 1, r1, w 0, r0, w 1); MARCH B All All All All Some (r1, w 0, w 1); (r1, w 0, w 1, w 0); (r0, w 1, w 0) } 10/28/2014 23 10/28/2014 24 4

10/28/2014 March Test Complexity Neighborhood Pattern Sensitive Neighborhood Pattern Sensitive Coupling Faults Coupling Faults Algorithm Complexity MATS 4 n MATS+ 5 n MATS++ MATS++ 6 6 n MARCH X 6 n MARCH C— 10 n MARCH A 15 n MARCH Y 8 n MARCH B 17 n 10/28/2014 25 10/28/2014 26 RAM Organization RAM Organization Notation Notation • ANPSF -- Active Neighborhood Pattern Sensitive Fault • APNPSF – Active and Passive Neighborhood PSF • Neighborhood -- Immediate cluster of cells whose pattern makes base cell fail • NPSF -- Neighborhood Pattern Sensitive Fault • PNPSF -- Passive Neighborhood PSF • SNPSF -- Static Neighborhood Pattern Sensitive Fault 10/28/2014 27 10/28/2014 28 Type 1 Active NPSF Type 1 Active NPSF Type 2 Active NPSF Type 2 Active NPSF • Active : Base cell changes when one deleted neighborhood cell transitions • Used when diagonal couplings are significant, • Condition for detection & location : Each base and do not necessarily cause horizontal/vertical cell must be read in state 0 and state 1, for all coupling possible deleted neighborhood pattern changes. 10/28/2014 29 10/28/2014 30 5

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.