Overview Motivation ATPG Systems ECE 553: TESTING AND Fault - PDF document

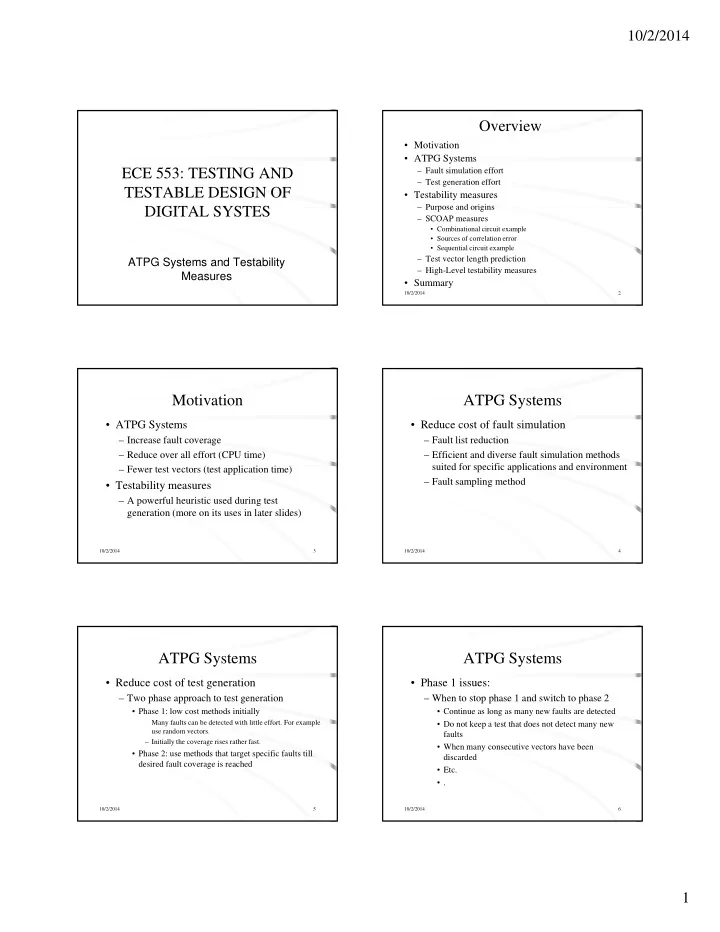

10/2/2014 Overview Motivation ATPG Systems ECE 553: TESTING AND Fault simulation effort Test generation effort TESTABLE DESIGN OF Testability measures Purpose and origins Purpose and origins DIGITAL SYSTES

10/2/2014 Overview • Motivation • ATPG Systems ECE 553: TESTING AND – Fault simulation effort – Test generation effort TESTABLE DESIGN OF • Testability measures – Purpose and origins – Purpose and origins DIGITAL SYSTES DIGITAL SYSTES – SCOAP measures • Combinational circuit example • Sources of correlation error • Sequential circuit example – Test vector length prediction ATPG Systems and Testability – High-Level testability measures Measures • Summary 10/2/2014 2 Motivation ATPG Systems • ATPG Systems • Reduce cost of fault simulation – Increase fault coverage – Fault list reduction – Reduce over all effort (CPU time) – Efficient and diverse fault simulation methods suited for specific applications and environment suited for specific applications and environment – Fewer test vectors (test application time) F ( li i i ) – Fault sampling method • Testability measures – A powerful heuristic used during test generation (more on its uses in later slides) 10/2/2014 3 10/2/2014 4 ATPG Systems ATPG Systems • Reduce cost of test generation • Phase 1 issues: – Two phase approach to test generation – When to stop phase 1 and switch to phase 2 • Phase 1: low cost methods initially • Continue as long as many new faults are detected – Many faults can be detected with little effort For example Many faults can be detected with little effort. For example • Do not keep a test that does not detect many new • Do not keep a test that does not detect many new use random vectors. faults – Initially the coverage rises rather fast. • When many consecutive vectors have been • Phase 2: use methods that target specific faults till discarded desired fault coverage is reached • Etc. • . 10/2/2014 5 10/2/2014 6 1

10/2/2014 ATPG Systems ATPG Systems • Phase 2 issues (during deterministic test • Efficient heuristics for backtrace generation): – Easy/hard heuristic – Efficient heuristics for backtrace • If many choices to meet an objective, and – What fault to pick next What fault to pick next satisfaction of any one of the choices will satisfy the satisfaction of any one of the choices will satisfy the objective – choose the easiest one first – Choice of backtrack limit • If all conditions must be satisfied to meet the desired – Switch heuristics objective, choose the hardest one first – Interleave test generation and fault simulation – Easy hard can be determined – Fill in x’s (test compaction) • Distance from Pis and Pos – Identify untestable faults by other methods • Testability measures 10/2/2014 7 10/2/2014 8 ATPG Systems ATPG Systems • Which fault to pick next • Choice of backtrack limit (High backtrack more time) – Target to generate tests for easy faults first • Hard faults may get detected with no extra effort • It has been observed that as the number of backtrack increases the success rate goes down.Thus we may increases the success rate goes down.Thus we may – Target to generate tests for hard faults first Target to generate tests for hard fa lts first wish to keep low backtrack limit. • Easy faults will be detected any way, why waste • Some faults may not get detected due to lack of time time spent on them – Target faults near PIs • Could start with low limit and increase it when – Target faults near POs necessary or in second round (often used heuristic) – etc. 10/2/2014 9 10/2/2014 10 ATPG Systems ATPG Systems • Switch heuristics • Fill in x’s (test compaction) – Switch between heuristics during backtrace as well as – Test generator generates vectors with some during backtrack inputs unspecified • Interleave test generation and fault simulation g • Can fill these values with random (0, 1) values • Can fill these values with random (0 1) values – Drop detected faults after generation of each test (often termed as dynamic compaction ). More on • This has higher switching cost but generally works well compaction on next three slides • This strategy may not be usable with certain fault simulators such as PPSFS • Sequential tests may not have other options and this may be the only practical option in some cases 10/2/2014 11 10/2/2014 12 2

10/2/2014 Static and Dynamic Compaction of Compaction Example Sequences • Static compaction • t 1 = 0 1 X t 2 = 0 X 1 – ATPG should leave unassigned inputs as X t 3 = 0 X 0 t 4 = X 0 1 – Two patterns compatible – if no conflicting values for any PI ∩ • Combine t 1 and t 3 , then t 2 and t 4 d d – Combine two tests t a and t b into one test t ab = t a C bi d i t b using D-intersection • Obtain: – Detects union of faults detected by t a & t b – t 13 = 0 1 0 t 24 = 0 0 1 • Dynamic compaction – Process every partially-done ATPG vector immediately • Test Length shortened from 4 to 2 – Assign 0 or 1 to PIs to test additional faults 10/2/2014 13 10/2/2014 14 ATPG Systems Test Compaction • Identify untestable faults by other methods • Fault simulate test patterns in reverse order of – If the goal is to identify only untestable faults generation as opposed to find a test, some other methods – ATPG patterns go first may do a better job example of such may do a better job – example of such – Randomly-generated patterns go last (because they Randomly generated patterns go last (because they may have less coverage) techniques are: – When coverage reaches 100%, drop remaining • Recursive learning patterns (which are the useless random ones) • Controllability evaluations – Significantly shortens test sequence – economic cost • etc. reduction 10/2/2014 15 10/2/2014 16 ATPG Systems Fault Coverage and Efficiency Circuit Fault Compacter Description List # of detected faults Fault coverage = Total # faults Test generator Test generator Aborted Aborted Test With fault Fault Faults # of detected faults Patterns = simulation Total # faults -- # undetectable faults efficiency Backtrack Undetected Redundant Faults Distribution Faults 10/2/2014 17 10/2/2014 18 3

10/2/2014 Testability Analysis - Purpose Origins Origins • Control theory • Need approximate measure of: • Rutman 1972 -- First definition of controllability – Difficulty of setting internal circuit lines to 0 or 1 by • Goldstein 1979 -- SCOAP setting primary circuit inputs – Difficulty of observing internal circuit lines by observing – First definition of observability primary outputs – First elegant formulation • Uses: U – First efficient algorithm to compute controllability and observability – Analysis of difficulty of testing internal circuit parts – redesign or add special test hardware • Parker & McCluskey 1975 – Guidance for algorithms computing test patterns – avoid – Definition of Probabilistic Controllability using hard-to-control lines • Brglez 1984 -- COP – Estimation of fault coverage – 1 st probabilistic measures – Estimation of test vector length • Seth, Pan & Agrawal 1985 – PREDICT – 1 st exact probabilistic measures 10/2/2014 19 10/2/2014 20 Types of Measures Testability Analysis - Constraints SCOAP – Sandia Controllability and Observability Analysis Involves Circuit Topological analysis, but no Program Combinational measures: test vectors and no search algorithm Static analysis CC0 – Difficulty of setting circuit line to logic 0 Linear computational complexity CC1 CC1 – Difficulty of setting circuit line to logic 1 Otherwise, is pointless – might as well use Diffi l f i i i li l i 1 CO – Difficulty of observing a circuit line automatic test-pattern generation and Sequential measures – analogous: calculate: Exact fault coverage SC0 Exact test vectors SC1 SO 10/2/2014 21 10/2/2014 22 Range of SCOAP Measures Goldstein’s SCOAP Measures Goldstein’s SCOAP Measures AND gate O/P 0 controllability: Controllabilities – 1 (easiest) to infinity (hardest) output_controllability = min (input_controllabilities) Observabilities – 0 (easiest) to infinity (hardest) + 1 AND gate O/P 1 controllability: Combinational measures: output_controllability = Σ Σ (input_controllabilities) – Roughly proportional to # circuit lines that must be set to + 1 control or observe given line Sequential measures: XOR gate O/P controllability output_controllability = min (controllabilities of – Roughly proportional to # times a flip-flop must be clocked each input set) + 1 to control or observe given line Fanout Stem observability: Σ or min (some or all fanout branch observabilities) 10/2/2014 23 10/2/2014 24 4

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.