Overview Motivation and introduction Structure independent - PDF document

10/23/2014 Overview Motivation and introduction Structure independent approach ECE 553: TESTING AND Structure dependant approach TESTABLE DESIGN OF Organization/architecture dependant DIGITAL SYSTES DIGITAL SYSTES approach

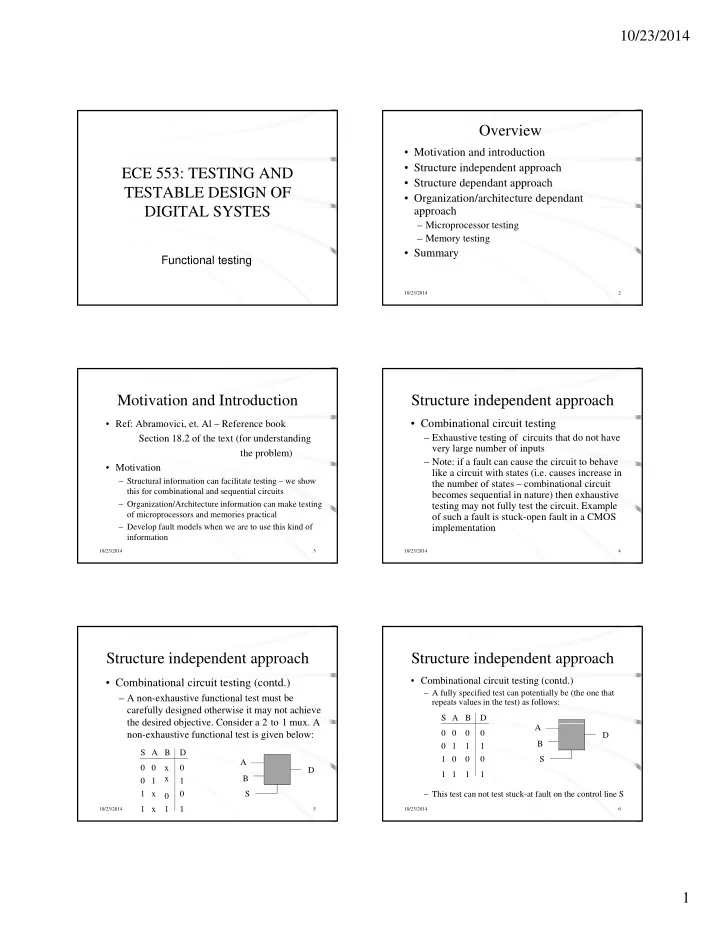

10/23/2014 Overview • Motivation and introduction • Structure independent approach ECE 553: TESTING AND • Structure dependant approach TESTABLE DESIGN OF • Organization/architecture dependant DIGITAL SYSTES DIGITAL SYSTES approach h – Microprocessor testing – Memory testing • Summary Functional testing 10/23/2014 2 Motivation and Introduction Structure independent approach • Ref: Abramovici, et. Al – Reference book • Combinational circuit testing – Exhaustive testing of circuits that do not have Section 18.2 of the text (for understanding very large number of inputs the problem) – Note: if a fault can cause the circuit to behave • Motivation M ti ti like a circuit with states (i.e. causes increase in – Structural information can facilitate testing – we show the number of states – combinational circuit this for combinational and sequential circuits becomes sequential in nature) then exhaustive – Organization/Architecture information can make testing testing may not fully test the circuit. Example of microprocessors and memories practical of such a fault is stuck-open fault in a CMOS – Develop fault models when we are to use this kind of implementation information 10/23/2014 3 10/23/2014 4 Structure independent approach Structure independent approach • Combinational circuit testing (contd.) • Combinational circuit testing (contd.) – A fully specified test can potentially be (the one that – A non-exhaustive functional test must be repeats values in the test) as follows: carefully designed otherwise it may not achieve S A B D the desired objective. Consider a 2 to 1 mux. A the desired objective Consider a 2-to-1 mux A A 0 0 0 0 non-exhaustive functional test is given below: D B 0 1 1 1 S A B D 1 0 0 0 S A 0 0 x 0 D 1 1 1 1 x B 0 1 1 1 x 0 S – This test can not test stuck-at fault on the control line S 0 1 x 1 1 10/23/2014 5 10/23/2014 6 1

10/23/2014 Structure independent approach Structure dependant approach • Sequential circuit testing • Combinational circuit testing – An example of this method and its limitations – Structure can potentially provide the has been discussed in detail in the checking information about dependence of outputs on experiment approach to testing experiment approach to testing inputs This leads to two methods of structure inputs. This leads to two methods of structure dependant functional testing • Pseudo-exhaustive testing • Sensitized partition testing 10/23/2014 7 10/23/2014 8 Structure dependant approach Structure dependant approach • Pseudo-exhaustive testing • Sensitized partition testing – Testing an ALU – control signals are • The circuit will require 128 A B C D E F G patterns for exhaustive determined and applied in such a way that each testing smaller part (say 4 bit ALU) is exhaustively smaller part (say 4-bit ALU) is exhaustively • Function description may tested not tell us the dependence of the output on partial – An example from the book by Abramovici et. input set al. • Both f 1 and f 2 can be tested exhaustively with 16 pattern each, thus requiring a total of 32 patterns f 1 f 2 10/23/2014 9 10/23/2014 10 Structure dependant approach Organization/architecture dependant approach • Sequential circuit testing • In many cases architecture and/or – Testing iterative logic arrays organization information is available and – Machine partitioning approach to testing such information can be used to facilitate • Substantial literature in this area but has not been Substantial literature in this area but has not been testing We will show two applications of testing. We will show two applications of applied to real applications of today such an approach – An example – testing of shift register A simple test 0 1 1 0 0 x x x x x … can test the shift register completely. This test is often used in testing “scan chains” to be discussed under DFT and BIST methods 10/23/2014 11 10/23/2014 12 2

10/23/2014 Microprocessor testing Microprocessor testing • Basic concept • References – Need to develop test programs that can be executed on – Reference book – Abramovici et. Al. the processor – Thatte and Abraham, “Test generation of – Need an open loop strategy to force instructions in the microprocessors” IEEE Transactions on microprocessors , IEEE Transactions on order we wish to execute – e.g. after a jump instruction Computers, June 1980, pp. 429-441 we may wish to execute an instruction from an address different from the address provided by jump instruction – Develop a model (or models) for faults in different organizational sub-units of the microprocessor 10/23/2014 13 10/23/2014 14 Microprocessor testing Microprocessor testing • What do we know? • Method – Different sub-units – Test each instruction • Register file, bus, ALU, memory (cache), … – Test each subunit such as ALU – How instructions are executed – Test busses • How data moves from sub-unit to other subunit – Test register file and decoders • Data movement from and to the external world – Test sequencing of instructions – Sequencing and timing • Key concept • Number of clocks, atomic and semi-atomic actions, – Start small – test components and instructions that are e.g. PUSH – causes increment PC, send SP as easy to test and then use the tested parts to test other address, send register as data, increment SP, etc. parts 10/23/2014 15 10/23/2014 16 Microprocessor testing Microprocessor testing • Model development • Fault model development – Determine which instructions are “easy” to execute – – Busses: stuck-at and bridging faults such as used fewest resources, fewest cycles – easy to – ALU: stuck-at (assume that the structural information is control and observe (graph model) available) – Use such instructions to read and write register file to – Register file: stuck-at, arbitrary decoder failure – this test register file(s) and address decoding logic will use similar fault model and tests as used for testing – Test busses by moving different types of data on busses memories – Test ALU by executing ALU related instructions such – Instruction decoder: as ADD, SUB, … • No instruction is executed (I j / φ ) • Different instruction is executed (I j /I k ) • An additional instruction is also executed (I j /I j +I k ) 10/23/2014 17 10/23/2014 18 3

10/23/2014 Microprocessor testing Microprocessor testing • Results (case study on an 8-bit HP processors) • Algorithm development – Program size 1K – FC about 90% – Develop simple sub-programs for each sub-unit – Additional complexities introduced in the test program (8K testing program) raised the coverage by 6% – Other faults were associated with the power-up logic intialization – Other faults were associated with the power-up logic, intialization, – Put them together Put them together interrupts, … (hard to test by functional tests) – Testing jumps and call will require intervention • Limitations of tester – open loop strategy of testing – Lack of good and practical model of modern microprocessors microprocessor – Automating the program generation difficult and impractical – Structural methods with the use of DFT provide better coverage with fewer test vectors 10/23/2014 19 10/23/2014 20 Memory testing Summary • Basic reasoning • Described structure independent and structure – Logic design methods may not be applicable dependent methods of testing logic • Special design methods • Not designed using logic gates • Microprocessor testing using organization – Cutting edge technology Cutting edge technology information – model, fault model, test • High density algorithms, results and limitations • Novel and non-traditional design methods and layout – Can be stand alone or embedded • Memory testing – its need • Need to develop – Model, fault model and test algorithms to be – Fault model discussed next – Test algorithms 10/23/2014 21 10/23/2014 22 4

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.