Outline Introduction. Paper: System Design for Ultra-Low Power. - PowerPoint PPT Presentation

Paper presentation Ultra-Portable Devices Outline Introduction. Paper: System Design for Ultra-Low Power. Bernier, C. Hameau, F., et al. An Ultra Low Power SoC for 2.4GHz IEEE802.15.4 wireless communications , Solid-State Circuits

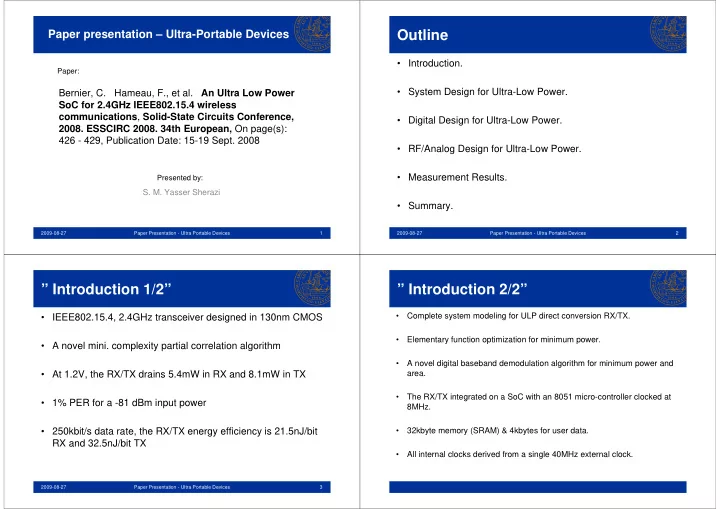

Paper presentation – Ultra-Portable Devices Outline • Introduction. Paper: • System Design for Ultra-Low Power. Bernier, C. Hameau, F., et al. An Ultra Low Power SoC for 2.4GHz IEEE802.15.4 wireless communications , Solid-State Circuits Conference, • Digital Design for Ultra-Low Power. 2008. ESSCIRC 2008. 34th European, On page(s): 426 - 429, Publication Date: 15-19 Sept. 2008 • RF/Analog Design for Ultra-Low Power. • Measurement Results. Presented by: S. M. Yasser Sherazi • Summary. 2009-08-27 Paper Presentation - Ultra Portable Devices 1 2009-08-27 Paper Presentation - Ultra Portable Devices 2 ” Introduction 1/2” ” Introduction 2/2” • Complete system modeling for ULP direct conversion RX/TX. • IEEE802.15.4, 2.4GHz transceiver designed in 130nm CMOS • Elementary function optimization for minimum power. • A novel mini. complexity partial correlation algorithm • A novel digital baseband demodulation algorithm for minimum power and • At 1.2V, the RX/TX drains 5.4mW in RX and 8.1mW in TX area. • The RX/TX integrated on a SoC with an 8051 micro-controller clocked at • 1% PER for a -81 dBm input power 8MHz. • 250kbit/s data rate, the RX/TX energy efficiency is 21.5nJ/bit • 32kbyte memory (SRAM) & 4kbytes for user data. RX and 32.5nJ/bit TX • All internal clocks derived from a single 40MHz external clock. 2009-08-27 Paper Presentation - Ultra Portable Devices 3

’’SOC Architecture’’ ”System Design for ULP” • Spreading of the 250kbps data stream into a 2Mchip/s • Mapping 4-bit symbol onto one of 16 quasi-orthogonal Seq. • 32-chip pseudo-random sequences. • Chip stream is modulated using O-QPSK • Digital part of receiver, half of the spreading codes are complex conjugates. • Reduced Correlation algorithm. ”System Design for ULP” ’’32-chip (GC) vs 8 4-chip (PC)’’ Implementation (Digital) • Eight non-coherent 4-chip partial correlations. • Rather than a single 32 chip correlation. • Well suited for ULP. • Most Complex calculation is square • Most Multiplications are by + 1.

”System Design for ULP” ’’ Simulated PER vs. Input Power ’’ Implementation (Analog) • Information in sign of baseband I and Q signal. • Non-linear amplification used in analog RX chain. • Reduced resolution and low sampling rate ADC. • ADC’ sampling rate 4MS/s and 3-bit dynamic range. • Drastic reduction of consumption of RX/TX digital operator. ”Digital Design for ULP” ’’Digital RX Architecture’’ • Packet format for IEEE802.15.4 • 8 consective 0 symbols. • Start Frame Delimiter (SFD). • PBY Header (length of PSDU). • PSDU is the payload.

’’Partial Correlation Algorithm’’ ’’ Architecture of PC bank’’ • For each symbol period, the received symbol is: = max( _ ( )), 0 ,.., 15 corr out n N with ⎛ ⎞ 2 7 3 ∑ ∑ ⎜ ⎟ = × n * corr _ out ( n ) s ( c ) ⎜ ⎟ + + 4 p k 4 p k ⎝ ⎠ = = p 0 k 0 • where s m is the m th complex signal sample (of 32) and c n m is the m th complex chip (of 32) of the n th spreading code (of 16). ’’ Generation of Spreading Codes’’ ’’RF/Analog Design for ULP’’ • Direct Conversion reciever architecture. • Bandwidth of baseband chain is minimized. • Amplifier’s outout impedence can be increased. • Its bias current is decreased withot sacrificing gain. • Transistors can be biased in weak inversion. • At weak inversion gm/Ids ratio is highest.

’’ 2.4-GHz Transceiver’’ ’’Measurement Results’’ • State of the art transceivers (250 KBit/S). ’’ Measured Digital RX current ’’Measurement Results’’ consumption (PSDU = 20 bytes)’’ • Measured Consumption Per Block

’’ Die Photograph (130nm CMOS) ’’ ’’ Picture of Demonstration Board ’’ • 4mm 2 Digital, 5mm 2 Analog Circit area. ”Summary” ”Papers to Look into” • High-level system modeling. • W. Kluge et al., “A Fully Integrated 2.4-GHz IEEE802.15.4 Compliant Transceiver for ZigBeeTM Applications,” IEEE JSSC,Vol. 41, NO. 12, Dec. 2006, pp 2767-2775. • High-level system simulation. • H. Ishizaki, K. Nose, M. Mizuno, “A 2.4GHz ISM-band digital • It is at the architectural level that most power is saved. wireless transceiver with an intra-symbol adaptively intermittent RX,” 2007 IEEE Symposium on VLSI Circuits Dig. • Through high-level simulations that the impact of each. Tech. Papers, pp. 84-85. • Minimizes complexity in Algorithms. 2009-08-27 Paper Presentation - Ultra Portable Devices 23

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.