Outline Interconnect scaling issues Aluminum technology Copper - PDF document

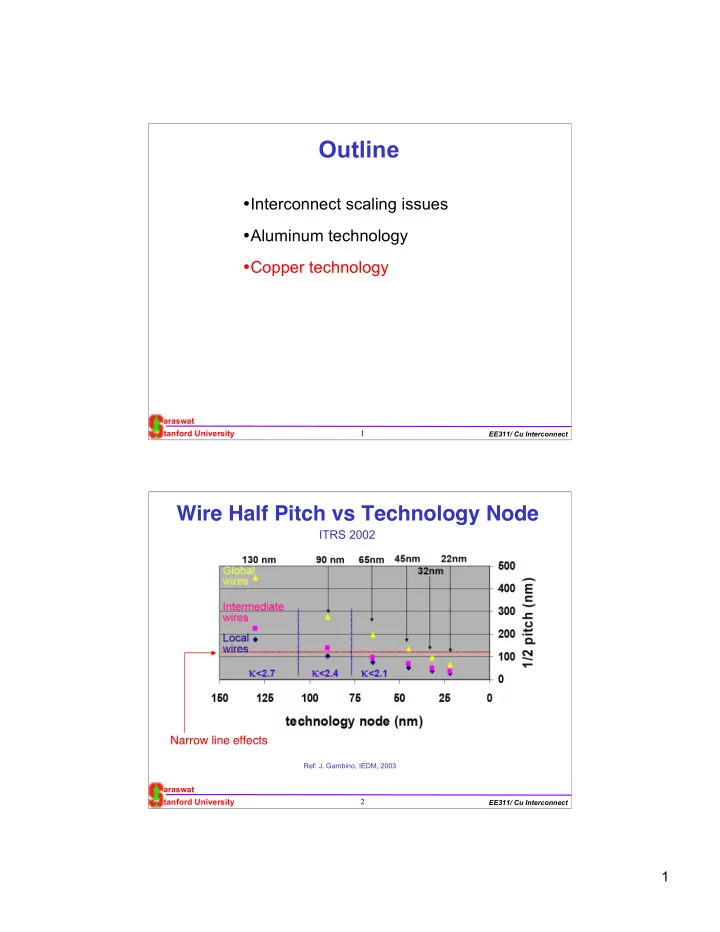

Outline Interconnect scaling issues Aluminum technology Copper technology araswat tanford University 1 EE311/ Cu Interconnect Wire Half Pitch vs Technology Node ITRS 2002 Narrow line effects Ref: J. Gambino, IEDM, 2003 araswat

Outline • Interconnect scaling issues • Aluminum technology • Copper technology araswat tanford University 1 EE311/ Cu Interconnect Wire Half Pitch vs Technology Node ITRS 2002 Narrow line effects Ref: J. Gambino, IEDM, 2003 araswat tanford University 2 EE311/ Cu Interconnect 1

Interconnect Scaling Scenarios 1 Scale Metal Pitch with Constant Height • C S1 1 - R, C s and J increase by scaling factor A 1 1 - Higher aspect ratio for gapfill / metal etch A 1 /S SC S1 - Need for lower resistivity metal, Low-k 1 Scale Metal Pitch and Height • 0.5 0.5 - R and J increase by square of scaling factor 1 C S1 - Sidewall capacitance unchanged 1 A 1 - Aspect ratio for gapfill / metal etch unchanged 1 A 1 /S 2 - Need for very low resistivity metal with C S1 significantly improved EM performance 0.5 0.5 0.5 araswat tanford University 3 EE311/ Cu Interconnect Why Cu and Low-k Dielectrics? Low ρ (Resistivity) Reduced RC delay 50 Metal 40 Bulk Resistivity [ µΩ •cm] Ag 30 1.63 Al+SiO 2 Cu 1.67 20 Dealy Time (psec) Total Delay Au 2.35 Cu+Low-k(2.0) Al 2.67 Total Delay Gate Delay W 10 5.65 9 8 7 6 Cu is the second best conducting element 5 4 � RC � K ox � o � L 2 � � W + H 3 Al+SiO 2 � � Cu+Low-k(2.0) Interconnect Delay WH X ox L S Interconnect Delay � � 2 0.1 0.2 0.3 0.4 0.5 0.6 � K ox � o � L 2 Feature Size (µm) � 2 for W = H = L S = X ox = � Calculations assume longest interconnect in the chip controls delay araswat tanford University 4 EE311/ Cu Interconnect 2

Why Cu and Low-k Dielectrics? 14 global 12 Al/SiO 2 Number of Metal Layers 10 Al/Low-k Cu/SiO 2 8 semiglobal 6 Cu/Low-k local 4 2 Ref: M. Bohr, IEDM 1995 . 0 0.09 0.13 0.18 0.25 0.35 Technology Generation (µm) Better electromigration resistance, reduced resistivity and dielectric constant results in reduction in number of metal layers as more wires can by placed in lower levels of metal layers. araswat tanford University 5 EE311/ Cu Interconnect Why Cu?: Excellent Reliability Al Cu high Melting Point 660 ºC 1083 ºC electromigration E a for Lattice Diffusion 1.4 eV 2.2 eV E a for Grain Boundary 0.4 – 0.8 eV 0.7 – 1.2 eV resistance Diffusion J = 2.5x10 6 A/cm 2 T = 295°C > 110X Percentile Ref: S. Luce, (IBM), IEEE IITC 1998 Al(Cu) Cu T 50 = 1.31 Hrs T 50 = 147.7 Hrs Stress Time (hours) araswat tanford University 6 EE311/ Cu Interconnect 3

Problem : Copper Diffusion in Dielectric Films Cu atoms ionize, penetrate into the dielectric, and then accumulate in the dielectric as Cu+ space charge. araswat tanford University 7 EE311/ Cu Interconnect Copper Diffusion in Dielectric Films Bias temperature stressing is employed to characterize behavior • Both field and temperature affect barrier lifetime • Neutral Cu atoms and Cu ions contribute to Cu transport through dielectrics Ref: A. Loke et al., Symp. VLSI Tech. 1998 Silicon nitride and oxynitride films are better barriers araswat tanford University 8 EE311/ Cu Interconnect 4

Solutions to Problems in Copper Metallization • Fast diffusion of Cu into Si and SiO 2 Dielectrics • Poor oxidation/corrosion resistance • Poor adhesion to SiO 2 Barrier Layer Diffusion barrier /adhesion promotor Passivation Cu • Difficulty of applying conventional dry-etching technique Damascene Process Typical Damascene Process araswat tanford University 9 EE311/ Cu Interconnect Barriers/Linears Barrier/Linear Space for wire Via Dielectric Metal araswat tanford University 10 EE311/ Cu Interconnect 5

Materials for Barriers / Liners • Transition metals (Pd, Cr, Ti, Co, Ni, Pt) generally poor barriers, due to high reactivities to Cu <450˚ C . Exception: Ta, Mo, W ... more thermally stable, but fail due to Cu diffusion through grain boundaries (polycrystalline films) • Transition metal alloys: e.g., TiW. Can be deposited as amorphous films (stable up to 500˚C) • Transition metal - compounds: Extensively used, e.g., TiN, TaN, WN. • Amorphous ternary alloys: Very stable due to high crystallization temperatures (i.e., Ta 36 S 14 ,N 50 , Ti 34 Si 23 N 43 ) • Currently PVD (sputtering/evaporation is used primarily to deposit the barrier/liner, however, step coverage is a problem. ALD is being developed for barrier/liner application. ALD PVD araswat tanford University 11 EE311/ Cu Interconnect Interconnect Fabrication Options Positive Negative Pattern Pattern Metal Dielectric Etch Etch Metal Dielectric Deposition Deposition Metal Dielectric Metal CMP Photoresist Etch Stop Dielectric (Dielectric) Planarization Dielectric by CMP Deposition Subtractive Etch Damascene (Conventional Approach) araswat tanford University 12 EE311/ Cu Interconnect 6

Cu Damascene Flow Options Single Damascene Dual Damascene Via Via & Pattern Lead & Etch Pattern & Etch Barrier & Cu Dep Barrier & Cu Cu Via Dep CMP Nitride + Oxide Dep Lead Cu CMP Via Lead Pattern & Etch + Barrier & Cu Dep Oxide Copper Cu Lead Lead CMP Conductive Barrier Via Dielectric Etch Stop/Barrier araswat tanford University 13 EE311/ Cu Interconnect Deposition methods of Cu films: PVD Various deposition methods for Cu metallization has been attempted : Physical vapor deposition (PVD) : Evaporation, Sputtering • conventional metal deposition technique: widely used for Al interconnects • produce Cu films with strong (111) texture and smooth surface, in general • poor step coverage: not tolerable for filling high-aspect ratio features Deposited film araswat tanford University 14 EE311/ Cu Interconnect 7

Deposition methods: CVD conformal deposition with excellent step coverage in high-aspect ratio holes and vias • costly in processing and maintenance • generally produce Cu films with fine grain size, weak (111) texture and rough surface araswat tanford University 15 EE311/ Cu Interconnect Deposition methods: Electroplating Copper electroplating Chemistry : Plating Bath : standard sulfuric acid copper sulfate bath (H 2 SO 4 , CuSO 4 solution) Additives to improve the film quality Dissociation : CuSO 4 → Cu 2+ + SO 42- (solution) Cu → Cu 2+ + 2e - (anode) Oxidation : Reduction : Cu 2+ + 2e - → Cu (cathode, i.e., wafer) araswat tanford University 16 EE311/ Cu Interconnect 8

Why Cu Electroplating? Electrochemical deposition (EVD) Good step coverage and filling capability comparable to CVD process (0.25 µ m) Compatible with low-K dielectrics Generally produce strong (111) texture of Cu film Produce much larger sized grain structure than any other deposition methods through self-annealing process araswat tanford University 17 EE311/ Cu Interconnect Trench Filling PVD vs. Electroplating of Cu "bottom-up filling" non-conformal ("superfilling") void PVD Electroplating araswat tanford University 18 EE311/ Cu Interconnect 9

Plated Copper Fill Evolution Seed only 5 seconds 10 seconds 15 seconds 25 seconds Ref: Jonathan Reid, IITC, 1999 araswat tanford University 19 EE311/ Cu Interconnect Trench Filling Capability of Cu Electroplating 029 µ vias 0.18 µ vias 0.13 µ trenches Ref: Jonathan Reid, IITC, 1999 araswat tanford University 20 EE311/ Cu Interconnect 10

Additives for Copper ECD DEFINITION • Mixture of organic molecules and chloride ion which are adsorbed at the copper surface during plating to: -- enhance thickness distribution and feature fill -- control copper grain structure and thus ductility, hardness, stress, and surface smoothness COMPONENTS • Most commercial mixtures use 3 or more organic components and chloride ion which adsorb at the cathode during plating. Brighteners ( Accelerators) Levelers Carriers Chloride Suppressors araswat tanford University 21 EE311/ Cu Interconnect Mechanisms of Superconformal Cu plating = Accelerators = Suppressors t = 0 sec t = 2 sec c = Chloride ions L = Levelers Wafers immersed in plating Additives adsorbed on Cu bath. Additives not yet seed. No current flow. adsorbed on Cu seed. t = 10 sec t = 20 sec Conformal plating begins. Accumulation of accelerator Accelerators accumulate at due to reduced surface area in bottom of via, displacing less narrow features, causes rapid strongly absorbed additives. growth at bottom of via. Ref: J. Reid et al., Solid St. Tech., 43, 86 (2000) D. Josell et al., J. Electrochem. Soc., 148, C767 (2001) araswat tanford University 22 EE311/ Cu Interconnect 11

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.