Nanocrystal embedded MOS non volatile memory devices Prof. C. K. - PowerPoint PPT Presentation

Nanocrystal embedded MOS non volatile memory devices Prof. C. K. Sarkar, Senior Member, IEEE IEEE EDS Distinguished Lecturer Professor Dept. of Electronics & Telecommunication Engineering Jadavpur University Kolkata-700032 , INDIA

Nanocrystal embedded MOS non volatile memory devices Prof. C. K. Sarkar, Senior Member, IEEE IEEE EDS Distinguished Lecturer Professor Dept. of Electronics & Telecommunication Engineering Jadavpur University Kolkata-700032 , INDIA Phone/Fax: +91-33-24146217 E-mail: phyhod@yahoo.co.in http://www.jaduniv.edu.in http://www.ndslju.org

2

Nanotechnology: A Revolutionary Concept “ T The here’s pl plent nty of r room a at t the he bot ottom om” -Richard P. Feynman (Caltech, 29.12.1959) Today Nanotechnology is a vast Inter-disciplinary Field 3

The applications of Nanotechnology are numerous Source: ht http: p://lib.bi bioinfo.pl pl/bl blid:1739 Nano-electronics holds a major share in this Source: NAT ATIONAL AL S SCIENCE F FOUNDAT ATION, USA 4

MOS Memory Devices USB Flash drives Memory cards (SD,MMC,M2) used in mobile phones, digital cameras, MP3 players Computer DRAMs, Solid State Hard Drives (HDD) They are & many more everywhere 5

Various MOS Memory Devices FeRAM, MRAM, PRAM RAM DRAM MOS SDRAM PROM Memory ROM • EEPROM • FLASH • EPROM MROM Ref: A. Sengupta, C.K. Sarkar, The 4 th IEEE International NanoElectronics Conf. (IEEE 6 INEC ), June 21-24, 2011, Taiwan

7

1991 1992 1993 Flash Memory Market 1994 Growth (NAND & NOR) 1995 1996 Data Source: WSTS & IC Insights 1997 1998 Year 1999 2000 2001 2002 2003 2004 2005 2006 0 5000 10000 15000 20000 Flash Memory Market (USD mn) 8

Transistors per die of MOS Memory Devices 9

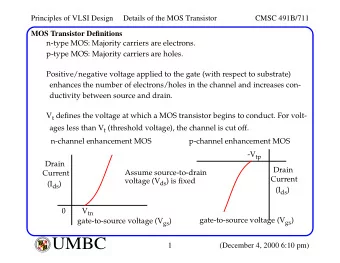

MOSFET memory and MOS capacitors MOSFET memory devices rely on charge stored in the Floating Gate to cause a shift in the threshold/ flatband voltage. Campardo e o et. a al. VLSI Design of of N Non on-Volatile M Memories, s, Springer V Verlag, Berlin H Heidelberg 2005, 2005, p pp. 50 50 10

Conventional MOS NVMs : Floating gate & SONOS Charges are stored in the polysilicon Floating Gate. Most commonly used for Flash memory applications. Charges are stored in the Oxide-Nitride interface. Another variant MNOS useful for Aerospace/Military applications. 11

12

Disadvantage of conventional MOS Memory Devices With scaling and thinner tunnel oxides, leakage provides a major challenge. Also for portability lesser write voltages are required. Advantages of Nanotechnology may be applied to MOS devices. Nanocrystal embedded MOS NVMs can help in this regard. 13

130 nm 2001 Courtesy : Prof. Jakub Kedz dzierski IIT IIT-Bomba bay/ MIT IT Linc ncoln n Lab ~100 A gate Roa oad-bloc ock: Ga Gate o oxide leakage ~0.1 A gate tunne nneling ng current nt, t the he leakage quantum n nature o of matter let ets el elect ectrons pen enet etrate e the e gate ox oxide 14

Nanoparticles Based Floating Gate MOS Memory Structure Nanoparticles(nc) diameter in 5-6nm range. Confined in a narrow layer within SiO 2 called embedded gate dielectric Charging and discharging of nc carried out by electron tunneling Electrons tunnel from Si substrate to gate electrode through gate dielectric A thin tunneling barrier is formed at the interface of silicon substrate and composite gate dielectric Comparison of nc-Si and nc-Ge Nanoparticles embedded embedded gate oxide MOS devices. floating gate MOSFET and MOSCAP 15

Write/Erase mechanism of such a device 16

Advantages of Nanocrystal embedded MOS NVM 17

18

Metallic Nanocrystals Use of Metallic nanocrystals like Ni, W, Ag, Au, Pt ncs. Lee et. a al. J J E Electron M Mater. 34, 1-11, 11, 2005. 2005. Lee e et. al. IEEE TED 52, 52,4, 4,507 ( 507 (2005) 2005) Better charge s storage , L Lesser l leakage, improved r retention 19

CNT/ C60 embedded MOS NVM [T-H. H Hou e et. a al. D Device Rese search Conference, 2008, Issu ssue D Date: 23-25 25 June 2008 2008 pp.275 275 - 276 276 [X. B B. Lu a and J. Y Y. D Dai, Applied P Physics L Letters, v vol. 8 88, n no. 1 11, p p. 1 113104, 2 2006.] 20

Stacked High-k gate dielectrics • High-k materials help in suppressing the leakage. They have better • Yang et. al. Nanotechnology 21 (2010) 245201 charge retention then SiO 2 gate dielectrics. • Better Program / Erase cycles endurance. Lo e et. a al. l. A APPLIED PHYSI SICS L S LETTERS S 94, 082901 082901 2009] 2009] 21

Compound semiconductor MOSFET • Compound semiconductors like In x Ga 1-x As, GaN, InP, GaAs have better MOSFET performance than conventional Si or strained Si MOS. • Such compound semiconductor MOS can be used for memory applications as well. P. D. Y Ye et a alApplied Physics L Letters, v vol. 8 84, no. 3, 3, p p. 434, 434, 2004. 2004. Kalna e et. al. Semicond. Sci. Technol. 1 19 S202 202-S205 ( 205 (2004) 2004) 22

Multigate MOS NVM structures Yeom e et. a al. Nanotechnology 19 ( 9 (2008) 2008) 395204 395204 S. O Oh, J J. Kor. Phys. S Soc., 5 55, 1, 2 263, 2009 H-B. . Chen e et. . al., ., IE IEEE E Electron D Dev. . Lett., ., 32, 10, 32, 0, 1 1382 382 (201 2011) M.F. Hung, Applied Physics Letters, 98, 98, 1 1621 62108, 08, 2011 23

24

Why Modeling? • Many device structures, many materials in terms of the embedded NCs and the substrate materials. • Fabrication and testing is costly, time-consuming and requires infrastructure and manpower. • A good model can thus act as a pointer in the right direction well before the actual fab is carried out. 25

Need for New Simulations Standard device simulators like Sentaurus, Silvaco • TCAD do not incorporate nanocrystal embedded MOS NVMs. • Existing models are either involving a large amount of numerical solutions and rather complex iterative orthogonalization and extraction methods for 3D Kohn-Sham / Poisson-Schrodinger equations. • No analytical models for advanced multi-gate nc embedded gate dielectric MOSFET NVMs. 26

Write Mechanism: Fowler – Nordheim Tunneling High Applied Gate voltage Fowler- Nordheim tunneling The barrier becomes Triangular in shape Applied gate voltage Electrons tunnel from the conduction band of Si to conduction band of oxide through part of potential barrier Band diagram of Fowler-Nordheim tunneling 27

Band Structure of Tunneling under Different Conditions of Applied Electric Field Band bending at applied electric fields under different conditions (a) (b) (c) 28

F-N Tunneling Probabilty ( ) Case I : < φ − qF d E eff eff o 4 2 m ( ) ( ) ( ) ( ) 4 2 m 3/2 3/2 3/2 = − φ − − φ − − − φ − − eff D E exp E E qF d E qF d eff 0 eff 0 eff 0 eff 0 3 q F 3 q F eff ( ) ( ) Case II : φ − < < φ − E qF d E eff o eff o ) { } − ( 1 = θ θ − θ + θ θ + θ + 2 2 2 2 D E sin cosh ( ) cos cosh ln(4) 2 3 1 2 3 1 0 { } 1/2 x i ( ) ∫ θ = − * 2 m V x E dx i 0 x − i 1 ( ) Case III : > φ − qF d E eff o 4 2 m ( ) 3/2 = − φ − eff D E ( ) exp E 0 eff 0 3 q F eff 29

Leakage: Direct Tunneling Low Applied Gate voltage Direct tunneling Applied gate voltage condition The Barrier becomes Trapezoidal in shape Electrons tunnel directly from Si conduction band to metal instead of through oxide conduction band Band diagram for direct tunneling { } ( ) ( ) 1/2 φ − α α φ − 2 2 m E q V 2 2 m E eff eff 0 eff eff 0 = J exp d D 2 d 30

Parameters changed due to inclusion of Nanoparticles Dielectric constant of SiO 2 embedded with nc-Si determined by using Maxwell-Garnett Effective Medium Approximation (EMA) { } ( ) ( ) − ∈ ν ∈ −∈ + ∈ + ∈ 1 − 2 2 t t t ∈ = + ∈ = ox nc ox nc ox ox ox ( ) ∈ ⋅ ∈ ⋅ − ∈ + ∈ − ν ∈ −∈ eff nc ox t t 2 − ox nc ox nc ox nc ox Band gap energy has been modified π + 2 2 1 1 = + E E gnc bulk 2 * * 2 R m m h e Effective barrier height modified E ( ) 1 1 φ = + ⋅ − + ⋅ − gsio 2 E (1 v ) v E E eff gsio 2 gnc gsi 2 2 2 Electron effective mass has been changed − m d m ( d d ) = + sio 2 sio 2 nc sio 2 m eff d d 31

Simulated Fowler-Nordheim Plot FN plot compares the pure SiO 2 gate dielectric with the nc- Si and the nc-Ge embedded dielectric. Both The nanoparticles embedded composite gate dieletrics show higher F-N tunneling current density than the pure SiO 2 dielectric. The F-N tunneling current density is higher in nc-Ge embedded gate dielectric than the nc-Si embedded one. Ref: G. Chakraborty, A. Sengupta, F.G. Requejo, C.K. Sarkar, J. Appl. Phys., 109, 064504 (2011). 32

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.