Multi-level Coarsening Algorithm Perform Edge Coarsening (EC) Visit - PowerPoint PPT Presentation

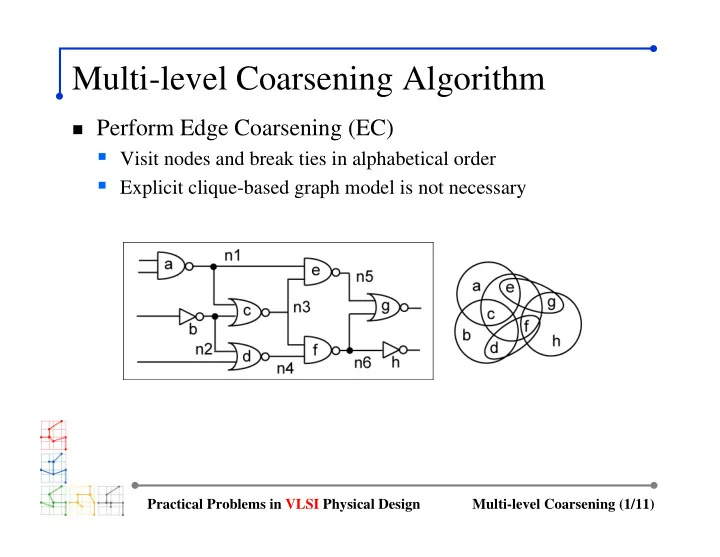

Multi-level Coarsening Algorithm Perform Edge Coarsening (EC) Visit nodes and break ties in alphabetical order Explicit clique-based graph model is not necessary Practical Problems in VLSI Physical Design Multi-level Coarsening (1/11)

Multi-level Coarsening Algorithm � Perform Edge Coarsening (EC) � Visit nodes and break ties in alphabetical order � Explicit clique-based graph model is not necessary Practical Problems in VLSI Physical Design Multi-level Coarsening (1/11)

Edge Coarsening Practical Problems in VLSI Physical Design Multi-level Coarsening (2/11)

Edge Coarsening (cont) Practical Problems in VLSI Physical Design Multi-level Coarsening (3/11)

Obtaining Clustered-level Netlist � # of nodes/hyperedges reduced: 4 nodes, 5 hyperedges Practical Problems in VLSI Physical Design Multi-level Coarsening (4/11)

Hyperedge Coarsening � Initial setup � Sort hyper-edges in increasing size: n 4 , n 5 , n 1 , n 2 , n 3 , n 6 � Unmark all nodes Practical Problems in VLSI Physical Design Multi-level Coarsening (5/11)

Hyperedge Coarsening Practical Problems in VLSI Physical Design Multi-level Coarsening (6/11)

Hyperedge Coarsening Practical Problems in VLSI Physical Design Multi-level Coarsening (7/11)

Obtaining Clustered-level Netlist � # of nodes/hyperedges reduced: 6 nodes, 4 hyperedges Practical Problems in VLSI Physical Design Multi-level Coarsening (8/11)

Modified Hyperedge Coarsening � Revisit skipped nets during hyperedge coarsening � We skipped n 1 , n 2 , n 3 , n 6 � Coarsen un-coarsened nodes in each net Practical Problems in VLSI Physical Design Multi-level Coarsening (9/11)

Modified Hyperedge Coarsening Practical Problems in VLSI Physical Design Multi-level Coarsening (10/11)

Obtaining Clustered-level Netlist � # of nodes/hyperedges reduced: 5 nodes, 4 hyperedges Practical Problems in VLSI Physical Design Multi-level Coarsening (11/11)

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.