Luis Garcia, Andres Cicuttin, Maria Liz Crespo, Kasun Sameera - PowerPoint PPT Presentation

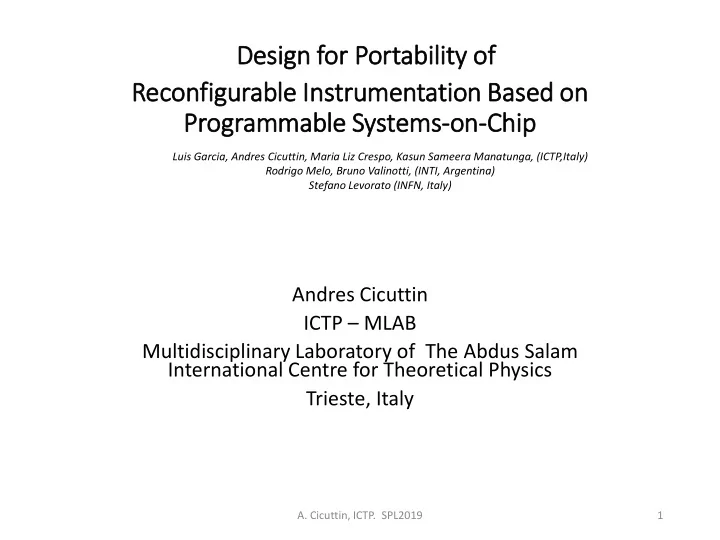

Desig sign for r Port rtabil ilit ity of f Reconfig igurable le In Instrumentatio ion Base sed on Programmable le Systems-on on-Chip ip Luis Garcia, Andres Cicuttin, Maria Liz Crespo, Kasun Sameera Manatunga, (ICTP,Italy) Rodrigo

Desig sign for r Port rtabil ilit ity of f Reconfig igurable le In Instrumentatio ion Base sed on Programmable le Systems-on on-Chip ip Luis Garcia, Andres Cicuttin, Maria Liz Crespo, Kasun Sameera Manatunga, (ICTP,Italy) Rodrigo Melo, Bruno Valinotti, (INTI, Argentina) Stefano Levorato (INFN, Italy) Andres Cicuttin ICTP – MLAB Multidisciplinary Laboratory of The Abdus Salam International Centre for Theoretical Physics Trieste, Italy A. Cicuttin, ICTP. SPL2019 1

Reconfigurable Virtual Instrumentation Emulated Instruments Virtual Instrument Reconfigurable Instrument A. Cicuttin, ICTP. SPL2019 2

Reconfigurable Virtual Instrumentation Oscilloscope Function generator Multimeter Transient recorder Spectrum Analyzer A. Cicuttin, ICTP. SPL2019 3

A. Cicuttin, ICTP. SPL2019 4

Hardware modularity and porting across different platforms A. Cicuttin, ICTP. SPL2019 5

Portability among different FMC Carriers of instrumentation based on dedicated hardware modules FMC carriers FMC modules A. Cicuttin, ICTP. SPL2019 6

A poss ssible FPGA Glo lobal Architecture for r RVI External Memory Controller PC Communication block Dual Port Memory External Instrument 1 Hardware RVI Core Controller 1 CONTROLLER With DMA PC FPGA capabilities communication External Parameters Instrument 2 Hardware Registers Core Controller 2 Instructions * * Status * * * * FIFO IN External Instrument N FIFO OUT Hardware Core Controller N RVI Bus Miscellaneous and High Speed Connections Port 1 Port 2 Port M Debugging Facilities * * * controller controller controller Controller A. Cicuttin, ICTP. SPL2019 7

Global Architecture of a distributed instrumentation Fibras Opticas DAQ System Pixel (287, 287) Ring Imaging Cherenkov Detector BORA-23 COMPASS Experiment CERN, 2004. BORA-12 Pixels : ~ 80000 BORA-0 Ave trigger rate: ~ 100KHz BORA-11 Dead time: ~ 1 us Max data rate: ~ 100GB/s DOLINA 24 C á mara 7 C á mara 6 C á mara 5 C á mara 4 RICH-1 192 tarjetas BORA C á mara 1 C á mara 3 C á mara 2 C á mara 0 8 Redes Fibras Opticas TDM de DSP Fibra desde TCS PCI PC de Control del RICH Pixel (0,0) (Ethernet) C á mara A. Cicuttin, ICTP. SPL2019 8

Da Data movement th through dis istr trib ibuted in instr trumentation Dolina, Side A FPGA TDP RAMs Dolina, Side B DSPs uP PCI Bus FIFOs A. Cicuttin, ICTP. SPL2019 9

Reconfigurable Instrumentation based on SoC FPGA Global Architecture FPGA-uP External communication Memory block SoC FPGA Time Critical External FPGA uP PC Hardware Ext HW Non Time Critical Middleware Controllers External Hardware A. Cicuttin, ICTP. SPL2019 10

Reconfigurable Virtual Instrumentation Based on a single SoC FPGA Typical Global Architecture FPGA uP FPGA – uP Communication SW (uP) Memory Mapped AXI Lite/ AXI Full/ AXI Stream Control Registers/ FIFOs and True Dual PC Registers Input/outp uP – PC Communication SW Native or Wishbone interface Native or Wishbone interface ut signals User Core Program External Hardware Interface uP – PC Communication FMC Connector Port RAM Virtual External SW (uP) User Core consoles & Hardware FPGA2uP Control (Application Logic FIFOs Computing specific) Design uP2FPGA FIFOs True Dual Port RAM Memory Memory Memory Controller Controller Controller External External External DDR RAM RAM RAM A. Cicuttin, ICTP. SPL2019 11

Reconfigurable Distributed Instrumentation Based on multiple SoC FPGA FPGA uP Standardized Data Packets FPGA FPGA FPGA FPGA uP FIFOs FIFOs Memory Mapped AXI Lite / Full / Stream FPGA2uP FPGA2Rout FIFOs FIFOs Native or Wishbone interface Native or Wishbone interface Native or Wishbone interface uP2FPGA Rout2FPGA Registers Registers Router Reserved Reserved area area controller controller UDMA True Dual UDMA True Dual Port RAM Port RAM Reserved Reserved area area CommBlock CommBlock Flags/semaphores for logic protocols DMA instructions Payload data A. Cicuttin, ICTP. SPL2019 12

A block view of the C ommunication B lock and memory mapping of the CB ports A. Cicuttin, ICTP. SPL2019 13

ComBlock: : Memory mapping on the uP side, and its connections with functional blocks implemented in the FPGA. SoC Bus WB or Native interfaces A. Cicuttin, ICTP. SPL2019 14

A possible logical utilization of reserved registers for safe data transfer through TDP RAM Asynchronous timing diagram of a flags-based protocol for safe data transmission through the TDPRAM of the CB A. Cicuttin, ICTP. SPL2019 15

Top level schematic: ComBlock and its connections FPGA-Subsystem AXI Bus ComBlock uP-Subsystem Custom connections with the FPGA-subsystem A. Cicuttin, ICTP. SPL2019 16

Top level schematic: ComBlock and its connections ComBlock FPGA subsystem uP Subsystem To external HW AXI Bus Custom connections with the FPGA-subsystem A. Cicuttin, ICTP. SPL2019 17

Configuration wizard window for the ComBlock (Vivado System Edition) A. Cicuttin, ICTP. SPL2019 18

Communication between the FPGA and uP subsystems It can be implemented by mean of three different hierarchical levels: 1. Physical Allows a simple utilization of the resources of the CB as storage elements. 2. Logical Includes a basic asynchronous logic protocol for a safe utilization of the ComBlock. It requires some reserved areas in the TDPRAM and some reserved registers. 3. Systemic Implements a high level protocol based on a set of complex instructions for Direct Memory Access (DMA). It provides transparent access from any domain to all resources mapped in a global memory mapping, including those that are not immediately accessible but that are directly accessible from the other domain. It requires a DMA machine in the FPGA, and a corresponding software routine in the uP. Each level corresponds to a communication layer. Each layer relays on the services offered by the immediate layer below, and provides services that can be used by the layer immediately above. A. Cicuttin, ICTP. SPL2019 19

Resource utilization of the CB in different Devices • RESOURCE UTILIZATION OF THE CB IN XILINXFPGAS • RESOURCE UTILIZATION OF THE CB IN ALTERA FPGAS Block Block Logic Name Slice Slice F7 F8 Family RAM Family Name ALMs RAM LUTs Registers Muxes Muxes Registers (kBytes) (kBytes) Cyclone V 5CSEMA5F31C6 764 563 290.25 Zynq-7000 xc7z020 726 816 128 64 290.25 Cyclone 10 LP 10CL006YU256A7G 1170 559 290.25 Spartan-7 xc7s100 726 816 128 64 290.25 Cyclone IV GX EP4CGX15BF14A7 1171 559 290.25 Artix-7 xc7a200 726 816 128 64 290.25 Kintex Cyclone IV E EP4CE6E22A7 1170 559 290.25 UltraScale+ xcku15p 854 816 128 64 290.25 Virtex UltraScale+ xcvu13p 854 816 128 64 290.25 A. Cicuttin, ICTP. SPL2019 20

Resource usage of a high-speed data acquisition system without and with the communication block Without Communication Block With Communication Block Name FPGA_ uP_ FPGA_ uP_ Communication Others Total Total Subsystem Subsystem Subsystem Subsystem _Block 7838 2486 Slice LUTs 187 960 6691 186 1466 834 (14.73%) (4.67%) Slice 14204 3105 264 1244 12696 264 1957 884 Registers (13.35%) (2.92%) 62 190 F7 Muxes 0 62 0 0 62 128 (0.23%) (0.71%) 64 F8 Muxes 0 0 0 0 (0%) 0 0 64 (0.48%) Block RAM 66.5 65 0 0 66.5 0 0 65 Tile (47.5%) (46.43%) A. Cicuttin, ICTP. SPL2019 21

Conclusions 1. The proposed Communication Block is a general purpose and reusable IP which completely absorbs the complexities of the SoC Interconnection Bus in modern SoC FPGA devices. 2. FPGA and uP subsystems can efficiently communicate through a ComBlock without any significant loss in performance and without any penalty in resources utilization. 3. Migration of complex systems among different SoC FPGA families and vendors is easier when based on ComBlocks since it essentially requires the porting of the ComBlock only. 4. Most of the uP embedded software and FPGA subsystem designs can be ported with minimal effort, and with facilitated debugging and optimization. 5. Since each subsystem deals with the other subsystem by reading and writing in the memory locations of the ComBlock , this block provides an abstract view of one subsystem to the other interacting subsystem. 6. The use of a ComBlock imposes a structured design methodology by mean of an explicit separation of the work in the uP and FPGA domains. 7. The implicit ComBlock strategy could simplify concrete Hardware/Software partitioning and implementation of complex cooperative activities. A. Cicuttin, ICTP. SPL2019 22

Thank you for your attention! A. Cicuttin, ICTP. SPL2019 23

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.