Untethered lowRISC, Memory Mapped IO and TileLink/AXI Wei Song - PowerPoint PPT Presentation

Untethered lowRISC, Memory Mapped IO and TileLink/AXI Wei Song 27/07/2015 Time Line expected Nov. 2014 Apr. 2015 Now Oct. 2015 First lowRISC Rocket-Chip release Memeory Untethered from Berkeley release. Mapped IO. lowRISC release.

Untethered lowRISC, Memory Mapped IO and TileLink/AXI Wei Song 27/07/2015

Time Line expected Nov. 2014 Apr. 2015 Now Oct. 2015 First lowRISC Rocket-Chip release Memeory Untethered from Berkeley release. Mapped IO. lowRISC release. Initial tagged · Untethered SoC. memory support. · Support Kintex KC705. · Added tags in L1 D$, L2. · Support MMIO. · Added a tag cache. · Support SD, UART, DDRAM. · Added 2 instructions to load/ · Open simulation environment. store tag. · A tutorial about Rocket-chip. 2

Rocket-Chip Release (Berkeley) Rocket Tile Rocket Tile Rocket Tile Rocket Rocket Rocket UART Core Core Core Host ARM SD Interface I$ D$ I$ D$ I$ D$ EtherNet TileLink TileLink TileLink TileLink TileLink TileLink L2 & L2 & L2 & Coherence Coherence Coherence Manager Manager Manager Arbiter MemIO Converter Memory Controller 3

lowRISC Release (tagged memory) Rocket Tile Rocket Tile Rocket Tile Rocket Rocket Rocket UART Core Core Core Host ARM SD I$ D$ I$ D$ I$ D$ Interface EtherNet TileLink TileLink TileLink TileLink TileLink TileLink L2 & L2 & L2 & Tag in L1 D$, L2 $ Coherence Coherence Coherence Manager Manager Manager Tag Cache LTAG/STAG instructions Allocator Tag Cache Data Tracker & Array Tracker & Converter Converter MetaData Array Arbiter Memory Controller 4

Latest Rocket-Chip (Berkeley) Rocket Tile Rocket Tile Rocket Tile UART Rocket Rocket Rocket Core Core Core Host ARM SD Interface I$ D$ I$ D$ I$ D$ EtherNet L2 Bus Cached TileLink L2 & L2 & L2 & Uncached TileLink Coherence Coherence Coherence Manager Manager Manager AXI MemIO Arbiter Multi-beat TileLink TileLink/AXI AXI Bus Standardize TileLink transactions Possible coherence support of L3 AXI/MemIO Code refactoring AXI/AXI interface (NASTI) Memory Controller 5

Untethered lowRISC SoC (First Version) Cached TileLink Rocket Tile Rocket Tile Rocket Tile Uncached TileLink Rocket Rocket Rocket Core Core Core AXI I$ D$ I$ D$ I$ D$ AXI-Lite L2 IO Bus L2 Cache Bus coherent L2 & L2 & L2 & TileLink/AXI-Lite Coherence Coherence Coherence DMA Manager Manager Manager Boot Minion Arbiter UART SD EtherNet DMA Tag Cache incoherent TileLink/AXI AXI Bus On-FPGA Memory Boot Ram Controller 6

Current Status Cached TileLink Rocket Tile Rocket Tile Rocket Tile Uncached TileLink Rocket Rocket Rocket Core Core Core AXI I$ D$ I$ D$ I$ D$ AXI-Lite L2 Cache Bus L2 IO Bus coherent L2 & L2 & L2 & Coherence Coherence Coherence TileLink/AXI-Lite DMA Manager Manager Manager Boot Minion Arbiter UART SD EtherNet DMA Tag Cache incoherent TileLink/AXI AXI Bus On-FPGA Memory Boot Ram Controller 7

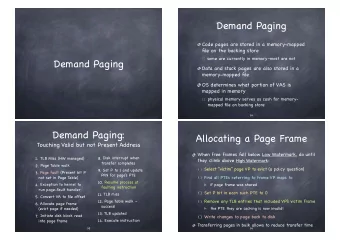

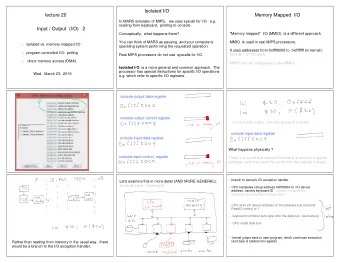

Memory Mapped IO • Target – IO load/write (B/HW/W/DW) – In-order uncached load/store – Side effect • None for all write in units of byte • None for all read in units of word (32-bit AXI-Lite) – No change in current L2 coherent manager 8

Untethered lowRISC SoC (First Version) Cached TileLink Rocket Tile Rocket Tile Rocket Tile Uncached TileLink Rocket Rocket Rocket Core Core Core AXI I$ D$ I$ D$ I$ D$ AXI-Lite L2 IO Bus L2 Cache Bus coherent L2 & L2 & L2 & TileLink/AXI-Lite Coherence Coherence Coherence DMA Manager Manager Manager Boot Minion Arbiter UART SD EtherNet DMA Tag Cache incoherent TileLink/AXI AXI/AXI-Lite AXI Bus On-FPGA Memory Boot Ram Controller 9

L1 Data Cache mem.finish mem.req mem.grant mem.probe wb prober [WriteBack;rocket/nbdcache.scala] wb.meta/data_read meta/data read [ProbeUnit;rocket/nbdcache.scala] 0 mshrs req data_resp wb_req Arb req release 1 meta/data read [MSHRFile;rocket/nbdcache.scala] rep mshr meta_write line_state [MSHR mshrs.wb_req rocket/nbdcache.scala] prober.release mem.release 0 Arb mshrs.meta_write 1 prober.meta/data_read mshrs.request mshrs.replay prober.meta_write s1_recycled s2_recycle s2_hit 0 s3_req s2_req Arbiter s1_req 1 2 3 4 s1_req.addr s2_data_correctable amoalu dtlb s2_data (corrected) [TLB [AMOALU cpu.ptw rocket/tlb.scala] rocket/nbdcache.scala] dtlb.ptw vpn meta ppn rhs meta 0 0 [MetadataArray s1_addr [MetadataArray uncore/cache.scala] Arbiter lhs uncore/cache.scala] 1 Arb out 1 write 2 read resp s2_data (corrected) 3 = = = = cpu.req s2_tag_eq_way 4 s2_hit data data code s1_tag_eq_way [DataArray [DataArray rocket/nbdcache.scala] rocket/nbdcache.scala] 0 [DecodeLogic 0 rocket/decode.scala] Arbiter Arb 1 1 write correctable s2_data read resp in out s1_data correct 2 3 s2_data Stage 3 Stage 1 Stage 2 Stage 4 (uncorrected) 10 cpu.resp.bits.data cpu.resp.valid

L1 Data Cache (simplified) mem.req mem.grant mshr mshrs mshrs.meta_write mshrs.request mshrs.replay s2_hit s2_req Arbiter s1_req s1_req.addr dtlb s1_addr s2_hit vpn meta meta ppn Arbiter s1_addr read resp write cpu.req = = = = data amoalu data s1_tag_eq_way Arb write Arbiter rhs out s2_data read resp lhs s1_data Stage 1 Stage 2 Stage 4 Stage 3 cpu.resp 11

L1 Data Cache with IO Handler mem.grant io.grant mem.req io.req mshrs mshr mshrs.meta_write mshrs.request mshrs.replay iomshr iomshr.replay replay io_data io_data s1_io_data request s2_hit s2_req ioaddr Arbiter s1_req addr io s2_req.addr s1_req.addr dtlb s1_addr s2_io_replay vpn s2_io_data meta meta ppn Arbiter s1_addr read resp write cpu.req = = = = data amoalu data s1_tag_eq_way Arb write Arbiter rhs out s2_data read resp lhs s1_data Stage 1 Stage 2 Stage 4 Stage 3 12 cpu.resp

TileLink Channels • Manager/Client – Manager: Coherent manager or next level cache/device – Client: upper level cache • 5 Channels – Acquire: [C -> M] • Read, uncached write (write-through, IO), permission update – Grant: [M -> C] • Ack to Acquire (with data when read) – Finish: [C -> M] • Finish a transaction – Probe: [M -> C] • Coherence probe (snoop, invalidate) – Release: [C -> M] • Write-back (replace or invalidate) 13

Untethered lowRISC SoC (First Version) Cached TileLink Rocket Tile Rocket Tile Rocket Tile Uncached TileLink Rocket Rocket Rocket Core Core Core AXI I$ D$ I$ D$ I$ D$ AXI-Lite L2 IO Bus L2 Cache Bus coherent L2 & L2 & L2 & TileLink/AXI-Lite Coherence Coherence Coherence DMA Manager Manager Manager Boot Minion Arbiter UART SD EtherNet DMA Tag Cache incoherent TileLink/AXI AXI/AXI-Lite AXI Bus On-FPGA Memory Boot Ram Controller 14

TileLink Corssbar client Manager TileLink Corssbar Acquire Acquire L2 Grant Grant L1 $ Finish Finish Bank Probe Probe Release Release Acquire Acquire Grant Grant L2 L1 $ Finish Finish Bank Probe Probe Release Release 15

Shared TileLink Corssbar client Manager Shared TileLink Corssbar Acquire Acquire L2 Grant Grant L1 $ Finish Finish Bank Probe Probe Release Release Acquire Acquire Grant Grant L2 L1 $ Finish Finish Bank Probe Probe Release Release Use a SuperChannel to store all types of TileLink channels. 16

Current Status of TileLink/AXI • TileLink/AXI (Berkeley, Rocket-chip) – only a whole cache line • TileLink/AXI-Lite (lowRISC) – 1,2,4,8 byte write; 4,8 byte read • AHB/APB (Berkeley, Z-Scale) • Still needed: – AXI/AXI-Lite compatible, auto width SerDes switch • The AXI-Node from PULP • May be in Chisel for its parameterization capability – AXI/Wishbone, TileLink/Wishbone 17

Remain Issues • Interrupt controller • Open Sourced, License compatible IPs – UART (Flexpret, BSD) – SD host controller – Ethernet controller (Xilinx IP for now) – Memory controller (difficult to get) • Open Source EDA tools – Current environment: • VCS (DRAMSim, Front-end server, DirectC) • Vivado+SDK (SDK not available for Kintex) – Target environment: • Verilator (SystemVerilog 2009, SystemC, VPI, DPI) • Vivado only 18

After the Untethered SoC • Implementing the hierarchical tag cache (hardware) • Debug interface • Integrating minions (PULP) • Tag support in Rocket cores (Lucas) 19

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.