ISAs and Y86-64 Z80 TI calculators lab Wednesday in-lab quiz C - PowerPoint PPT Presentation

ISAs and Y86-64 Z80 TI calculators lab Wednesday in-lab quiz C loops to assembly loops condition codes ISAs versus microarchitectures last time 2 RISC V some embedded Itanium some HP servers SHARC some digital

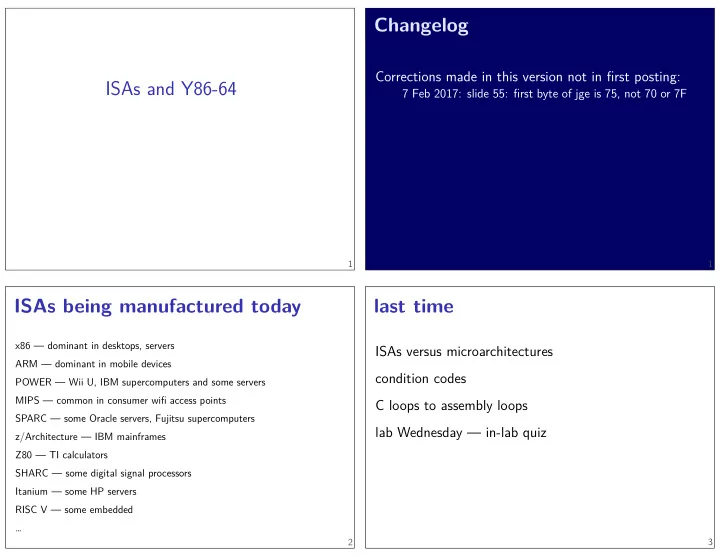

ISAs and Y86-64 Z80 — TI calculators lab Wednesday — in-lab quiz C loops to assembly loops condition codes ISAs versus microarchitectures last time 2 … RISC V — some embedded Itanium — some HP servers SHARC — some digital signal processors z/Architecture — IBM mainframes 1 SPARC — some Oracle servers, Fujitsu supercomputers MIPS — common in consumer wifj access points POWER — Wii U, IBM supercomputers and some servers ARM — dominant in mobile devices x86 — dominant in desktops, servers ISAs being manufactured today 1 7 Feb 2017: slide 55: fjrst byte of jge is 75, not 70 or 7F Corrections made in this version not in fjrst posting: Changelog 3

strlen/strsep lab anonymous feedback (2) possible, could we receive solutions to the quizzes?” problem is supposed to be solved? If that’s not so students who got it wrong can know how the “Could we go over the quizzes in class the next day, “bring back the .webm recordings of the lectures” anonymous feedback (3) 6 yes, one has more experience teaching this course yes, some will like one more than the other need to stay in sync — labs/homeworks should be less work for both of us — better quality? when he is in the lecture?” “why is Professor Khan lecturing instead of Reiss 5 two functions that operate on C strings before taking the quiz. Thanks.” nice. This way, we actually know what to study 4.1–4.3. If you could be consistent, that would be the top of the pre-quiz it stated to read sections required reading before class on Tuesday, however, at “According to the Schedule, only section 4.1 was bunch of comments (some not quite as polite) like: anonymous feedback (1) 4 you: code both under test conditions lab writeup has example implementations terminated by ‘sentinel’ \0 7 pre-week — readings for entire week’s lectures post-week — material from entire week’s lectures

anonymous feedback (4) char *strsep( char **ptrToString, char delimiter); char *token; while ((token = strsep(&ptr, ' ')) { printf("[%s]", token); } /* output: [this][is][a][test] */ /* final value of buffer: "this\0is\0a\0test" */ 10 strsep (2) char str[] = "this test"; is a test"; char *ptr = str; char *token; token = strsep(&ptr, ' '); /* token points to &buffer[0], string "this" */ /* ' ' after "this" replaced by '\0' */ /* ptr points to &buffer[5]: "is a test" */ “I think it is unfair that when asked about the fmags char *ptr = buffer; a be doing. I have looked all over the Internet and in lecture last week, Khan fumbled her answer and could not explain when each fmag would be set yet that was still a quiz question. If Khan cannot explain to us in lecture which assembly command would set which fmag…” question on quiz was comparing cmpq and subq cmpq is subtraction without storing result shouldn’t have needed to exactly how fmags were set 8 anonymous feedback (5) “I am looking over the lab writeup and I cannot understand what the strsep() method is supposed to can’t fjnd anything that would be helpful. If we approach the problem.” is char buffer[] = "this char *strsep( char **ptrToString, char delimiter); strsep (1) could spend maybe 5-10 minutes in class Tuesday 9 then maybe I’ll have a better idea of how to just going over what the method is supposed to do 11 ␣ ␣ ␣ ␣ ␣ ␣ ␣ ␣

anonymous feedback (6) ptr: x ... x[3] = sentinel; x = malloc( sizeof ( short )*4); short *x; lists homework 14 on heap or regs on stack *x payload: 1 x[3] x ... x = malloc( sizeof (node_t)); node *x; } node; list *next; short payload; typedef struct node_t { 3 2 “I believe that the question ”What does the output f x[0] x[1] x[2] typedef struct range_t { len: 3 typedef struct node_t { or regs *x ptr: payload: 1 x ... x = malloc( sizeof (node_t)); node *x; } node; list *next; short payload; 3 unsigned int length; 2 1 ptr: len: 3 x ... x.ptr = malloc( sizeof ( short )*3); x.length = 3; range x; } range; short *ptr; ptr: 1 x x[0] = 1; x[1] = 2; x[2] = 3; typedef struct node_t { x.ptr[0] = 1; ... x.ptr = malloc( sizeof ( short ) * 3); x.length = 3; range x; } range; short *ptr; unsigned int length; typedef struct range_t { x[3] = sentinel; short *x = malloc( sizeof ( short ) * 4); short payload; lists homework 12 f = 0; f = 6 && 0; f = 6 && !(4); f = 6 && !(6 & 5); !4 == 0 ; ~4 == 0xFFF...B && is logical; & is bitwise of 2, yet it return s true (0010).” Consider the case in which v=6. Six is not a power tell us about the input v?” has the incorrect answer. ... 14 list *next; unsigned int length; } node; x[0] x[1] x[2] x ... x[3] = sentinel; x = malloc( sizeof ( short )*4); short *x; lists homework typedef struct range_t { short *ptr; 13 } range; range x; x.length = 3; node *x = malloc( sizeof (node_t)); x.ptr = malloc( sizeof ( short )*3); x[3] short sentinel = − 9999; ! is logical; ~ is bitwise f = v && !(v & (v − 1)); x − >payload = 1; x − >next = ... ← on stack on heap → short sentinel = − 9999; short sentinel = − 9999; 3 − 9999 3 − 9999 1 2 1 2

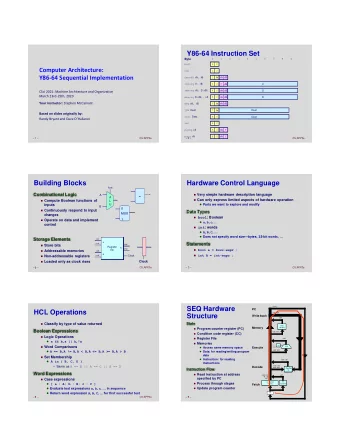

about our fjnal 2–6 byte Itanium 41 bits* 128 300 Z80 1–4 byte 7 40 VAX 1–14 byte 8 150 z/Architecture 16 31 1000 RISC V 4 byte* 31 500* 17 Other choices: condition codes? instead of: testq %r11, %r12 je somewhere could do: /* _B_ranch if _EQ_ual */ beq %r11, %r12, somewhere 200 4 byte 9 May, 7PM–10PM x86-64 location will be announced form for confmicts will be announced 15 non-anonymous feedback 16 ISA variation instruction set instr. length # normal registers approx. # instrs. 1–15 byte MIPS32 16 1500 Y86-64 1–10 byte 15 18 ARMv7 4 byte* 16 400 POWER8 4 byte 32 1400 18

Other choices: addressing modes 20 more? x86-64: push , pop , movsb , … instructions that write multiple values? complexity Other choices: instruction 21 Reduced from what? RISC — Reduced Instruction Set Computer CISC and RISC VAX: both ways of specifying operands. examples: x86, AVR, Z80, … add src2, src1=dest (or swapped) ARM, POWER, MIPS, SPARC, … add dest, src1, src2 Other choices: number of operands 19 VAX: ((%r11)) (register value is pointer to pointer) ARM: %r11 << 3 (shift register value by constant) x86-64: 10(%r11,%r12,4) 22

Some VAX instructions 24 few addressing modes no instructions with two memory operands no “loops” within single instructions more registers fjxed-length instructions seperate instructions to access memory fewer, simpler instructions typical RISC ISA properties 25 compilers, not hand-written assembly complex instructions were harder to implement complex instructions were usually not faster Why RISC? secret simpler instruction set MATCHC haystackPtr , haystackLen , needlePtr , needleLen loop in hardware??? Find the position of the string in needle within haystack. MATCHC haystackPtr , haystackLen , needlePtr , needleLen microcode 23 string specifjed by patternPtr . Edit the string pointed to by sourcePtr using the pattern EDITPC sourceLen , sourcePtr , patternLen , patternPtr coeffjcientPtr at the value x . Evaluate the polynomial whose coefficients are pointed to by POLY x , coeffjcientsLen , coeffjcientsPtr Find the position of the string in needle within haystack. 26 typically: lookup sequence of microinstructions

Y86-64 instruction set 28 i — immediate r — register m — memory irmovq immovq iimovq rrmovq rmmovq based on x86 rimovq mrmovq mmmovq mimovq Y86-64: movq Y86-64: movq SD movq i — immediate r — register m — memory irmovq immovq iimovq rrmovq rmmovq rimovq mrmovq mmmovq mimovq SD movq 28 27 hlt (renamed) omits most of the 1000+ instructions based on x86 Y86-64 instruction set much, much simpler encoding much, much simpler encoding ret nop xorq call addq jmp movq (renamed) andq cmov CC popq subq j CC pushq addq jmp leaves omits most of the 1000+ instructions leaves 27 popq andq cmov CC pushq ret nop hlt (renamed) xorq call subq j CC movq (renamed) source destination source destination ❳❳❳❳❳ ✘ ❳❳❳❳❳ ✘ ❳❳❳❳❳ ✘ ❳❳❳❳❳ ✘ ✘✘✘✘✘ ✘✘✘✘✘ ✘✘✘✘✘ ✘✘✘✘✘ ❳ ❳ ❳ ❳ ❳❳❳❳❳ ✘ ❳❳❳❳❳ ✘ ✘✘✘✘✘ ✘✘✘✘✘ ❳ ❳ ❳❳❳❳❳ ✘ ❳❳❳❳❳ ✘ ✘✘✘✘✘ ✘✘✘✘✘ ✭✭✭✭✭ ❤❤❤❤❤ ✭ ❤❤❤❤❤ ✭✭✭✭✭ ✭ ❤ ❤ ❳ ❳

Y86-64: movq much, much simpler encoding jle skip_move instead of: Y86-64: register-to-register only exist on x86-64 (but you probably didn’t see them) conditional move cmovCC 29 ret skip_move: nop hlt (renamed) xorq call movq (renamed) cmov CC andq popq rrmovq %rax, %rbx // ... pushq subq j CC much, much simpler encoding ret nop hlt (renamed) xorq call andq cmov CC movq (renamed) popq pushq can do: addq jmp leaves omits most of the 1000+ instructions based on x86 Y86-64 instruction set 30 cmovg %rax, %rbx subq j CC addq jmp SD movq mrmovq i — immediate r — register m — memory irmovq immovq iimovq rrmovq rmmovq leaves rimovq 31 mimovq omits most of the 1000+ instructions mmmovq based on x86 Y86-64 instruction set 28 source destination ❳❳❳❳❳ ✘ ❳❳❳❳❳ ✘ ✘✘✘✘✘ ✘✘✘✘✘ ❳ ❳ ❳❳❳❳❳ ✘ ✘✘✘✘✘ ❳ ❳❳❳❳❳ ✘ ✘✘✘✘✘ ✭✭✭✭✭ ❤❤❤❤❤ ✭ ❤ ❳

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.