Introduction to structured Test, diagnosis, and verification VLSI - PowerPoint PPT Presentation

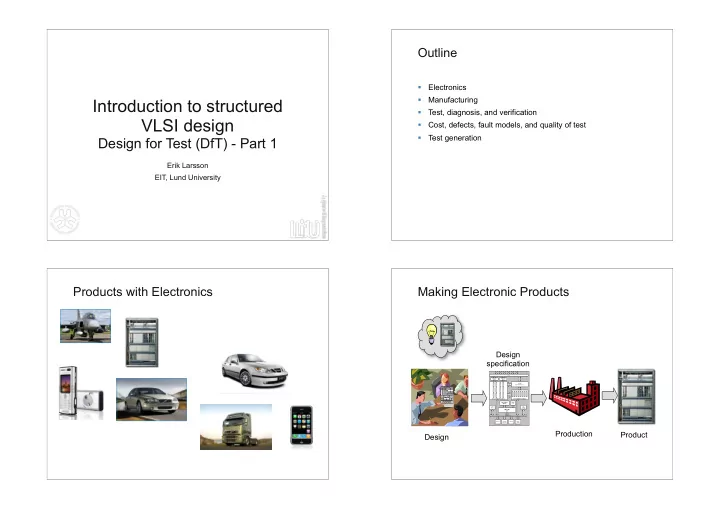

Outline Electronics Manufacturing Introduction to structured Test, diagnosis, and verification VLSI design Cost, defects, fault models, and quality of test Test generation Design for Test (DfT) - Part 1 Erik Larsson

Outline Electronics Manufacturing Introduction to structured Test, diagnosis, and verification VLSI design Cost, defects, fault models, and quality of test Test generation Design for Test (DfT) - Part 1 Erik Larsson EIT, Lund University Products with Electronics Making Electronic Products Design specification Production Product Design

Electronics Integrated Circuits (ICs) Wafer IC Board “System” Integrated Circuits (ICs) Integrated Circuits (IC) Die Small Scale Integration (SSI), early 1960s example, Philips TAA320 had two transistors Medium Scale Integration (MSI), late 1960s example, Intel 4004 had 2300 transistors Large Scale Integration (LSI), mid-1970s example, Intel 8008 had 4500 transistors Viper 2.0 RevB Very-Large Scale Integration (VLSI), 1980s, Analog/Digital TV Processor example, Intel 80286, 134000 transistors 10mm x 10 mm (100 mm 2 ) Ultra-Large Scale Integration (ULSI), now, more than 1 million transistors ~10 M gates Wafer-scale integration (WSI) ~50 M transistors System-on-a-chip ~100 clock domains Three dimensional integrated circuits (3D-ICs)

Printed Circuit Board (PCB) Multi-board System Backplane IC Manufacturing AND-gate Chemical or plasma etch Si-substrate Hardened resist SiO 2 (a) Silicon base material Si-substrate Photoresist SiO 2 (d) After development and etching of resist, chemical or plasma etch of SiO Si-substrate 2 Hardened resist (b) After oxidation and deposition SiO2 of negative photoresist Si-substrate UV-light Patterned (e) After etching optical mask Exposed resist SiO2 Si-substrate Si-substrate (f) Final result after removal of resist (c) Stepper exposure

IC Manufacturing Outline The cost to set up a modern Electronics and manufacturing 45 nm process is $200–500 Defects, test, diagnosis, and verification million Cost, defects, fault models, and quality of test The purchase price of a Test generation photomask can range from $1,000 to $100,000 for a single mask. As many as 30 masks (of varying price) may be required to form a complete mask set. IC Defects PCB Defects Occurrence frequency (%) Defect classes 51 Shorts Opens 1 6 Missing components Wrong components 13 6 Reversed components Seed Bent leads 8 Salt 5 Analog specifications Digital logic 5 5 Performance (timing) Ref.: J. Bateson, In-Circuit Testing , Van Nostrand Reinhold, 1985.

Fault Models Test Real defects too numerous and often not analyzable Device under test (DUT) A fault model identifies targets for testing A fault model makes analysis possible Effectiveness measurable by experiments Response Stimulus A defect manifests itself as a fault A fault is modeled by a fault model Example of fault models: Stimulus: test vectors Stuck-at Fault, Bridging Fault, Shorts (Resistive shorts), Opens, Test pattern: test vector + expected test response (ordered n-tuple of binary values) Delay Faults, Transient Fault Produced test response is compared against expected test response So far stuck-at fault model is the most used one: Motivations: Simple and covers quite well possible defects Design specification is correct. It means that tests can be generated from the design specification. Verification, Test and Diagnosis Diagnosis and Volume Production Yield Verification is to verify the correctness of the design. It is performed through simulation, hardware emulation, or formal methods. It is performed once prior to manufacturing. Responsible for quality of design. Pass/fail testing Test verifies the correctness of manufactured hardware. Test is a two-part process: Test generation: software process executed once during design, and Test application: electrical tests applied to hardware. Test application Diagnosis performed on every manufactured device. Responsible for quality of devices. Diagnosis: Identification of a specific fault that is present on DUT. First silicon Ramp-up Volume production

Making Fault Free Electronic Products Types of Test Rule of ten: Finding Production ok? a defect in one later Wafer sort (or probe) Test of die on the wafer step increases cost with a factor 10 Final test (package) Test of packaged chips compared to ok? Acceptance Test to demonstrate compliance ok? addressing the with purchaser’s requirements defect in current ok? step. Sample Test some but not all parts ok? Go/No-go Pass or fail test Characterization Test actual parameters (performance) Stress screening (burn-in) At high temperature to get wear- out Diagnostic (repair) Test to pinpoint defective part Test Preparation Production Test In-Field Test On-line Test while system is in operation Types of Test Objective with Test Wafer sort - tests the logic of each die on the wafer Specify the test vector Determine correct response (expected response) Evaluate cost of test (# patterns related to cost) Final test - tests the logic of each packaged IC Evaluate quality of test Fault coverage = No of faults detected / No. faults modeled Board test - tests interconnections (soldering errors) Yield = Number of good parts / Total number of tested parts

Tests Automatic Test Equipment (ATE) Good IC that pass test -> OK Consists of: Bad IC that fail test -> OK Powerful computer Powerful 32-bit Digital Signal Processor (DSP) for analog Bad ICs that pass test -> test escape Outcome utcome of testing Good ICs that fail test -> yield loss test test Test Program (written in high- level language) running on the Pass Fail computer Probe Head (actually touches Yield the bare or packaged chip to Good OK loss perform fault detection experiments) IC Test Bad OK Probe Card or Membrane Probe esc. (contains electronics to measure signals on chip pin or pad) ATE Outline Electronics and manufacturing Automatic Test Equipment (ATE) Defects, test, diagnosis, and verification Test stimuli (TS) Cost, defects, fault models, and quality of test Device under test 0010100 0110000 Test generation Combinational test generation Expected responses (ER) Fault simulation 1011001 1101010 Test set compaction Sequential test generation Produced responses (PR) Compare 0111011 0100101 Pass/fail

Test Generation Test Generation Example: Create test for output SA1 (Stuck-At 1) Fault-free Faulty a SA1 z b X X 0 1 0 0 Find test stimuli such that test responses are a b z different in fault-free and faulty device 0 0 0 0 1 0 1 0 0 1 1 1 To get test for SA0 on h: Stuck-at Fault (SAF) Model Single Stuck-at Fault 1. fix c=1 -> good value on j to be 0 and defective value to be 1 (input reached - done) Three properties define a single stuck-at fault 2. fix k=0 -> set f=0 A line is fixed to logic value 0 (stuck-at-0) or 1 (stuck-at-1) (input reached - done) Only one line is faulty The faulty line is permanently set to 0 or 1 For the stuck-at fault model there are for a circuit with n lines The fault can be at an input or output of a gate 2*n possible faults Circuit has 12 fault sites ( ) and 24 single stuck-at faults G3 Find test for SA0 on h Faulty circuit value G5 U G2 G NOR Z G1 W OR Good circuit value A AND s-a-0 NOR B F c j X 0(1) G4 H d a AND 1(0) g h Y 1 z i 0 1 e b Quality of a test is given by: k fault coverage = faults detected / total number of faults f Test vector for h s-a-0 fault Example: 12 lines (24 faults) detect 15 faults: f.c.=15/24 (63%)

Single Stuck-at Fault Stuck-at Faults Let us generate a s-a-1 on the same line a b z To get c=0, set a=1 and b=1 Minimize fault list through: 0 0 0 a 4 exhaustively generated vectors z 0 1 0 To get fault effect on d (1/0), set a=1 but only 3 deterministic vectors b 1 0 0 needed: Fault equivalence To get fault effect on z (0/1), set e=0 1 1 1 To get e=0, set b=1 and c=1 (but c=0 - see above) s-a-1 d Value fault free/faulty (v/v f ) 1(0) a Stuck-at 0 on a: a=1/0, b=1 -> z=1/0 //vector (stimulus) 11 c 0(1) z Stuck-at 0 on b: b=1/0, a=1 -> z=1/0 //vector (stimulus) 11 e b Stuck-at 0 on z: b=1, a=1 -> z=1/0 //vector (stimulus) 11 0 Stuck-at 1 on a: a=0/1, b=1 -> z=0/1 //vector (stimulus) 01 Stuck-at 1 on b: b=0/1, a=1 -> z=0/1 //vector (stimulus) 10 Stuck-at 1 on z: a=0, b=x -> z=0/1 //vector (stimulus) 0x or x0 Fault Equivalence Equivalence Rules sa0 sa0 Fault equivalence: Two faults f1 and f2 are equivalent if all tests sa1 sa1 that detect f1 also detect f2. sa0 sa1 sa0 sa1 WIRE sa0 sa1 sa0 sa1 If faults f1 and f2 are equivalent then the corresponding faulty AND OR functions are identical. sa0 sa1 sa0 sa1 sa0 sa1 NOT sa0 sa1 c j sa0 sa1 sa0 sa1 a d g sa0 sa1 sa0 sa1 h sa0 NAND NOR z sa1 i sa0 1 sa0 sa1 sa0 sa1 e b 1 sa1 sa0 k sa1 f FANOUT

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.