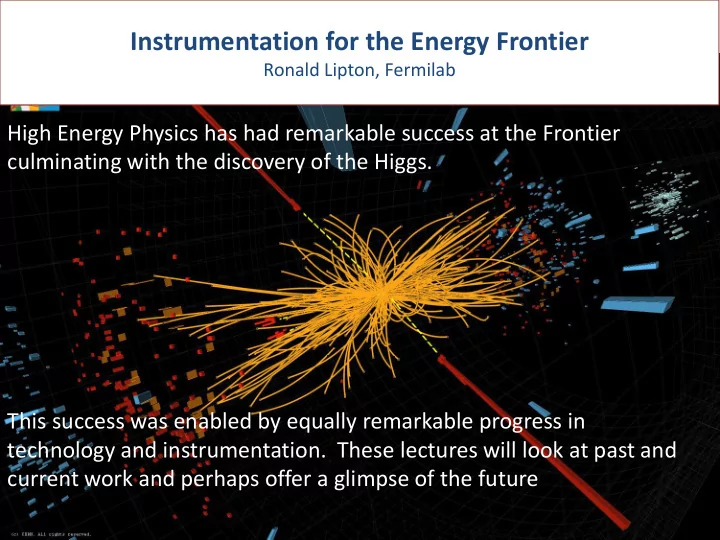

Instrumentation for the Energy Frontier Ronald Lipton, Fermilab - PowerPoint PPT Presentation

Instrumentation for the Energy Frontier Ronald Lipton, Fermilab High Energy Physics has had remarkable success at the Frontier culminating with the discovery of the Higgs. This success was enabled by equally remarkable progress in technology

Instrumentation for the Energy Frontier Ronald Lipton, Fermilab High Energy Physics has had remarkable success at the Frontier culminating with the discovery of the Higgs. This success was enabled by equally remarkable progress in technology and instrumentation. These lectures will look at past and current work and perhaps offer a glimpse of the future

Tracking Let’s think about designing a tracker for a collider detector • They all look pretty generic • The solenoidal field defines the overall geometry • Transitions from a barrel to disk geometry tend to be awkward D0 – Disks provide lower mass at high eta, more normal incidence – The number of hits/area is maximized with disks combined with barrels R. Lipton 2

Designing a Tracker - 1 1 g b� g c t b = g c t ´ 1 g » c t » 30 - 300 microns æ ö 1 + ( R inner ç ÷ ) 2 R outer ç ÷ s ip = s meas ç ÷ (1 - R inner ç ÷ ) R outer è ø D0SMT First let’s decide on the vertex detector • Scale set by HQ lifetimes • Minimize R inner /R outer • R inner set by occupancy, beam pipe diameter • R outer set by cost of pixelated detectors Tevatron luminous region s meas set by technology, mass of sensors • ~25 cm long • ILC ~ 5 microns at 1.5 cm (slow, rad soft, monolithic) • LHC ~ 20 microns at 5 cm (fast, rad hard, hybrid) • Length set by luminous region, angular coverage R. Lipton 3

Designing a Tracker - 2 2E-11 1.8E-11 1.6E-11 Layer Impact on momentum resolution 1.4E-11 (Seiden SDC-91-00021) 1.2E-11 ALPHA 1E-11 8E-12 6E-12 4E-12 2E-12 0 0.00 20.00 40.00 60.00 80.00 100.00 120.00 140.00 Layer Radius (cm) æ ö å r i d i ç ÷ æ ö æ ö s i ç ÷ f 0 2 - B A ç ÷ k = ÷= ç ÷ ç ÷ ç - B è C ø å r 2 d i è k ø ç ÷ i ç ÷ s i 2 è ø a i = ( C r 2 - B r Momentum Resolution i i 2 ) Resolution proportional to s /BL 2 • s i s i For a high momentum track f = f 0 + k r k =1/p t • We effectively want to measure Df (circumferential • å k ( curvature ) = a i d i distance d i ) • Most important information is at the outer radius and Alpha estimates the effect near the origin of the layer on momentum • Intermediate layers primarily provide pattern recognition resolution R. Lipton 4

Designing a Tracker - 3 CMS FPIX Plaquette LHCB VELO R and F sensors The Forward Direction • As we move forward the we begin to lose ∫ Bdl and momentum resolution • Disks become more cost effective/hit than barrels • We can recover some momentum resolution with precision disks • We want to measure phi well, r not as well, but this is difficult in a disk geometry • Intermediate disks have little effect on resolution Tiled 3D pixel structure R. Lipton 5

Doublet strip modules For track trigger Doublet pixel/strip modules for track trigger Forward pixel diska For extended h coverage Possible design for CMS Phase 2 tracker with extension to improve acceptance for forward physics (H ➛ tt , Higgs self coupling, WW scattering) R. Lipton 6

Silicon Tracking This has become the “baseline” technology for the energy frontier. It is: • Precise ~ micron-level resolution • Moderate to low mass (depends on density, cooling, electronics) • Fast ~ can achieve sub-nanosecond resolution • Radiation hard – can be designed to operate to 10 16 /cm 2 fluence • Costly? $10/cm 2 for CMS sensors $3/cm 2 for CMOS electronics We can profit from the huge technical advances and infrastructure in the semiconductor industry R. Lipton 7

Signal and Noise • What is the thinnest “ practical ” silicon tracker? 1 g 2 kT ENC 2 = ( C det + C gate ) 2 a • Noise – g m t s Increasing g m costs power (g m ~I d ), minimize C det ->pixels ~ 10 ff possible minimal coupling to other electrodes • Power – assume i d =500 na, pitch 25 microns • Signal – shoot for 25:1 s/n 10000 – 80 e/h pairs/micron Signal/Noise Ratio • Speed – let ’ s say 5 ns 1000 • Mechanical – – Can thin to ~10 microns 100 10 0 50 100 150 200 250 300 Detector Thickness (microns) R. Lipton 8

Silicon Detector How we connect the Al SiO 2 detectors to the electronics, p+ cool them, and mount them is the name of the game… n+ Hybrid Pixel Interconnect using bump bonds Analog Analog cable cable SVX4 SVX4 hybrid hybrid R. Lipton 9

Detector/Electronics Integration Technologies MAPS • Monolithic active pixels – collect charge in a few m m epitaxial layer (STAR, ALICE) • Charge coupled device (SLD) CCD • DEPFET (Belle II) • Silicon on Insulator… source top gate drain clear bulk • 3D Integration… ~1µm n+ p+ p+ n+ n+ p s n internal gate i x a y 50 µm r - - t DEPFET e - - - - + m m y + s - n - - + + - p+ rear contact 3D SOI R. Lipton 10

Solving Problems - MAPS MAPs – technology used in cameras using charge collection by diffusion in a thin(~5-15 m m) epitaxial layer Slow-charge Low S/N Charge lost to collection by parasitic PMOS diffusion Thick, high 4 Well process 3D assemblies Fully depleted resistivity substrates epitaxial layers (RAL) (IPHC-DRS) Thinning and backside processing (IPHC-DRS)

Technologies - Device-scaling Rapid initial decrease in cost • Slower leveling Voltage no longer scaling (P~CV 2 f) Analog becomes harder at feature sizes below 65 nm Designs become very costly 8” 130 nm - $500k 12” 65 nm - $1.9M (Deptuch, IF ASIC meeting) R. Lipton 12

Technologies- Bonding Costs and Yields Current and projected costs and yields for sensor/readout integration technologies

Technologies- Three Dimensional Electronics Back-Face A 3D-IC technology is composed of two or more layers of active electronics or sensors Face-Face connected with through silicon vias • It enables intimate interconnection between sensors and readout circuits MIT-LL 3D-IC process • It enables unique functionality FDSOI oxide- – Digital/analog/ and data oxide bonding communication tiers Ziptronix / licensed to Novati – Micro/macro pixel designs – Correlate information • Wafer thinning enables low mass, high resolution sensors • Etching of vias (3D) through silicon bulk • Bonding technologies enable very fine pitch, high resolution pixelated devices • Commercialization of 3D wafer bonding can reduce costs for large areas • Unique circuit/sensor Xilinx 3D-based FPGA

Pixelization- Copper bonded two-tier IC 3D Interconnect (Tezzaron) Technology based on: • Bonding between layers – Copper/copper – Oxide to oxide fusion – Copper/tin bonding – Polymer/adhesive bonding – Cu stud • Through wafer via formation and metalization 8 micron pitch, 50 micron thick oxide bonded 8 micron pitch DBI (oxide-metal) bonded imager (Lincoln Labs) PIN imager (Ziptronix) IBM 32 nm 3D technology PCB Interconnect 15

Opportunities in 3 Dimensions readout 200 micron IC and pads Buried sensor oxide trenches Handle wafer CMS Level 1 track trigger - Correlate hits in adjacent layers to filter out low momentum tracks Combine active edge and 3D electronics to produce tiled sensors combined with ROICs for large area arrays CMS – Use stack of 3D tiers to emulate tracker layers for CAM – based track recognition Use TSVs to connect each SiPM subpixel to quenching, timing, and control electronics

Example - Track Trigger In CMS the L1 trigger will be saturated with multiple interaction background • Use tracking information in the L1 Via-Last Module trigger (FNAL design) – Send hits from tracks with Pt>2 • 50 x 250 micron through silicon vias • Bump bonded short strip sensors off detector for L1 • Analog signals through flex jumper • 2.5 cm long strips (set by chip size) – Correlate hits from sensors separated by ~ 1 mm TSVs 250 m ROIC – Correlation done on-module Analog Short (0.125 cm) strips signals Short (1.25 mm) strips • To do this we need novel interconnect technology which Flex Jumper allows the chip to “see” signals from Carbon Foam Spacer top and bottom sensors – Through-silicon-vias allows single layer of electronics to see both Long (2.5 cm) strips R. Lipton 17

High Speed silicon Two techniques to attain ~10 ps resolution • Fast parallel plate structure using 3D detector technology Fast parallel plate structure • Use amplification to produce a large signal (Da Via) from initial electron arriving at gap structure TSV� Coarse SiPM Tier� Fine SiPM Tier� Coincidence and active quench� Gain-based structure (Sadrozinski) READOUT FLEX Use two layers of 3D SiPMs to produce fast, low power, low noise trackers (Lipton) R. Lipton Higgs Factory 18 Workshop[ 11/16/2012

Radiation Damage in Silicon • Radiation – Electromagnetic ( g , b , x-ray). • Ionization, e-hole pair creation. – Hadronic (n, p , p). Damage to the bulk material caused by displacement of atoms from lattice sites in addition to ionization • Electronics are affected primarily by ionization A. Vasilescu (INPE Bucharest) and G. Lindstroem (University of Hamburg), Displacement damage in silicon, on-line compilation – Charge buildup in insulating layers – Charge injection into sensitive nodes • Sensors are affected by bulk damage and ionization – Crystal structure damage – Introduction of traps – Introduction of mid-band states R. Lipton 19

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.