IBIS-AMI Modeling of Asynchronous Topic: o Nam elementum commodo - PowerPoint PPT Presentation

TITLE IBIS-AMI Modeling of Asynchronous Topic: o Nam elementum commodo mattis. Pellentesque High Speed Link Systems malesuada blandit euismod. Topic: o Nam elementum commodo mattis. Pellentesque Speakers malesuada blandit euismod.

TITLE IBIS-AMI Modeling of Asynchronous Topic: o Nam elementum commodo mattis. Pellentesque High Speed Link Systems malesuada blandit euismod. Topic: o Nam elementum commodo mattis. Pellentesque Speakers malesuada blandit euismod. Image Hongtao Zhang (Xilinx Inc.) Fangyi Rao (Keysight Technologies) o Nam elementum commodo mattis. Pellentesque malesuada blandit euismod. Authors Topic: Hongtao Zhang (Xilinx Inc.) o Nam elementum commodo mattis. Pellentesque Fangyi Rao (Keysight Technologies) malesuada blandit euismod. Zhaoyin Daniel Wu (Xinlin Inc.) Geoff Zhang (Xilinx Inc.)

IBIS-AMI Modeling of Asynchronous High Speed Link Systems Speakers Hongtao Zhang (Xilinx Inc.) Fangyi Rao (Keysight Technologies) Authors Hongtao Zhang (Xilinx Inc.) Fangyi Rao (Keysight Technologies) Zhaoyin Daniel Wu (Xilinx Inc.) Geoff Zhang (Xilinx Inc.)

SPEAKERS Hongtao Zhang, Xilinx, hongtao.zhang@xilinx.com received his Ph.D. degree in Electrical and Computer Engineering from University of California, San Diego in 2006. He joined Xilinx in 2013 and is now a senior staff Design Engineer, working on SerDes architecture development and circuit design. From 2010 to 2013, he was with SerDes design team at Oracle Corporation, where he worked on circuit design and architecture modeling. Prior to that, he worked on SerDes characterization at Texas Instruments, Dallas. His current interests are SerDes architecture development and modeling, high speed mixed- signal circuit design and optimization, and system level modeling. Fangyi Rao, Keysight, Fangyi_rao@keysight.com is a master R&D engineer at Keysight Technologies. He received his Ph.D. degree in theoretical physics from Northwestern University. He joined Agilent/Keysight EEsoft in 2006 and works on Analog/RF and SI simulation technologies in ADS. From 2003 to 2006 he was with Cadence Design Systems, where he developed SpectreRF Harmonic Balance technology and perturbation analysis of nonlinear circuits. Prior to 2003 he worked in the areas of EM simulation, nonlinear device modeling, and medical imaging.

Outline Synchronous and Asynchronous Systems o Synchronous and Asynchronous Definition o Embedded clocks in SerDes systems o Clock Data Recovery (CDR) o CDR Architecture Example IBIS-AMI Modeling Overview IBIS-AMI Simulation for Asynchronous Systems Asynchronous System Simulation and Measurement o CDR Tracking, eye diagram and bathtub curves o Frequency offset tolerance o Jitter tolerance Conclusions and Future Work

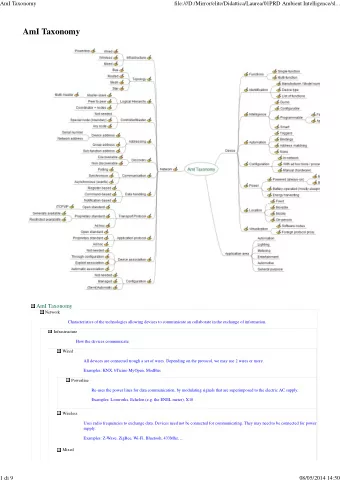

Synchronous and Asynchronous Systems Synchronous System o Signal has the same frequency as the local clock and has a fixed phase offset Δ𝑔 = 0, ΔΦ( t) = constant Asynchronous System signal o Mesochronous Δ𝑔 = 0, ΔΦ( t) is bounded clock o Plesiochronous Δ𝑔 ≠ 0, but very small o Heterochronous Signal Phase − Clock phase = Δ𝑔 × 𝑢 + ΔΦ( t) Δ𝑔 ≠ 0

SerDes Clocking Clock in SerDes o Clock information is embedded in the serial data o RX needs to recover the clock from the incoming waveform and use it to latch the data Common clock – when both the TX and the RX are o Δ𝑔 = 0 sharing the same common clock source Only phase needs to be recovered Independent clock – the TX and the RX do not share o the same clock source (Plesiochronous) Both the phase and the frequency need to be tracked

SerDes Clock Data Recovery (CDR) Two types of CDR in SerDes Systems o Burst mode system (often in a point-to-multipoint applications) Applications include GPON, EPON and LANs Commonly used CDR architectures include gated oscillators or oversampling techniques o Continuous mode system (often used in a point-to-point applications) Applications include SONET, Fiber Channel and Gigabit Ethernet Commonly used CDR architectures include PLL-based or Phase Interpolatro (PI)-based PLL based clock data recovery does not produce quantized phase error Phase interpolator from each channel can share the same PLL PLL based clock data recovery Phase Interpolator based clock data recovery data PD Accumulators Charg Low Pass data PD Pump Filter Phase VCO PLL Interpolator

CDR Architecture Example PI-based CDR loop can be categorized into 1 st order loop, which is inherently stable o 2 nd order loop, which can track frequency offset o + + -1 data PD Gp Z - + -1 Gf Z PI

CDR Architecture Example – Cont’d With frequency offset present, 1 st order CDR would lead to phase tracking error that is 𝛦𝑔 proportional to the ppm offset 1𝑡𝑢−𝑝𝑠𝑒𝑓𝑠 ~ 𝑄 𝑓 𝐻 𝑞𝑗 × 𝐻 𝑞 This will affect the eye margin and jitter tolerance Frequency and time domain architecture model can predict the CDR behavior and margin loss IBIS-AMI simulation is desired for higher accuracy and to account for the convergence complexities and interactions among various adaptation loop in the SerDes system

IBIS-AMI Modeling Overview TX DLL input is a Binary EDA Tool Sends +/-0.5V Sequence switching between binary sequence to TX DLL at TX DLL processes data rate and sample rate 0.5V and -0.5V the waveform determined by IBIS-AMI and sends it out parameters bit_time and TX output is convolved with to the EDA tool sample_interval and pass EDA Tool then these parameters to the TX channel impulse response convolves the waveform with the The convolved waveform is channel impulse response, which is input to the RX DLL sampled at the EDA Tool sends the same sampling rate RX DLL processes the data RX processes the data and convolved waveform and sends the processed to the RX DLL and sends equalized signal and waveform along with passes the bit_time clock_times to the EDA tool clock ticks to the simulator for and sample_interval for post processing to the RX DLL post processing

Simulation Approach for Async Systems (a) To simulate the asynchronous system o The EDA tool needs to send different (a) bit_time (determined by the data rate TX DLL handles and the offset) to the RX and the TX EDA Tool Sends waveform to the necessary TX DLL at nominal sampling interpolation and o The offset can be added either on the rate and passes the revised re-sampling and bit_time (nominal adjusted TX side or on the RX side processes the by ppm offset) and the EDA Tool then waveform before nominal sample_interval convolves the o sends it out to The system sample time AMI_parameters waveform with the EDA tool sample_interval can be kept constant the channel impulse o response, which AMI DLL needs to handle any real is sampled at the number bit_time and sample_interval EDA Tool sends the nominal RX DLL processes the data waveform to the RX sampling rate (which may lead to non-integer and sends the processed DLL and passes the waveform along with samples per bit) nominal bit_time clock_times to the EDA tool and sample_interval for post processing to the RX DLL

Simulation Approach for Async Systems (b) Alternative approach o The EDA tool needs to send different (b) bit_time (determined by the data rate EDA Tool Sends waveform to and the offset) and different TX DLL at TX side sampling sample_interval to the RX and the TX rate (nominal sampling rate TX DLL processes EDA Tool then convolves the with ppm offset) and passes the waveform waveform with the channel the corresponding and sends it out impulse response, which is o The offset can be added either on the AMI_parameters to the TX to the EDA tool sampled at the TX sampling rate TX side or on the RX side DLL: revised bit_time and revised sample_interval o The EDA tool needs to do the necessary interpolation and re-sampling between EDA Tool sends the EDA Tool then interpolates the corresponding blocks re-sampled RX DLL processes the data and resamples the waveform to the RX and sends the processed waveform according to the DLL and passes the waveform along with nominal sampling rate nominal bit_time clock_times to the EDA tool determined by the original and the nominal for post processing AMI_parameters: bit_time sample_interval to and sample_interval the RX DLL

Simulation Setup Channel and Simulation Setup o Three channels were selected with IL at 36dB, 30dB and 18dB, respectively at 14 GHz o Data rate at 28 Gbps o PRBS-23 for 2M bits Offset added on the TX side in unit of Δ f o

Simulation Results – CDR Phase Shift High Loss Channel (36dB) With +/-5 Δ f offset, the CDR is able to track and the eye is open o With 8.5 Δ f, the offset is outside of the CDR capture range and the eye is closed o o Phase shift can be calculated from the clock ticks using the equation below ) 𝒖 𝒅𝒎𝒍 𝒐 − 𝒖 𝒅𝒎𝒍 (0 𝒒𝒊𝒃𝒕𝒇 𝒕𝒊𝒋𝒈𝒖(𝒐) = − 𝒐 𝑼 0 8.5 D f

Simulation Results – Eye Diagram Eye diagrams o Within CDR frequency locking range, eye diagram is negligibly affected o Outside of the CDR frequency capture range, eye is completely closed Medium Loss High Loss Low Loss

Simulation Results – Bathtub Curves Bathtub curves o Within CDR frequency locking range, BER is only slightly affected o The CDR locking point is not noticeably changed High Loss Medium Loss Low Loss

Simulation Results – Eye Contours Eye contours o Within CDR frequency locking range, eye contour is comparable o The eye contour symmetry is largely retained High Loss Medium Loss Low Loss

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.