High Voltage DC and RF Power Reliability of GaN HEMTs J. A. del - PowerPoint PPT Presentation

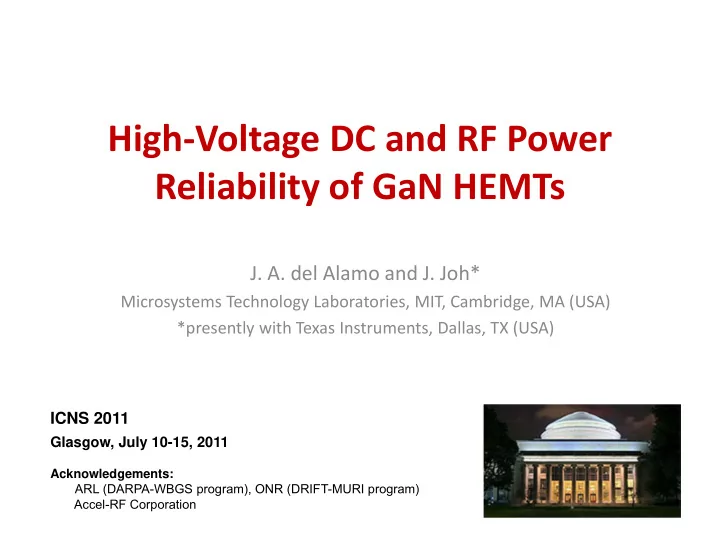

High Voltage DC and RF Power Reliability of GaN HEMTs J. A. del Alamo and J. Joh* Microsystems Technology Laboratories, MIT, Cambridge, MA (USA) *presently with Texas Instruments, Dallas, TX (USA) ICNS 2011 Glasgow, July 10-15, 2011

High ‐ Voltage DC and RF Power Reliability of GaN HEMTs J. A. del Alamo and J. Joh* Microsystems Technology Laboratories, MIT, Cambridge, MA (USA) *presently with Texas Instruments, Dallas, TX (USA) ICNS 2011 Glasgow, July 10-15, 2011 Acknowledgements: ARL (DARPA-WBGS program), ONR (DRIFT-MURI program) Accel-RF Corporation

Breakthrough RF ‐ mmw power in GaN HEMTs Micovic, MTT ‐ S 2010 Micovic, Cornell Conf 2010 94 ‐ 95 GHz MMIC PAs: P out >40 W/mm, over 10X GaAs! Wu, DRC 2006 2

GaN HEMTs in the field Counter ‐ IED Systems 200 W GaN HEMT for (CREW) cellular base station Kawano, APMC 2005 100 mm GaN ‐ on ‐ SiC volume manufacturing Palmour, MTT ‐ S 2010 3

Recent great strides in RF power reliability 28 V RF oper. life MTTF=1x10 7 h at 47 V (C ‐ > 2 years (X ‐ band, 5 dB comp., ~150 o C) band, 3 dB Yamasaki, MTT ‐ S 2010 comp., ~150 o C) Kolias, MTT ‐ S 2010 MTTF=7x10 7 h at 28 V (40 GHz, 1.5 dB comp., ~150 o C) Heying, MTT ‐ S 2010 4

Dominant degradation mechanisms under RF stress? • In general: – RF stress P out ↓ , Gain ↓ , I Dmax ↓ , |I G | ↑ , V T shift, dispersion ↑ – RF introduces more degradation than DC – RF stress accelerated by V DQ , P in , T j Conway, IRPS 2007; Joh, ROCS 2008, IEDM 2010, ROCS 2011; Chini, IEDM 2009 Chini, EUMW 2009 • Indications of two competing mechanisms: – Trap creation and trapping? – Field ‐ driven structural degradation? Dammann, IRPS 2010 Rozman, ROCS 2009; Chini, IEDM 2009 5

Outline 1. RF power reliability concerns 2. Methodology for RF reliability experiments 3. Electrical and structural results 4. Discussion: the role of gate placement 5. Conclusions 6

RF power reliability concerns High ‐ power DC stress: – Not accessible to DC ON DC stress: OFF and semi ‐ ON high ‐ voltage stress experiments DC stress : – Mostly benign – Device blows up – Degradation of I Dmax , R D , I Goff instantly – V T shift – Electron trapping – Trap creation – Formation of grooves and pits under drain ‐ end of gate 7

RF experiment flowchart: conventional approach Limitations: START • Bias point shifts during stress T stress • Limited RF characterization RF Stress • No DC characterization P out , PAE, Gain, I DQ , I GQ • No trap characterization • If examining different RF conditions, RF characterization END confusing 8

RF experiment flowchart: improved approach (I) New features: START • RF and DC characterization under T base standardized conditions Short Characterization (DC, RF) • At beginning, end and periodically T stress through experiment RF Stress Limitations: • Limited characterization End? NO • Characterization temperature YES cannot be too different from Short Characterization (DC, RF) stress temperature • Cannot separate trapping from END “permanent” degradation 9

RF experiment flowchart: improved approach (II) START New features: • Comprehensive DC, RF and Detrapping RT pulsed characterization under Full Characterization (DC, RF, CC) standardized conditions (RT) T base • At beginning, end, and during Short Characterization (DC, RF) experiment T stress • Detrapping step to enable trap RF Stress characterization Key Event? YES NO END: detrapping + Full characterization 10

Setup for RF reliability studies Accel ‐ RF AARTS RF10000 ‐ 4/S system: Accel ‐ RF System • two 2 ‐ 4 GHz channels Hardware • two 7 ‐ 12 GHz channels DC/Pulsed Characterization DUT • Max P in =30 dBm Switching Matrix ‐ KeithleySources ‐ Agilent B1500A • T base =50 ‐ 200 ° C Heater RF/DC Units T base Windows ‐ based PC MIT RF/DC Accel ‐ RF Software Characterization Suite ‐ RF measurement ‐ DC FOMs ‐ Temperature control ‐ Current collapse ‐ Stressing Augmented with: • external instrumentation for DC/pulsed characterization • software to control external instrumentation and extract DC and RF FOMs 11

RF ‐ stress experiments T base =100 ° C for 30 mins START – Full DC I ‐ V sweeps Detrapping – RF power sweep @ V DS =28 V, I DQ =100 mA/mm Full Characterization (DC, RF, CC) – Current collapse (after 1” V DS =0, V GS = ‐ RT 10 V pulse) Short Characterization (DC, RF) – Room temperature T base =50°C RF (DC) Stress T stress – DC FOMs: I Dmax , R S , R D , V T , I Goff , … Key – RF FOMs @ V DS =28 V, I DQ =100 mA/mm Event? YES NO • Saturated conditions (P in =23 dBm): P out,sat , G sat , PAE END: detrapping + • Linear conditions (P in =10 dBm): G lin Full characterization – Every few minutes at T base =50 ° C 12

RF stress experiments: P in step ‐ stress • Motivation: – higher P in larger V waveform at output • MMIC: – single ‐ stage internally ‐ matched – 4x100 μ m GaN HEMT (OFF-state V crit >60 V at RT) – Gate centered in S ‐ D gap 14 25 Gain 12 20 • Step P in stress: 10 Gain (dB) PAE (%) – V DS = 40 V, I DQ = 100 mA/mm 15 8 – P in = 0 (DC), 1, 20 ‐ 27 dBm PAE 6 10 4 – 300 min stress at each step 5 2 – T stress =50 ° C (T j =110 ‐ 230 ° C) V DS =40 V, I DQ =100 mA/mm 0 0 10 15 20 25 30 P in (dBm) Joh, ROCS 2011 13

Evolution of RF stress P in P out P out 30 33 START 25 32 20 Detrapping P out (dBm) P in (dBm) 15 31 Full Characterization (DC, RF, CC) 10 RT 30 5 DC DC Short Characterization (DC, RF) 0 29 T base =50°C 0 10 20 30 40 50 60 0 10 20 30 40 50 60 Time (hr) Time (hr) RF (DC) Stress PAE I DQ Gain T stress 400 30 Key 25 300 Event? YES NO 20 I DQ (mA/mm) 200 PAE (%) END: detrapping + 15 100 Full characterization 10 0 5 -100 0 0 20 40 60 0 10 20 30 40 50 60 Time (hr) Time (hr) • P in changing RF FOMs changing • Degradation apparent but not easily quantifiable 14

RF FOM during short characterization START Detrapping Full Characterization (DC, RF, CC) RT Short Characterization (DC, RF) T base =50°C RF (DC) Stress T stress P out at P in =23 dBm, G lin at P in =10 dBm Key V DS =28 V, I DQ =100 mA/mm, T base =50 ° C Event? YES NO END: detrapping + Full characterization • Mild degradation under DC and low P in • Adding RF increases degradation: P in ↑ P out ↓ 15

DC FOM during short characterization DC|P in =1 20 21 22 23 24 25 26 27 dBm 1.2 1.E+01 START 1.E+00 Detrapping I Dmax /I Dmax (0), R/R(0) I Goff 1.1 1.E-01 |I Goff | (mA/mm) R D Full Characterization (DC, RF, CC) RT 1.E-02 1 Short Characterization (DC, RF) R S 1.E-03 T base =50°C RF (DC) Stress 1.E-04 0.9 T stress I Dmax 1.E-05 Key T base =50 ° C Event? YES NO 0.8 1.E-06 0 1000 2000 3000 END: detrapping + Time (min) Full characterization • Mild degradation under DC and low P in • At P in =20 dBm, step degradation in I Goff • Beyond P in =20 dBm, increasing degradation of I Dmax and R D 16

DC/RF/CC full characterization 9 33 Permanent I Dmax Degradation (%) T base =RT 8 START 7 Current Collapse (%) Saturated P out (dBm) 32 P out Detrapping 100 °C 6 5 Full Characterization (DC, RF, CC) 31 Current RT 4 Collapse Short Characterization (DC, RF) 3 DC RF T base =50°C 30 2 RF (DC) Stress Initial T stress 1 Δ |I Dmax | Key 0 29 Event? YES NO ‐ 10 0 10 20 30 END: detrapping + Stress Input Power P in (dBm) Full characterization • Beyond P in =20 dBm: ― Sharp P out degradation ― Permanent degradation of I Dmax ― Increased CC evidence of new trap creation 17

Structural degradation (planar view) SEM AFM • Pit formation along drain end of gate edge • Similar to DC high voltage OFF ‐ state stress DC OFF ‐ state stress, V DG =50 V, 1000 min, ~150 o C Makaram, APL 2010 18

HV OFF ‐ state DC vs. RF power degradation Similar pattern of degradation: HV OFF ‐ state DC RF power I Dmax ↓ beyond V crit ↓ beyond P in ‐ crit R D ↑ beyond V crit ↑ beyond P in ‐ crit R S small increase small increase I Goff ↑ beyond V crit ↑ beyond P in ‐ crit Current Collapse ↑ beyond V crit ↑ beyond P in ‐ crit Permanent I Dmax ↓ beyond V crit ↓ beyond P in ‐ crit Pits under drain end of gate Yes Yes Pits under source end of gate No No High V end of load line responsible for degradation 19

Step P in stress: Offset Gate Offset gate devices (L GS <L GD ): OFF-state V crit > 80 V at T=150 ° C RF FOMs DC FOMs 32.5 DC RF P in =20 23 26 dBm 3 1.E+01 DC RF P in =20 23 26 dBm T j ~170 ° C by adjusting T base 15 Small Signal Gain G lin (dB) 2.5 32 I Dmax /I Dmax (0), R/R(0) Inner loop (50°C) Saturated P out (dBm) 1.E+00 R S |I Goff | (mA/mm) 14.5 2 31.5 Gain 1.5 1.E-01 R D 14 31 1 P out I Dmax 1.E-02 13.5 30.5 0.5 I Goff Inner loop (50°C) 0 1.E-03 30 13 0 300 600 900 1200 0 300 600 900 1200 Time (min) Joh, IEDM 2010 Time (min) • Increased degradation under high P in • No I Goff degradation • Degradation of I Dmax and R S , not R D 20

HV OFF ‐ state DC vs. RF power degradation Different pattern of degradation: HV OFF ‐ state DC RF power I Dmax ↓ beyond V crit ↓ beyond P in ‐ crit R D ↑ beyond V crit ↑ beyond P in ‐ crit R S small increase ↑↑ beyond P in ‐ crit I Goff ↑ beyond V crit No Current Collapse ↑ beyond V crit ↑ beyond P in ‐ crit Permanent I Dmax ↓ beyond V crit ↓ beyond P in ‐ crit Pits under drain end of gate Yes No Pits under source end of gate No No High V end of load line NOT responsible for degradation 21

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.