Hardware-Software Codesign 10. Performance Analysis of Distributed - PowerPoint PPT Presentation

Hardware-Software Codesign 10. Performance Analysis of Distributed Embedded Systems Lothar Thiele 10 - 1 System Design Specification System Synthesis Estimation SW-Compilation Instruction Set HW-Synthesis Intellectual Intellectual

Hardware-Software Codesign 10. Performance Analysis of Distributed Embedded Systems Lothar Thiele 10 - 1

System Design Specification System Synthesis Estimation SW-Compilation Instruction Set HW-Synthesis Intellectual Intellectual Prop. Code Prop. Block Machine Code Net lists Swiss Federal Computer Engineering 10 - 2 Institute of Technology and Networks Laboratory

Contents Overview Real-Time Calculus Modular Performance Analysis Examples Swiss Federal Computer Engineering 10 - 3 Institute of Technology and Networks Laboratory

Formal Analysis vs. Simulation e.g. delay upper bound Worst-Case Best-Case lower bound Real System Simulation Formal analysis Swiss Federal Computer Engineering 10 - 4 Institute of Technology and Networks Laboratory

Analysis and Design Embedded System = Computation + Communication + Resource Interaction Analysis: Infer system properties from subsystem properties. Design: Build a system from subsystems while meeting requirements. Swiss Federal Computer Engineering 10 - 5 Institute of Technology and Networks Laboratory

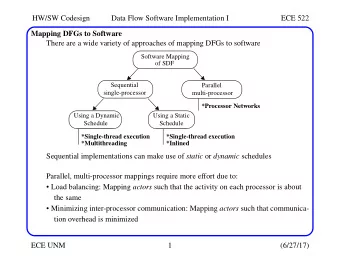

Modular Performance Analysis architecture Task graphs diagrams Application Architecture Mapping Scheduling Data Measure- sheets ments System Model WCET Formal Analysis specification Service Model (Resources) Performance Processing Model Model (Tasks & Scheduling) Load Model (Environment) Analysis Formal Input traces specification Analysis Results Swiss Federal Computer Engineering 10 - 6 Institute of Technology and Networks Laboratory

Abstract Models for Performance Analysis Processor Task Input Stream Concrete Instance Abstract Representation Service Model Load Processing Model Model Swiss Federal Computer Engineering 10 - 7 Institute of Technology and Networks Laboratory

Modular System Composition CPU BUS DSP RM TDMA TDMA GPC GPC GSC GPC GPC GPC Swiss Federal Computer Engineering 10 - 8 Institute of Technology and Networks Laboratory

Overview Swiss Federal Computer Engineering 10 - 9 Institute of Technology and Networks Laboratory

Contents Overview Real-Time Calculus Modular Performance Analysis Examples Swiss Federal Computer Engineering 10 - 10 Institute of Technology and Networks Laboratory

Foundation Real-Time Calculus can be regarded as a worst- case/best-case variant of classical queuing theory . It is a formal method for the analysis of distributed real-time embedded systems. Related Work : Min-Plus Algebra : F. Baccelli, G. Cohen, G. J. Olster, and J. P. Quadrat, Synchronization and Linearity --- An Algebra for Discrete Event Systems, Wiley, New York, 1992. Network Calculus : J.-Y. Le Boudec and P. Thiran, Network Calculus - A Theory of Deterministic Queuing Systems for the Internet, Lecture Notes in Computer Science, vol. 2050, Springer Verlag, 2001. Swiss Federal Computer Engineering 10 - 11 Institute of Technology and Networks Laboratory

Comparison of Algebraic Structures Algebraic structure set of elements one or more operators defined on elements of this set Algebraic structures with two operators plus-times: min-plus: Infimum : The infimum of a subset of some set is the greatest element, not necessarily in the subset, that is less than or equal to all other elements of the subset. Swiss Federal Computer Engineering 10 - 12 Institute of Technology and Networks Laboratory

Comparison of Algebraic Structures Joint properties : Example : plus-times: min-plus: Swiss Federal Computer Engineering 10 - 13 Institute of Technology and Networks Laboratory

Comparison of Algebraic Structures Joint properties : Differences : plus-times : Existence of a negative element for : min-plus : Idempotency of : Swiss Federal Computer Engineering 10 - 14 Institute of Technology and Networks Laboratory

Comparison of System Theories Plus-times system theory signals, impulse response, convolution, time-domain Min-plus system theory streams, variability curves, time-interval domain, convolution Swiss Federal Computer Engineering 10 - 15 Institute of Technology and Networks Laboratory

Abstract Models for Performance Analysis C(t) Processor Task Input Stream R’(t) R(t) Concrete Instance Abstract Representation Service Model β ( ∆ ) Load Processing Model α ( ∆ ) Model Swiss Federal Computer Engineering 10 - 16 Institute of Technology and Networks Laboratory

From Streams to Cumulative Functions Data streams : R(t) = number of events in [0, t) Resource stream : C(t) = available resource in [0, t) R(t) C(t) Swiss Federal Computer Engineering 10 - 17 Institute of Technology and Networks Laboratory

From Event Streams to Arrival Curves events Event Stream number of events in in t=[0 .. 2.5] ms t 2.5 t [ms] Arrival Curves α = [ α l , α u ] ∆ events α u α l maximum / minimum arriving events in any interval of length 2.5 ms 2.5 ∆ [ms] Swiss Federal Computer Engineering 10 - 18 Institute of Technology and Networks Laboratory

From Resources to Service Curves availability Resource Availability available service in t=[0 .. 2.5] ms t 2.5 t [ms] Service Curves β = [ β l , β u ] ∆ β u service β l maximum/minimum available service in any interval of length 2.5 ms 2.5 ∆ [ms] Swiss Federal Computer Engineering 10 - 19 Institute of Technology and Networks Laboratory

Example 1: Periodic with Jitter A common event pattern that is used in literature can be specified by the parameter triple ( p, j, d ), where p denotes the period, j the jitter, and d the minimum inter-arrival distance of events in the modeled stream. periodic p periodic jitter p j ≥ d Swiss Federal Computer Engineering 10 - 20 Institute of Technology and Networks Laboratory

Example 1: Periodic with Jitter periodic periodic with jitter Swiss Federal Computer Engineering 10 - 21 Institute of Technology and Networks Laboratory

Example 1: Periodic with Jitter Arrival curves : Swiss Federal Computer Engineering 10 - 22 Institute of Technology and Networks Laboratory

Example 2: TDMA Resource Consider a real-time system consisting of n applications that are executed on a resource with bandwidth B that controls resource access using a TDMA policy . Analogously, we could consider a distributed system with n communicating nodes , that communicate via a shared bus with bandwidth B , with a bus arbitrator that implements a TDMA policy. TDMA policy : In every TDMA cycle of length , one single c resource slot of length s i is assigned to application i . appl.2 ... appl. n appl.2 ... appl. n appl.1 appl.1 c c s n Swiss Federal Computer Engineering 10 - 23 Institute of Technology and Networks Laboratory

Example 2: TDMA Resource Service curves available to the applications / node i: B s i s i c-s i 2 c c Swiss Federal Computer Engineering 10 - 24 Institute of Technology and Networks Laboratory

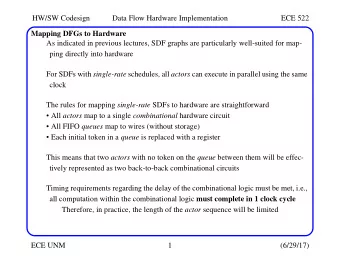

Greedy Processing Component (GPC) available resources FIFO buffer input output event event GPC stream stream remaining resources Examples: computation (event – task instance, resource – computing resource [tasks/second]) communication (event – data packet, resource – bandwidth [packets/second]) Swiss Federal Computer Engineering 10 - 25 Institute of Technology and Networks Laboratory

Greedy Processing Component Behavioral Description • Component is triggered by incoming events. • A fully preemptable task is instantiated at every event arrival GPC to process the incoming event. • Active tasks are processed in a greedy fashion in FIFO order. • Processing is restricted by the availability of resources. Swiss Federal Computer Engineering 10 - 26 Institute of Technology and Networks Laboratory

Greedy Processing Component (GPC) Conservation Laws C(t) C(t) R(t) R(t) R’(t) GPC R’(t) C’(t) t Swiss Federal Computer Engineering 10 - 27 Institute of Technology and Networks Laboratory

Greedy Processing For all times u ≤ t we have R’(u) ≤ R(u) (conservation law). We also have R’(t) ≤ R’(u)+C(t)–C(u) as the output can not be larger than the available resources. Combining both statements yields R’(t) ≤ R(u) + C(t) – C(u). Let us suppose that u* is the last time before t with an empty buffer. We have R(u*) = R’(u*) at u* and also R’(t) = R’(u*) + C(t) – C(u*) as all available resources are used to produce output. Therefore, R’(t) = R(u*) + C(t) – C(u*). As a result, we obtain B(t) u* t Swiss Federal Computer Engineering 10 - 28 Institute of Technology and Networks Laboratory

Abstract Models for Performance Analysis C(t) Processor Task Input Stream R’(t) R(t) Concrete Instance Abstract Representation Service Model β ( ∆ ) Load Processing Model α ( ∆ ) Model Swiss Federal Computer Engineering 10 - 29 Institute of Technology and Networks Laboratory

Abstraction GPC GPC time domain time-interval domain cumulative functions variability curves Swiss Federal Computer Engineering 10 - 30 Institute of Technology and Networks Laboratory

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.