Hardware-Software Codesign 3. Mapping Applications To Architectures - PowerPoint PPT Presentation

Hardware-Software Codesign 3. Mapping Applications To Architectures Lothar Thiele Computer Engineering Swiss Federal 3 - 1 Institute of Technology and Networks Laboratory System Design specification system synthesis estimation

Hardware-Software Codesign 3. Mapping Applications To Architectures Lothar Thiele Computer Engineering Swiss Federal 3 - 1 Institute of Technology and Networks Laboratory

System Design specification system synthesis estimation SW-compilation instruction set HW-synthesis intellectual intellectual prop. code prop. block machine code net lists Computer Engineering Swiss Federal 3 - 2 Institute of Technology and Networks Laboratory

What is ahead? Section 4: Partitioning Some basic methods to assign tasks to computing resources (or communication to networks and busses). Section 5: Multiobjective Optimization Generic method to optimize H/S systems (and other engineering systems) Section 7: Design Space Exploration Application of these methods to design space exploration Computer Engineering Swiss Federal 3 - 3 Institute of Technology and Networks Laboratory

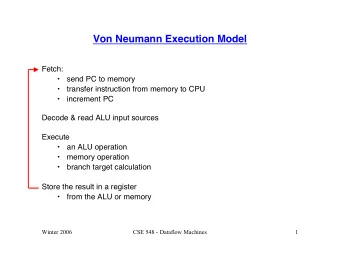

System Synthesis - Mapping Mapping transforms behavior into structure and execution allocation : select components partitioning binding : assign functions to components mapping scheduling : determine execution order … finally, synthesis results into implementation scheduler function_1() function_2() function_3() function_1() function_2() function_3() function_1() function_2() function_3() core1 core2 core3 read() write() port port port port channel channel Computer Engineering Swiss Federal 3 - 4 Institute of Technology and Networks Laboratory

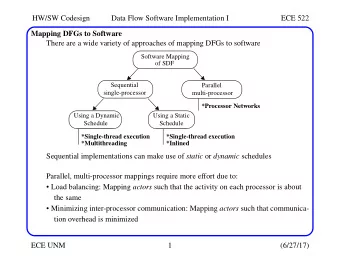

Application Specification … using an underlying model of computation function_1() function_2() function_3() function_1() function_2() function_3() function_1() function_2() function_3() some examples (see also next slides) task graphs: data flow graph, control flow graph process networks: Kahn process network, synchronous data-flow state machine representations: SpecCharts, StateCharts [not covered in this course] for mapping , very often only the process network structure and its (abstract) properties are relevant (abstraction from detailed functionality) Computer Engineering Swiss Federal 3 - 5 Institute of Technology and Networks Laboratory

Application Specification - Example 1 3 a b b data flow graph a b (DFG) ∗ ∗ + c + ∗ x = 3*a + b*b - c; c y = a + b*x; b z = b - c*(a + b); − − b ∗ a + z y x Computer Engineering Swiss Federal 3 - 6 Institute of Technology and Networks Laboratory

Application Specification - Example 2 Kahn process network example: hierarchical network of MJPEG application Computer Engineering Swiss Federal 3 - 7 Institute of Technology and Networks Laboratory

Application Specification - Example 3 read(a,b) 1 control flow graph (CFG) 2 done = FALSE what_is_this { repeat until 1 read(a,b); if(a>b) done 4 2 done = FALSE; a>b a<=b 3 repeat { elseif(b>a) a=a-b 4 if(a>b) 5 6 5 a = a-b; a<b a=b 6 elseif(b>a) b=b-a 7 8 done=TRUE 7 b = b-a; 8 else done = TRUE; done? 9 } until done; 9 10 write(a); !done done } 10 write(a) Computer Engineering Swiss Federal 3 - 8 Institute of Technology and Networks Laboratory

Architecture Specification – Example reflects the structure and (key) properties of the underlying platform … and can be done at different abstraction levels example: system-level architecture specification usually a graph notation is used to describe structure annotations to graph elements reflect properties of the underlying platform, e.g., processing frequency Computer Engineering Swiss Federal 3 - 9 Institute of Technology and Networks Laboratory

Mapping Specification - Example mapping relates application and architecture specifications binds processes to processors binds communication between processes to communication paths of the architecture specifies resource sharing disciplines and scheduling Computer Engineering Swiss Federal 3 - 10 Institute of Technology and Networks Laboratory

Example: DFG Application Model basic model: data flow graph and static scheduling data flow graph G P (V P , E P ) Computer Engineering Swiss Federal 3 - 11 Institute of Technology and Networks Laboratory

Example: Architecture Model Computer Engineering Swiss Federal 3 - 12 Institute of Technology and Networks Laboratory

Example: Mapping data flow (all possible) application data flow architecture graph mapping relations graph G P ( , ,E P ) G A ( , ,E A ) E M Computer Engineering Swiss Federal 3 - 13 Institute of Technology and Networks Laboratory

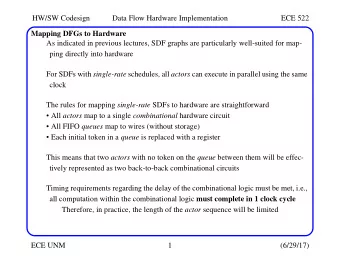

Example: Synthesis Synthesis involves allocation α (subset of V A ) binding β (subset of E M ), i.e., reflecting the mapping of application nodes in V P (functional and communication) onto architectural nodes in V A (processors and buses) mapping scheduling τ , i.e., assigning an order among nodes (e.g., start time) …and ultimately, implementation of ( α , β , τ ) targeted to actual hardware and/or software modules Computer Engineering Swiss Federal 3 - 14 Institute of Technology and Networks Laboratory

Example: … towards Implementation Computer Engineering Swiss Federal 3 - 15 Institute of Technology and Networks Laboratory

Example: … towards Implementation RISC V1 5 V2 V3 RISC SB V6 V7 SB HWM1 V4 application 0 1 21 22 29 30 32 &mapping HWM1 execution schedule implementation Computer Engineering Swiss Federal 3 - 16 Institute of Technology and Networks Laboratory

Mapping Optimization in the Design Flow functional application architecture validation system-level design mapping space exploration loop (typ. automated) system-level search performance algorithm analysis hardware/ complete design space software exploration loop synthesis (typ. manual) final performance analysis Computer Engineering Swiss Federal 3 - 17 Institute of Technology and Networks Laboratory

Mapping Optimization in the Design Flow Often based on iterative interaction between optimization and performance analysis Based on quantitative parameters obtained through estimation, e.g., end-to-end delay, throughput, power, temperature functional application architecture validation system-level design mapping space exploration loop (typ. automated) system-level search performance algorithm analysis hardware/ complete design space software exploration loop synthesis (typ. manual) final performance analysis Computer Engineering Swiss Federal 3 - 18 Institute of Technology and Networks Laboratory

What is ahead? Section 4: Partitioning Some basic methods to assign tasks to computing resources (or communication to networks and busses). Section 5: Multiobjective Optimization Generic method to optimize H/S systems (and other engineering systems) Section 7: Design Space Exploration Application of these methods to design space exploration Computer Engineering Swiss Federal 3 - 19 Institute of Technology and Networks Laboratory

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.