Hardware Description Languages Digital Design Using Verilog always - PowerPoint PPT Presentation

Hardware Description Languages Digital Design Using Verilog always @(posedge clk) begin assign pcinc = pc + 4; > 2 1 2 < 5 : R c : E L 2 S > R A i n o : 1 1 1 for (i=0; i < 31; i = i+1) begin I L L T r u

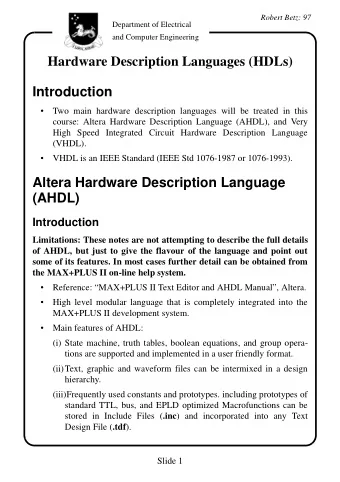

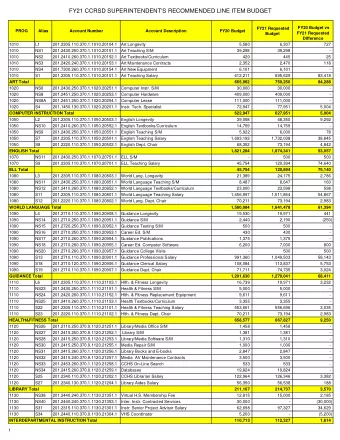

Hardware Description Languages Digital Design Using Verilog always @(posedge clk) begin assign pcinc = pc + 4; > 2 1 2 < 5 : R c : E L 2 S > R A i n o : 1 1 1 for (i=0; i < 31; i = i+1) begin I L L T r u c t < 1 5 0 r O P J n s t o r y R : b F R X A d 0 I M e m 2 W D W E 1 A > 6 R A 2 D 2 0 1 : r W E 3 0 0 < : i s e t L 4 R a R e g R D 2 C S E P C E L 1 F i l e P A S R A W W A W A 1 R D 1 P X 1 > J T E L + 4 2 5 2 : 0 S B + c : < 0 R > ) Z 1 5 : 0 1 W r T ( < S X W C : D R / 0 W ( C ) 1 o r y S X T E L e m + 4 * S A a M C + 4 Z B D a t P R D R Q r I c L U A d o g i A A o l L n t r C o L C S E N F P S E L A L U A 2 R E L A S E L B S E L W D S S E L U F N C + 4 W D A L P 2 W r 1 F 0 W E R E L W A S In the beginning designs involved just a few gates, and thus it was possible to verify these circuits on paper or with breadboards module beta(clk,reset,irq,… Input [31:0] mem_data; endmodule If (done) $finish; 6.884 – Spring 2005 02/04/05 L02 – Verilog 1 6.884 – Spring 2005 02/04/05 L02 – Verilog 2 Hardware Description Languages Hardware Description Languages When designers began working on 100,000 gate designs, these gate-level models were too low- level for the initial functional specification and early high- level design exploration As designs grew larger and more complex, designers began using gate-level models described in a Hardware Description Language to help with verification before fabrication 02/04/05 02/04/05 6.884 – Spring 2005 L02 – Verilog 3 6.884 – Spring 2005 L02 – Verilog 4

Hardware Description Languages Advantages of HDLs Allows designers to talk about what the hardware Designers again turned to HDLs for help – abstract behavioral should do without actually designing the hardware models written in an HDL itself, or in other words HDLs allow designers to provided both a precise separate behavior from implementation at various specification and a framework levels of abstraction for design exploration HDLs do this with modules and interfaces 6.884 – Spring 2005 02/04/05 L02 – Verilog 5 6.884 – Spring 2005 02/04/05 L02 – Verilog 6 Advantages of HDLs Advantages of HDLs Allows designers to talk about what the hardware Allows designers to talk about what the hardware should do without actually designing the hardware should do without actually designing the hardware itself, or in other words HDLs allow designers to itself, or in other words HDLs allow designers to separate behavior from implementation at various separate behavior from implementation at various levels of abstraction levels of abstraction 02/04/05 02/04/05 6.884 – Spring 2005 L02 – Verilog 7 6.884 – Spring 2005 L02 – Verilog 8

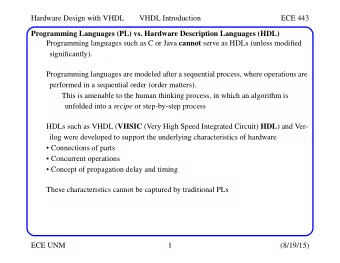

Advantages of HDLs Advantages of HDLs Allows designers to talk about what the hardware Allows designers to talk about what the hardware should do without actually designing the hardware should do without actually designing the hardware itself, or in other words HDLs allow designers to itself, or in other words HDLs allow designers to separate behavior from implementation at various separate behavior from implementation at various levels of abstraction levels of abstraction – Designers can develop an executable functional specification that documents the exact behavior of all the components and Processor Processor Processor their interfaces A B C – Designers can make decisions about cost, performance, power, and area earlier in the design process Network – Designers can create tools which automatically manipulate the design for verification, synthesis, optimization, etc. Memory Memory Bank Bank A B 6.884 – Spring 2005 02/04/05 L02 – Verilog 9 6.884 – Spring 2005 02/04/05 L02 – Verilog 10 A Tale of Two HDLs We will use Verilog … VHDL Verilog Advantages – Choice of many US design teams ADA-like verbose syntax, lots C-like concise syntax of redundancy – Most of us are familiar with C-like syntax – Simple module/port syntax is familiar way to organize Extensible types and Built-in types and logic hierarchical building blocks and manage complexity simulation engine representations – With care it is well-suited for both verification Design is composed of entities Design is composed of modules and synthesis each of which can have which have just one multiple architectures implementation Disadvantages Gate-level, dataflow, and Gate-level, dataflow, and – Some comma gotchas which catch beginners everytime behavioral modeling. behavioral modeling. – C syntax can cause beginners to assume C semantics Synthesizable subset. Synthesizable subset. – Easy to create very ugly code, good and consistent Harder to learn and use, DoD Easy to learn and use, fast coding style is essential mandate simulation 02/04/05 02/04/05 6.884 – Spring 2005 L02 – Verilog 11 6.884 – Spring 2005 L02 – Verilog 12

An HDL is NOT a Hierarchical Modeling with Verilog Software Programming Language A Verilog module includes a module name and an interface in the form of a port list Software Programming Language – Language which can be translated into machine instructions – Must specify direction and bitwidth for each port and then executed on a computer Hardware Description Language – Language with syntactic and semantic support for modeling the module adder( A, B, cout, sum ); A B temporal behavior and spatial structure of hardware input [3:0] A, B; output cout; output [3:0] sum; module foo(clk,xi,yi,done); adder input [15:0] xi,yi; // HDL modeling of output done; // adder functionality always @(posedge clk) begin: cout sum if (!done) begin endmodule Don’t forget if (x == y) cd <= x; else (x > y) x <= x - y; the semicolon! end end endmodule 6.884 – Spring 2005 02/04/05 L02 – Verilog 13 6.884 – Spring 2005 02/04/05 L02 – Verilog 14 Hierarchical Modeling with Verilog Hierarchical Modeling with Verilog A Verilog module includes a module name and an A module can contain other modules through interface in the form of a port list module instantiation creating a module hierarchy – Must specify direction and bitwidth for each port – Modules are connected together with nets – Verilog-2001 introduced a succinct ANSI C style portlist – Ports are attached to nets either by position or by name module adder( input [3:0] A, B, A B module FA( input a, b, cin a b output cout, output cout, sum ); output [3:0] sum ); cin // HDL modeling of 1 bit FA // HDL modeling of 4 bit cout adder // adder functionality // adder functionality endmodule endmodule cout sum c 02/04/05 02/04/05 6.884 – Spring 2005 L02 – Verilog 15 6.884 – Spring 2005 L02 – Verilog 16

Hierarchical Modeling with Verilog Hierarchical Modeling with Verilog A module can contain other modules through A module can contain other modules through module instantiation creating a module hierarchy module instantiation creating a module hierarchy – Modules are connected together with nets – Modules are connected together with nets – Ports are attached to nets either by position or by name – Ports are attached to nets either by position A B A B module adder( input [3:0] A, B, module adder( input [3:0] A, B, output cout, output cout, adder output [3:0] S ); adder output [3:0] S ); cout S cout S FA fa0( ... ); wire c0, c1, c2; FA fa1( ... ); FA fa0( A[0], B[0], 0, c0, S[0] ); FA fa2( ... ); FA fa1( A[1], B[1], c0, c1, S[1] ); FA fa3( ... ); FA fa2( A[2], B[2], c1, c2, S[2] ); FA fa3( A[3], B[3], c2, cout, S[3] ); endmodule FA FA FA FA FA FA FA FA endmodule Carry Chain 6.884 – Spring 2005 02/04/05 L02 – Verilog 17 6.884 – Spring 2005 02/04/05 L02 – Verilog 18 Hierarchical Modeling with Verilog Verilog Basics A module can contain other modules through Data Values Numeric Literals module instantiation creating a module hierarchy 4’b10_11 – Modules are connected together with nets – Ports are attached to nets either by position or by name 0 1 Underscores A B module adder( input [3:0] A, B, X Z are ignored output cout, Base format adder output [3:0] S ); (d,b,o,h) cout S wire c0, c1, c2; Decimal number FA fa0( .a(A[0]), .b(B[0]), representing size in bits .cin(0), .cout(c0), .sum(S[0] ); 32’h8XXX_XXA3 FA fa1( .a(A[1]), .b(B[1]), FA FA FA FA ... endmodule 02/04/05 02/04/05 6.884 – Spring 2005 L02 – Verilog 19 6.884 – Spring 2005 L02 – Verilog 20

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.