Gray-Code Bin arkodierung f ur Zahlen achst l = 0 und r = 2 n 1 - PDF document

Diskretisierung Digitaltechnik Einfache Addierer 4 Arithmetik Carry-Select-Addierer A Conditional-Sum-Addierer Conditional-Sum-Addierer Carry-Look-Ahead Addierer Revision 1.1 Multiplizierer Diskretisierung Diskretisierung Urspr

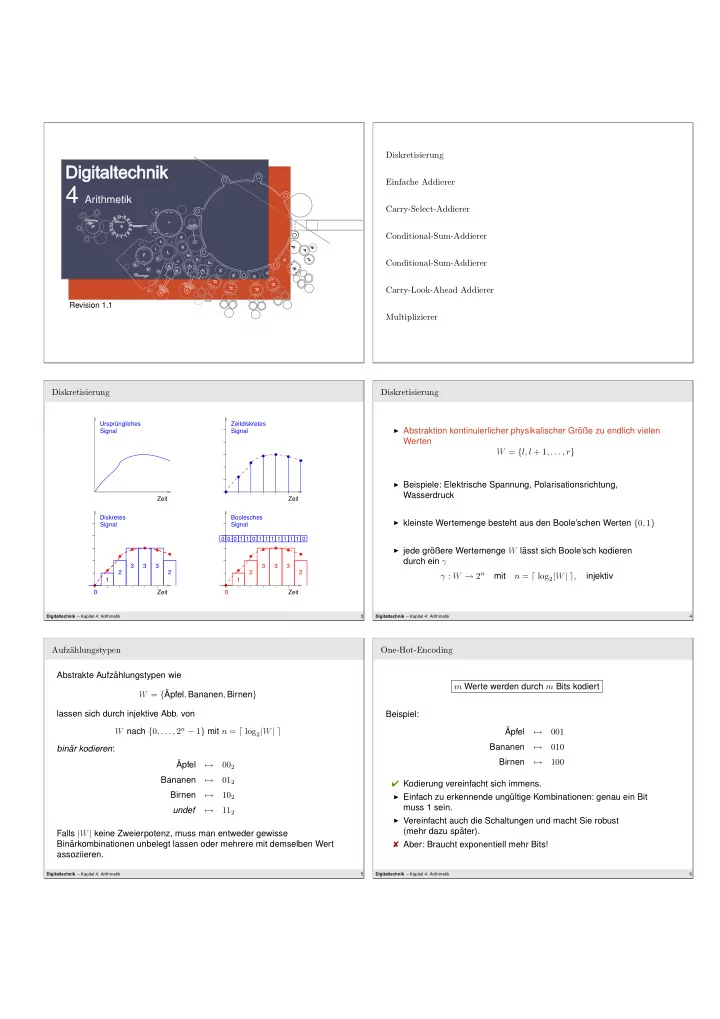

Diskretisierung Digitaltechnik Einfache Addierer 4 Arithmetik Carry-Select-Addierer A Conditional-Sum-Addierer Conditional-Sum-Addierer Carry-Look-Ahead Addierer Revision 1.1 Multiplizierer Diskretisierung Diskretisierung Urspr¨ ungliches Zeitdiskretes ◮ Abstraktion kontinuierlicher physikalischer Gr¨ oße zu endlich vielen Signal Signal Werten W = { l, l + 1 , . . . , r } ◮ Beispiele: Elektrische Spannung, Polarisationsrichtung, Wasserdruck Zeit Zeit Diskretes Boolesches ◮ kleinste Wertemenge besteht aus den Boole’schen Werten { 0 , 1 } Signal Signal 0 0 0 1 1 0 1 1 1 1 1 1 1 0 ◮ jede gr¨ oßere Wertemenge W l¨ asst sich Boole’sch kodieren durch ein γ 3 3 3 3 3 3 2 2 2 2 γ : W → 2 n mit n = ⌈ log 2 | W | ⌉ , injektiv 1 1 0 Zeit 0 Zeit Digitaltechnik – Kapitel 4: Arithmetik 3 Digitaltechnik – Kapitel 4: Arithmetik 4 Aufz¨ ahlungstypen One-Hot-Encoding Abstrakte Aufz¨ ahlungstypen wie m Werte werden durch m Bits kodiert W = { ¨ Apfel , Bananen , Birnen } lassen sich durch injektive Abb. von Beispiel: W nach { 0 , . . . , 2 n − 1 } mit n = ⌈ log 2 | W | ⌉ ¨ Apfel �→ 001 Bananen �→ 010 bin¨ ar kodieren : Birnen �→ 100 ¨ Apfel �→ 00 2 Bananen �→ 01 2 ✔ Kodierung vereinfacht sich immens. Birnen �→ 10 2 ◮ Einfach zu erkennende ung¨ ultige Kombinationen: genau ein Bit muss 1 sein. undef �→ 11 2 ◮ Vereinfacht auch die Schaltungen und macht Sie robust (mehr dazu sp¨ ater). Falls | W | keine Zweierpotenz, muss man entweder gewisse Bin¨ arkombinationen unbelegt lassen oder mehrere mit demselben Wert ✘ Aber: Braucht exponentiell mehr Bits! assoziieren. Digitaltechnik – Kapitel 4: Arithmetik 5 Digitaltechnik – Kapitel 4: Arithmetik 6

Gray-Code Bin¨ arkodierung f¨ ur Zahlen achst l = 0 und r = 2 n − 1 ◮ geg. Wertebereich W = { l, . . . , r } , zun¨ ur Z¨ Logarithmisch viele Bits in | W | , g¨ unstig f¨ ahler. ◮ jedes w ∈ W l¨ asst sich als n -stellige Bin¨ arzahl darstellen: Aufeinanderfolgende Kombinationen unterscheiden sich an einer Bitposition 0 10 �→ 00 2 1 10 �→ 01 2 Motivation wie beim One-Hot-Encoding: robuste und einfache Schaltungen. 2 10 �→ 10 2 3 10 �→ 11 2 100 000 ◮ Wir schreiben � d n − 1 . . . d 0 � f¨ ur die Zahl, die durch d n − 1 . . . d 0 101 001 repr¨ asentiert wird: n − 1 � d i · 2 i � d n − 1 . . . d 0 � := 111 011 i =0 110 010 ◮ Beispiel: � 10110 � = 1 · 16 + 0 · 8 + 1 · 4 + 1 · 2 + 0 · 1 = 22 Man beachte das implizite Festlegen der Stelligkeit n . Digitaltechnik – Kapitel 4: Arithmetik 7 Digitaltechnik – Kapitel 4: Arithmetik 8 Integers: Einerkomplement Integers: Zweierkomplement Zus¨ atzliches Vorzeichen-Bit s n Zus¨ atzliches Vorzeichen-Bit s n wie beim Einerkomplement ur x ≥ 0 werden durch 2 n +1 − 1 − x repr¨ Negative Zahlen − x f¨ asentiert. ur x ≥ 0 werden durch 2 n +1 − x repr¨ Negative Zahlen − x f¨ asentiert. Die ( n + 1) -stellige Bin¨ arzahl s n d n − 1 . . . d 0 im Einerkomplement kodiert Die ( n + 1) -stellige Bin¨ arzahl s n d n − 1 . . . d 0 im Zweierkomplement � n − 1 d i · 2 i die positive Zahl falls s n = 0 kodiert i =0 � n − 1 - � n − 1 d i · 2 i die positive Zahl falls s n = 0 i =0 (1 − d i ) · 2 i falls s n = 1 die negative Zahl i =0 - (1 + � n − 1 i =0 (1 − d i ) · 2 i ) die negative Zahl falls s n = 1 Trick: Bits umdrehen, als Integer negieren! Trick: Bits umdrehen, Eins hinzuz¨ ahlen, als Integer negieren! Beispiele: 00110 im 5-stelligen Einerkomplement kodiert 4 + 2 = 6 Beispiele: 10110 im 5-stelligen Einerkomplement kodiert − (8 + 1) = − 9 00110 im 5-stelligen Zweierkomplement kodiert 4 + 2 = 6 2 n − 1 = 15 01111 gr¨ oßte darstellbare Zahl − (2 n − 1) = − 15 10110 im 5-stelligen Zweierkomplement kodiert − (1 + 8 + 1) = − 10 10000 kleinste darstellbare Zahl 2 n − 1 = 15 01111 gr¨ oßte darstellbare Zahl − 2 n = − 16 Redundante Darstellungen der 0 10 sind 0 . . . 0 und 1 . . . 1 . 10000 kleinste darstellbare Zahl Digitaltechnik – Kapitel 4: Arithmetik 9 Digitaltechnik – Kapitel 4: Arithmetik 10 Integers: Zweierkomplement Integers: Zweierkomplement Beweis: Trivial f¨ ur s n = 0 . ◮ Wir schreiben � d n − 1 . . . d 0 � f¨ ur die Zahl, die im Zweierkomplement n − 1 � 1 · − 2 n + d i · 2 i F¨ ur s n = 1 : � s n d n − 1 . . . d 0 � = durch d n − 1 . . . d 0 kodiert wird i =0 n − 1 � − (2 n − d i · 2 i ) = n − 1 � ◮ Lemma: 2 n = 1 + 1 · 2 i i =0 n − 1 i =0 − (2 n + � − d i · 2 i ) = i =0 n − 1 n − 1 ◮ Definition ohne Fallunterscheidung � � 1 · 2 i + − d i · 2 i ) = − (1 + (Lemma!) i =0 i =0 n − 1 � � s n d n − 1 . . . d 0 � = s n · − 2 n + � � d i · 2 i n − 1 � (1 · 2 i − d i · 2 i ) = − 1 + i =0 i =0 n − 1 � (1 − d i ) · 2 i ) = − (1 + i =0 Digitaltechnik – Kapitel 4: Arithmetik 11 Digitaltechnik – Kapitel 4: Arithmetik 12

Festkommazahlen – Fixpoint Numbers Fließkommazahlen – Floating Point Numbers ( − 1) s · 1 .m · 2 e Darstellen und Runden einer Zahl als ◮ Genauigkeit m der Nachkommastellen wird fixiert, z.B. m = 2 Bin¨ arstellen. Separate Kodierung des Exponenten e im Zweierkomplement, uckrechnen wie Zweierkomplement, Multiplikation mit 2 − m zum ◮ Zur¨ des Vorzeichen-Bit s und Schluss. der positiven Mantisse m . ◮ Umwandlung von Zahlen x in die Festkommadarstellung erfordert Vorzeichen Mantisse 1 Runden: 1 0 0 0 0 0 0 0 1 0 1 0 0 1 0 0 0 6 . 26 10 bei zwei Nachkommastellen (1/4) wird zu 6 . 25 10 = 110 . 01 2 22 21 20 19 18 1 0 Exponent ◮ Das Festkomma (oder der Punkt im Englischen) wird nicht gespeichert: Einfache Genauigkeit (32 Bits): 1 Vorzeichen-Bit, 8 f¨ ur Exponent, 23 f¨ ur Mantisse. 0 0 0 1 1 0 0 1 6.25 in einem Byte mit 2 Nachkommastellen IEEE Standard 754–1985: auch 64, 128 Bits. ◮ H¨ aufig verwendete Zahlendarstellung in Graphikhardware Zus¨ atzlich: Infinity und ung¨ ultige Zahlen (NaN = Not a Number). Digitaltechnik – Kapitel 4: Arithmetik 13 Digitaltechnik – Kapitel 4: Arithmetik 14 Rechnen mit Bin¨ arzahlen Rechnen mit Bin¨ arzahlen ◮ Klar: #include < stdio . h > 00000100 + 00000110 = 00001010 � �� � � �� � � �� � int main ( ) 4 6 10 { char x ; ◮ Aber was ist 5 x=100; x=x+200; 11001000 + 1100100 ? p r i n t f ( ”%d \ n ” , x ) ; � �� � � �� � 200 100 } ◮ Exception werfen? ◮ Saturierung: Ausgabe: 44 11001000 + 1100100 = 11111111 � �� � � �� � � �� � 200 100 255 Digitaltechnik – Kapitel 4: Arithmetik 15 Digitaltechnik – Kapitel 4: Arithmetik 16 Rechnen mit Bin¨ arzahlen ◮ ¨ Uberlauf: 300 = � 100101100 � , also 11001000 + 01100100 = 00101100 = 44! ◮ ¨ http://www.xkcd.org/571/ Uberlauf entspricht modulo-Arithmetik 200 + 100 = 300 mod 256 = 44 mod 256 Digitaltechnik – Kapitel 4: Arithmetik 17 Digitaltechnik – Kapitel 4: Arithmetik 18

Addierer Additions-Algorithmus a 1 1 0 1 1. Summand b 0 1 0 1 2. Summand Σ 0 ◮ einfache arithmetische { 1 ¨ c 1 1 0 1 0 Ubertrag (engl. Carry) P Basis-Operation 2 0 { 3 1 Σ 0 2 { ◮ Hardware Trade-Off: Zeit versus Platz 1 3 s 0 0 1 0 Summe Q 2 3 CO ◮ Skalierbar durch Carry-Weiterleitung CI 1 = Carry Out 0 = Carry In IEEE Schaltsymbol Carry In (CI) und Carry Out (CO) 4-Bit Addierer s k ≡ ( a k + b k + c k ) mod 2 c k +1 ≡ ( a k b k c k ) div 2 + + ( + = Addition in den nat¨ urlichen Zahlen, nicht als + = ODER) Digitaltechnik – Kapitel 4: Arithmetik 19 Digitaltechnik – Kapitel 4: Arithmetik 20 Halb-Addierer (Half Adder) Volladdierer (Full Adder) Addition von drei Bits mit ¨ Ubertragsgenerierung Addition von zwei Bits mit ¨ Ubertragsgenerierung s ≡ ( a + b + i ) mod 2 ≡ a ⊕ b ⊕ i s ≡ ( a + b ) mod 2 ≡ a ⊕ b ≡ ( a + b + i ) div 2 ≡ a · b + a · i + b · i o o ≡ ( a + b ) div 2 ≡ a ∧ b a b i o s a b i a b 0 0 0 0 0 Blackbox FA Model a b 0 0 1 0 1 Whitebox 0 1 0 0 1 Model Blackbox o s HA Model 0 1 1 1 0 o s o s 1 0 0 0 1 i = carry i n 1 0 1 1 0 o = carry o ut (Datenfluss von oben nach unten, Carry links, Summe rechts) 1 1 0 1 0 1 1 1 1 1 s = s um Digitaltechnik – Kapitel 4: Arithmetik 21 Digitaltechnik – Kapitel 4: Arithmetik 22 Volladdierer Whitebox Model Ripple-Carry Addierer a b c i a b c i a b c i a b a b a b a b a b 3 a b a b a b 7 7 6 6 5 5 4 4 3 2 2 1 1 0 0 i FA FA FA FA FA FA FA FA o s s s s s s s s 7 6 5 4 3 2 1 0 oder oder ◮ L¨ asst sich einfach skalieren (Schema iterativ fortsetzen) ◮ Platz: O ( n ) n Volladdierer f¨ ur Addition von zwei n -Bit Zahlen c o s c o s ◮ Zeit: O ( n ) c o s l¨ angster Pfad (von i nach o ) durchl¨ auft n Volladdierer c o = ab ⊕ (( a ⊕ b ) · c i ) ≡ ab + (( a ⊕ b ) · c i ) ≡ (( a + b ) · c i ) + ab (bei einem 128 Bit Addierer kann das ziemlich lange dauern) s = ( a ⊕ b ) ⊕ c i ≡ ( a ⊕ b ) ⊕ c i ≡ ( a ⊕ b ) ⊕ c i Digitaltechnik – Kapitel 4: Arithmetik 23 Digitaltechnik – Kapitel 4: Arithmetik 24

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.