Gate-All-Around Si Nanowire Transistors (SNWTs) for Extreme - PowerPoint PPT Presentation

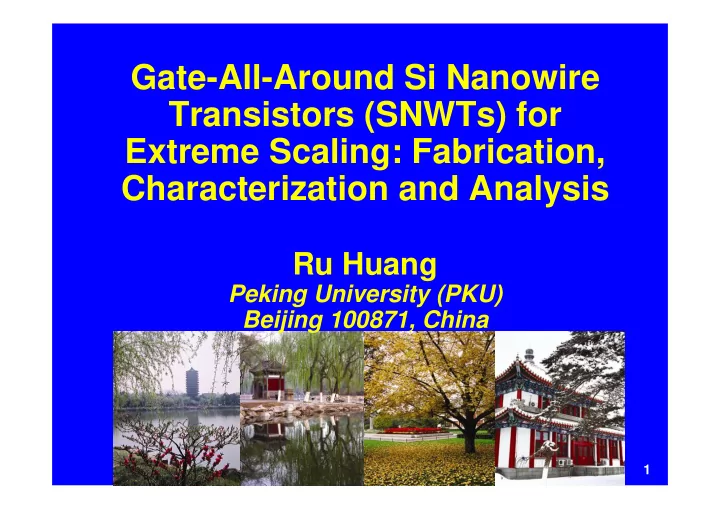

Gate-All-Around Si Nanowire Transistors (SNWTs) for Extreme Scaling: Fabrication, Characterization and Analysis Ru Huang Peking University (PKU) Beijing 100871, China 1 Outline Introduction Fabrication and integration Recent

Gate-All-Around Si Nanowire Transistors (SNWTs) for Extreme Scaling: Fabrication, Characterization and Analysis Ru Huang Peking University (PKU) Beijing 100871, China 1

Outline • Introduction • Fabrication and integration • Recent advances in understanding SNWTs – Parasitic effects – Self-heating effects – Variability • Recent nanowire circuit demonstrations • Summary 2

3 Introduction - 1/5

Introduction - 2/5 We are entering the multi-gate era! • Intel’s 22nm is Tri-gate transistor Source: M. Bohr and K. Mistry, http://www.intel.com • What’s next? 4

Introduction - 3/5 Next: Gate-all-around Nanowire Transistor Scalability Scalability Gate-all-around Gate-all-around Upper Limit Upper Limit Gate Source Drain of T Si / L G of T Si / L G 2 2 All Ext. Ext. Around -gate -gate -gate -gate cylindrical cylindrical rectangular rectangular Double- Double- 1 1 gate gate “the ideal transistor” FinFET FinFET 2/3 2/3 best gate controllability Tri-gate Tri-gate FinFET FinFET relax the strict scaling Number of Gates Number of Gates requirement of t OX and T si 1/2 1/2 2 2 3 3 3+ 3+ 4 4 4+ 4+ FinFET/Tri-gate Gate-all-around Extreme Fin Nanowire Scaling Channels Channels 5

Introduction - 4/5 How to fabricate this device? Did we know all about this kind of device? • We already have the scaling theory for Tri-gate and GAA • But, one cannot simply scale GAA properties to get correct understanding of Si nanowire transistor fundamentally Strongly-confined quasi-1D structure different ! Carrier Carrier transport? transport? Gate Gate Source Source n n Fabrication? a a i i Reliability? r r D D Fabrication? Reliability? Parasitics? Parasitics? Source Ext. Source Ext. Drain Ext. Drain Ext. 3D 3D 3D 3D System System System System Quasi-1D System Quasi-1D System Noise? Noise? Variability? Variability? Self- Self- heating? heating? 6

Introduction - 5/5 Fabricate this device from top-down approach Evaluate the key device characteristics for circuit applications with confined quasi-1D structure • clarify the related physics • find the challenges for optimization • new characterizing techniques • …… Transport? Transport? Parasitics? R. Wang, et al., IEDM 2008 Parasitics? Reliability? Reliability? R. Wang, et al, T-ED 2008 J. Zhuge, et al., T-ED 2008 R. Wang, et al., IEDM 2007 J. Zou, et al, T-ED 2011 L. Zhang, et al., IEDM 2008 Fabrication? Fabrication? L. Zhang, et al., VLSI 2009 C. Liu, et al., T-ED 2010 C. Liu, et al., IEDM 2011 Noise? Y. Tian, et al., IEDM 2007 Noise? Variability? J. Zhuge, et al., EDL 2008 Variability? J. Zhuge, et al., APL 2009 C. Liu, et al, IEDM 2011 Self-heating? J. Zhuge,et al., IEDM 2009 R. Wang, et al, IEDM 2010 GAA SNWTs R. Wang, et al., IEDM 2008 C. Liu et al, IEDM 2011 T. Yu, et al., T-ED 2010 J. Zhuge, et al., T-Nano 2008 R. Wang, et al, T-ED 2011. X. Huang, et al., ISQED 2012 7

Key Messages: Preview • Fabrication and integration: almost Manufacturable • Recent advances in understanding SNWTs – Intrinsic carrier transport: near-ballistic transport 8

Key Messages: Preview • Fabrication and integration: almost Manufacturable • Recent advances in understanding SNWTs – Intrinsic carrier transport: near-ballistic transport 90 GAA SNWT (twin NWs) [x] [this work] bulk MOSFET [x] [1] 80 SiC S/D FinFET [x] [2] NW FETs 70 [3] plannar DG MOSFET [x] [4] bulk MOSFET (simulation) [x] 60 Tri-gate SNWT (single NW) [x] [5] B SAT (%) 50 40 Double-gate FETs 30 [1] J. Jeon, et al., VLSI 2009, p. 48 20 Planar [2] T.-Y. Liow et al., IEDM 2006, p. 473 10 [3] V. Barral et al., Solid-State Electron., bulk FETs 51, p. 537, 2007. 0 [4] Y. Taur et al., IEDM 1998, p. 789 500 10 100 [5] S.D Suk et al., VLSI 2009, p. 142 L G (nm) • Better B SAT than planar and double-gate devices 9

Key Messages: Preview • Fabrication and integration: almost Manufacturable • Recent advances in understanding SNWTs – Intrinsic carrier transport: near-ballistic transport – Low-frequency noise: slightly degraded and fluctuated – Parasitic effects (R and C): should be optimized – Self-heating effects: observable when d NW <14nm – Variability: holds the record low (static) variations – Reliability: HCI is OK, but NBTI needs more studies • Recent nanowire circuit demonstrations: On the way – SRAM, ring oscillator, current mirror… • Other benefits for 3D integration, MtM applications… • Summary: We are facing a great opportunity! 10

Key Messages: Preview • Fabrication and integration: almost Manufacturable • Recent advances in understanding SNWTs – Intrinsic carrier transport: near-ballistic transport – Low-frequency noise: slightly degraded and fluctuated – Parasitic effects (R and C): should be optimized – Self-heating effects: observable when d NW <14nm – Variability: holds the record low (static) variations – Reliability: HCI is OK, but NBTI needs more studies • Recent nanowire circuit demonstrations: On the way – SRAM, ring oscillator, current mirror… • Other benefits for 3D integration, MtM applications… • Summary: We are facing a great opportunity! 11

Outline • Introduction • Fabrication and integration – based on bulk (our focus) – based on SOI – with stacked NW channel • Recent advances in understanding SNWTs – Parasitic effects – Self-heating effects – Variability • Recent nanowire circuit demonstrations • Summary 12

Top-down process for SNWTs • Key points – NW formation – NW releasing or suspending LETI PKU P P TiN o o l l y y - - G G a a t t e e Poly Silicon Poly Silicon IBM SiO 2 BOX BOX S. Bangsaruntip Oxide Oxide NUS 10 nm Silicon Nanowire 10 nm Silicon Nanowire et al., IEDM, 2009 SNW SNW SNW SNW Gox Gox Gox Gox Si Purdue Oxide Oxide Oxide Oxide IBM Samsung NUS 10 nm Silicon Nanowire 10 nm Silicon Nanowire 10 nm Silicon Nanowire 10 nm Silicon Nanowire TIT IEDM, 2005 IEDM, 2006 IEDM, 2007 C. Dupré et al ., Samsung NUS PKU IEDM, 2008 LETI Sato S, et al., SSE, 13 2010, TIT

Bulk SNWTs - Samsung method HM trimming HM Trimming for NW definition diameter = 10nm t OX =3.5nm SiGe/Si stack epi for releasing TiN metal-gate 14 S.D.Suk et al., IEDM, 2005

Self-aligned bulk SNWTs by epi- free compatible process based on bulk substrate NW originally defined by e-beam, thinning and cylinder channel shaping by self-limiting oxidation and annealing NW released by isotropic etch with HM Y. Tian et al., IEDM, 2007, PKU 15

Oxide Oxide Oxide Oxide S S o o u u r r c c e e D D r r a a i i n n Si Substrate Si Substrate Gate trench Nitride fin patterning & etching after oxide S/D implantation deposition Nitride spacer formation Silicon fin etching 16

Silicon etching Si etching under surrounding fin channel channel BPT(bottom parasitic Hard mask removal transistor) Stopper layer 17

18 Gate oxidation &Poly-Si gate formation • diameter = 10nm • Poly gate • t OX =5nm Cylindrical shaping

NW formation NW shaping and diameter controlling Patterning for Oxidation original channel (Temperature & time) rr Si Traded with Oxidation SiO 2 retardation effect c c b b a a Increasing oxidation time: from triangle to circle 19

Experimental results of NWFETs Single wire Source Source Damascene Damascene Gate Groove Gate Groove Drain Drain Y. Tian et al., IEDM, 2007, Multiple wire PKU 20

Current mirror (CM) based on SNWTs Single NW 2T CM cascade CM Multi NW adjust current ratio R.Huang et al.,T-ED,2011,PKU with NW number 21

Testing results symbols: results lines: linear fitting current ratio (I OUT :I IN ) I IN =8 A Inversion Inversion 8 20 1:2 I IN =6 A V OUT =0.3~1.2V 6 1:1 I OUT ( A) 4:1 I OUT ( A) output voltage swing I IN =4 A 10 4 I IN =2 A 2 0 lines: 2-T PCM symbols: 2-T NWCM 0 0.0 0.2 0.4 0.6 0.8 1.0 1.2 0 2 4 6 8 10 V OUT ( A) I IN ( A) OVC(%)=100( I OUT /I OUT )/ V OUT OVC NW CM Planar CM ~ 0.2% ~ 5.7% 2T ~ 0.05% ~ 1% cascade 22

Outline • Introduction • Fabrication and integration • Recent advances in understanding SNWTs – Parasitic effects (R par and C par ) • dominant factors in R par and C par – Self-heating effects SNWTs C parasitic C gc – Variability 100% Capacitance percentage • Recent nanowire circuit demonstrations 80% • Summary 60% 40% 20% 0% 10nm 15nm 25nm 32nm gate length 23

Parasitic R and C in GAA SNWTs • SNWT is worse than planar devices R sd R sd and FinFETs R ext – larger and dominant SDE series resistances – larger outer fringing capacitances 24

Parasitic capacitances in SNWTs C parasitic = C of + C if + C ov + C side C of = C of_gsd + C of_gex • A predictive model for parasitic C in SNWTs has been developed* 25 *Jibin Zou et al., T-ED, vol. 58, no. 10, Oct. 2011,PKU

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.