Front-end Electronics and Data Acquisition in Particle Physics Igor - PowerPoint PPT Presentation

Front-end Electronics and Data Acquisition in Particle Physics Igor Konorov Institute for Hadronic Structure and Fundamental Symmetries (E18) Technical University of Munich Department of Physics Advanced Workshop on Modern FPGA-Based

Front-end Electronics and Data Acquisition in Particle Physics Igor Konorov Institute for Hadronic Structure and Fundamental Symmetries (E18) Technical University of Munich Department of Physics Advanced Workshop on Modern FPGA-Based Technology for Scientific Computing ICTP Trieste

Plan Motivation DAQ and Frond-end electronics Data Processing in FPGA Continuous DAQ Intelligent FPGA-based Data Acquisition System

CERN Accelerator and Experiments

CERN Accelerators LHC Experiments • CMS • ATLAS • LHCb • ALICE • TOTEM, LHCf, MeEDAL Fixed Target Experiments • COMPASS • NA61/SHINE • NA62 • DIRAC • LOUD • …

LHC CMS Experiment

CERN Accelerators

LHC CMS Experiment

CMS Experiment 3 other LHC experiments - ATLAS - LHCb - ALICE

COMPASS Experiment

FPGAs in High-Energy Physics 1. Detector Front-End Electronics (FEE) TDC ADC • • Zero Suppression Pedestal Calculation • • Time stamp assignment Signal detection Reduction • Feature Extraction Steps Data • Signal Amplitude • Signal Time 2. Data Acquisition and (Sub-)Event Building 3. Trigger Logic

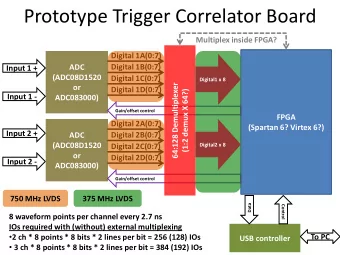

Data Acquisition System The process of sampling detector signals Conversion to digital form Data processing Transmission to PC for further processing, visualization, and storage Transducer Volta ltage Digital Curr rrent Amplifier Digitizer Logic Front-End Electronics FPGA tasks DAQ Glue logic Control and synchronization Data processing Computer interface

Experiment : Electron Energy Measurement Electromagnetic Calorimeter Scintillation Scintillation Counter 1 Counter 2 e‾ Curr rrent FPGA Digitizer TRIGGER TRIGGER – define time when detector signal to be measured Why read only when trigger and not continuously ? Not feasible to measure continuous data flow Not feasible to transmit such amount of data Not feasible to sore such amount of data

DAQ Architecture in Particle Physics Acquisition Slow Control PCIe Ie Etherne rnet Inhibit Thr Trigger igger Logic gic Delay ay cable bles ADC Trigger T wait ADC T read Readout ADC Front-End Tread Tdead = Twait + Tread

DAQ Architecture in Particle Physics Acquisition Slow Control PCIe Ie Etherne rnet Inhibit Thr Trigger igger Logic gic Delay ay cable bles ADC Trigger T wait ADC T read Readout ADC Front-End Tread Tdead = Twait + Tread

Efficiency of data taking RO Sequence : Trigger – > Busy – Read Out -> Release Busy (Ready for next event) = T busy Probability of events described by Poisson distribution 𝑟 𝑘 𝑢 = 𝑠(𝑠𝑢)𝑘−1𝑓−𝑠𝑢 𝑟 1 𝑢 = 𝑠𝑓 −𝑠𝑢 j = 1 , if 𝑘−1 ! J – number of triggers and r – trigger rate A rule of thumb: 𝑈𝑐𝑣𝑡𝑧 Dead Time = λ Tbusy – DAQ busy time λ – average time between triggers Tav >> Tbusy Example: 1kHz => λ = 1ms Tbusy Tbusy = 50 useconds DeadTime = 0.05/1 = 0.05 or 5%

Pipe Line Front Ends Multi Event buffer: de-randomization buffer Trigger 100MHz CLK CLK FIFO Logic ADC FIFO FIFO FIFO for N events Trigger CLK 100MHz CLK FIFO ADC Logic FIFO FIFO FIFO for N events Input : Poisson distribution Output : more like a Gaussian centered around average value

DAQ efficiency vs FIFO Depth DAQ Efficiency Trigger rate/DAQ rate capability

Multi Channel Data Flow Trigger Front-End Logic Data Concentrator PC Event Builder PC

Time Reference ∆ T Classical method: Detector – TRIGGER is a reference Signals ∆ T SIGNAL time is measured respectively to TRIGGER – Trigger Signal Alternative method for big experiments: – Distribute CLOCK , why clock? t sig T0 • Easier to distribute with very low jitter – Measure absolute time respectively to CLOCK phase Detector N s t sig Signals T sig = N s T clk + t sig t trg Trigger T trg = N t T clk + t trg Signal Common CLOCK Clock and Data are encoded and transmitted from single source to multiple destinations Encoding Data

Multiple Trigger Levels Trigger Trigger Trigger Front-End Front-End Front-End Logic Logic Logic Data Data Data Concentrator Concentrator Concentrator PC PC Trigger PC Trigger Logic Logic Event Event Event Builder Builder Builder Trigger PC PC PC Logic Storage/CDR Storage/CDR Storage/CDR

DAQ Elements FPGA Front-end electronics, detector specific Conversion of detector analog signal to digital form Derandomization D ata processing: signal detection, extraction of signals’ parameters Time and/or Amp… Trigger Logic reduce amount of stored data define time when of interesting event Trigger Distribution system => Time Distribution System Slow Control System Control and monitoring of PS, Gas system, Temperature, Humidity,… Programming of Front-ends Acquisition System => Event builder Data acquisition – moving data from FE to PCs Data flow control Real time Software Run control

FRONT-END ELETRONICS DATA PROCESSING

FPGAs in High-Energy Physics 1. Detector Front-End Electronics (FEE) TDC ADC • • Zero Suppression Pedestal Calculation • • Time stamp assignment Signal detection Reduction • Feature Extraction Steps Data • Signal Amplitude • Signal Time 2. Data Acquisition and (Sub-)Event Building Pipeline Architecture Reliability 3. Trigger Logic High-speed Advanced event identification abilities Doublet/triplet finder Track fitter

ADC readout – Avalanche Photodiodes (APDs) • Semiconductor detector: Reverse- biased p-n-junction • Primary photoelectrons accelerated in electric field → avalanche • Created charge proportional to deposited energy • suitable for detection of every ionizing radiation

ADC readout – Preamplifier and Shaper Created charge proportional to energy deposit Sampling FPGA Amplitude measurement ADC CLK Signal Time defines EVENT TIME > 10 MHz 12-16 bit • Charge-sensitive (CS) 30 keV proton preamplifier 20 keV proton • Shaping: CR differentiator and RC integrator

Noise on Signals 𝜈 𝑡/𝑜 = Important quantity: 𝜏noise 𝜈 𝜏 Challenges in presence of noise Data reduction steps • • Averaging over large number of samples Pedestal Calculation • • Signal detection Discrimination between signals and noise (signal-to-noise ratio) • • Feature Extraction Precise determination of amplitude or signal shape

ҧ Pedestal Calculation – Low Pass Filter • Implementing a low pass filter means averaging over number of samples N: 𝑂−1 𝑡 𝑗 σ 𝑗=0 𝑡 = 𝑂 It is convenient to choose 𝑂 = 2 𝑛 so that division can be implemented as a bit shift. (e.g. a/8 = a >> 3) o Measurement of pedestal when there is no signal - Very precise method 2 𝑂−1 𝑡 𝑗 𝑂−1 𝑡 𝑗 2 Allows to determine noise distribution (RMS): 𝜏 2 = 𝑦 2 − ҧ 𝑦 2 = σ 𝑗=0 σ 𝑗=0 − - 𝑂 𝑂 o Measurement in the presence of signals: accuracy of measured value depends on signal rate

ҧ Pedestal Calculation – Baseline Follower • Continuous calculation of pedestal during data taking with signals and exclude signal samples for calculation: Σped = Σped + 𝑡 𝑗 − ҧ 𝑡 Τ 𝑡 = Σped 𝑂 • Allows for continuous calculation of RMS of noise: 𝑡 2 − 𝜏 2 Σdiff = Σdiff + 𝑡 𝑗 − ҧ 𝜏 2 = Τ Σdiff 𝑂 Evolution of pedestal and noise RMS at the startup

Signal Detection Conditions 𝑡 𝑗 > thr 1. Amplitude over threshold: σ 𝑡 𝑗 𝑂 > thr 2. Window over threshold: 3. Difference between consecutive samples over threshold: σ 𝑡 𝑗 − 𝑡 𝑗−1 > thr 4. Window over baseline: 5. For baseline follower and continuous RMS calculation: 𝑡 𝑗 − ҧ 𝑡 > 𝑦 ∙ 𝜏 ∧ 𝑡 𝑗+1 − ҧ 𝑡 > 𝑦 ∙ 𝜏 ∧ 𝑡 𝑗+2 − ҧ 𝑡 > 𝑦 ∙ 𝜏 ∧ ⋯ ∧ 𝑡 𝑗+𝑜 − ҧ 𝑡 > 𝑦 ∙ 𝜏

Comparison Between Algorithms Algorithm 3 Algorithm 4 Areas where trigger condition is fulfilled are highlighted. S/N = 6 Parameter for algorithm 3: N = 15 Parameter for algorithm 4: length of averaging wiondows = 16, distance = 30

Feature Extraction – Signal Time Extraction • Time reference – sampling clock • Signal time = coarse time & fine time • Coarse time - sample number • Fine time - fraction of clock period • Algorithms: • Leading edge discriminator = time of the first sample above threshold Constant fraction discriminator = time of 1 st sample above fraction of max amplitude • Constant fraction algorithm Leading edge algorithm introducing walk

Signal Time Extraction – Constant Fraction Discriminator Difference of two signals 𝐶 𝑗 • Scaled samples 𝑔 ∙ 𝑡 𝑗 • Delayed samples 𝑡 𝑗−𝑢 • • Zero crossing defines signal time • Coarse time = i if B i < 0 and B i+1 > 0 𝐶 𝑗 Fine time 𝑒𝑢 = 𝐶 𝑗 −𝐶 𝑗+1 ∙ 𝑢 𝑑𝑚𝑙 •

Digital Constant Fraction Discriminator Additional signal compared to original: Time measurement: • • Delay of 2 samples Subtraction of delayed signal from original • • scaled Interpolation of zero crossing

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.