for or FG FGT T El Elec ectroma romagnetic gnetic Ca Calorim - PowerPoint PPT Presentation

Pro rototype type Fr Front-end end Re Readout ut El Elect ctronic ronics s for or FG FGT T El Elec ectroma romagnetic gnetic Ca Calorim rimeter eter Maharna arnab b Bhattach achar arjee Indian Institute of Technology

Pro rototype type Fr Front-end end Re Readout ut El Elect ctronic ronics s for or FG FGT T El Elec ectroma romagnetic gnetic Ca Calorim rimeter eter Maharna arnab b Bhattach achar arjee Indian Institute of Technology Guwahati

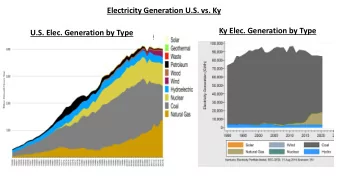

FGT ECAL FGT ECAL has three components: Forward ECAL, Backward ECAL and the Barrel ECAL ECAL is required for identification of EM showers (e - / e + and Gamma showers) & for reconstruction of neutral hadrons such as pi0 ECAL modules are made of alternating layers of lead and plastic scintillators Each of the extruded plastic scintillator bars of such layers are readout by a WLS fibre and photon counters (MPPCs), attached at both ends Proposed Fine-Grained-Tracker (with ECAL modules) for DUNE Near Detector T2K Near Detector (ND280) ECAL

Photon Counter and readout We propose to use MPPCs to readout the Simulation and MPPC characterization is scintillator bars required to ensure MPPC model meets the design requirement MPPCs (Multi-Pixel Photon Counters) are used in the T2K ECAL Similar MPPCs (Hamamatsu S13360-1350CS ) can be adopted for DUNE-ECAL. ― ~56,000 (Hamamatsu S10362-13-050C ) used ― 1.3 x 1.3 mm 2 active area, 667 pixels (50 μ m ― 1.3 x 1.3 mm 2 active area, 667 pixels (50 μ m pixel pitch), ceramic device pixel pitch), ceramic device ― Improved Gain (1.7 x 10 6 ) at lower V O ~53 V ― Gain (7.5 x 10 5 ) with V O ~70 V ― better PDE at 450 nm: ~40 % (270 – 900 nm ― Photon Detection Efficiency ( PDE ) at 550 spectral range) nm: ~25 % ― Lower Dark count rate: 270 kcps (max.) at ― Dark count rate: < 1.3 Mcps (25° C) at threshold 0.5 p.e. threshold 0.5 p.e. MPPC (left) Typical schematic model (right)

Photon Counter and readout Simulation of the MPPCs attempted to determine the electrical characteristics for comparison during characterization Electrical model of MPPC and typical response below for certain p.e. events with afterpulse + crosstalk Quenching resistance R q extracted from I-V curve of forward biased MPPC experimentally, similarly other parameters of MPPC such as diode & parasitic capacitances, etc. [C d ,C q , R d …]

Photon Counter and readout Calculation of the parameters based on S. From the following parameters we can Seifert’s ( Simulation of Silicon Photomultiplier obtain the signal rise time ― τ r = (C d + C q ). R d .R q Signals, IEEE ‘09 ) approach R d +R q ― Total Charge, Q = (C q + C d ) Δ V Necessary in evaluating recovery times and ― Fired Cells, N p = N tot – N f scintillation pulses ― C dp = C d x N p Also useful to create sub circuits imitating ― R qp = R q / N p p.e. events for designing biasing circuit and ― C qp = C q x N p ― C dTOT = N x C d readout electronics ― C qTOT = N x C q

Photon Counter and readout Off the shelf biasing and readout systems can handle a few MPPCs at a time. Thousands of MPPCs require grouping into Front-End Boards for easier control (case: TripT Front-end Board for the T2K). Similar designs with ASICs used for ATLAS, CMS, ILC, … TFB of T2K-ND280 ECAL (above) and visible placement in design inside the ECAL Approach adopted for the T2K-ECAL TripT Front-end Board

Photon Counter and readout Trip-T is being used by T2K ND280 Investigating whether we can use similar TripT design or alternatives (SPIROC, EASIROC, …) Simulation and testing process for each step of readout ASIC Biasing DAC + Analog HVPS Detector Shaper ADC … Preamplifier Memory MPPC Power requirements Power Supply specifications (ideal): ― Supply Voltage, HV O = 40 – 80 V depending on ― Supply Voltage, V IN = 4.75 ≤ Vs ≤ 5.25V the model ― Output Voltage, V OUT = 40 - 80 V ― MPPC Supply Current, I O = 1.0 mA ― Current Consumption, I IN = 20 mA ― Setting Voltage = ± 5 V ― Output Current, I OUT = 2 mA ― Setting Voltage Res. = 10 mV ― Ripple, V p-p(MAX) = 0.2 mV or better ― Voltage monitor error = ± 10 mV ― Fine adjustable steps res. = 1.8 mV ― Current monitor error = ± 0.05 mA ― Reference Hamamatsu’s C112014-01 Power Supply

HV Power Supply: Options AC - DC ― High noise (ripple factor), bulky (add. filter circuit, current reduction), heating issue considering multiple MPPCs AC - DC then DC-DC converter ― Lower noise, current and heat dissipation; with AC- DC for multiple FEBs Many Switching topologies (SMPS) SMPS using Linear Regulators; ― Linear Regulators : *heat dissipation, loss, … Noisy which increases over longer periods ― Buck ― Boost ― Polarity Inverter Switching Regulator ― … ― MOSFETs with PWM drive

HV Power Supply (SMPS) • Basic Configuration for SMPS using PWM: Maximum Switch Current: Duty Cycle, Efficiency of Converter • (~80%), Inductor Ripple Current Inductor and Rectifier Diode Selection • Output Voltage Setting • Input, Output Capacitor Selection • HVPS simulation using PWM drive for MOSFET; with different component (L, C,) and PWM driver selections. One/two such power module per FEB supporting 16 ch., 32 ch. or more

Biasing DAC Simulation with a μ C + 8-bit DAC for 0 – 5 V biasing Important for step size resolution, delay and cutoff voltage Resolution increases with 12-bit or higher DACs DAC simulation (0-5V) Step size = 100 mV, Delay = 20 ms, without & with cutoff DAC simulation (0-5V) Step size = 20 mV, Delay = 50 ms, without & with cutoff

ASICs Compact, low power option To replace the functions of 4 or 16 ch. readout module (Preamplification, Shaper, DAC, …) The ‘SPIROC’ was found to have suitable specifications (possible Trip-T substitute), more study required ― 36 ch. ASIC. Each ch. charge 1 p.e – 2000 p.e ― 7.2 mm x 4.2 mm ― 5V /3.5V OMEGA chip: SPIROC workflow

Front-end and Readout Electronics • Attempt at designing the HVPS, HV DAC, Preamplification stages with current/voltage sensor, temperature/humidity sensor circuits into modules each with 4 to 16 ch. with good sig- noise ration • Characterization of the MPPCs with those readout modules • Added amplification stages in prototype modules to be tested in the immediate future as needed • Comparing the tested designs/prototypes with existing ASICs (TripT, SPIROC, EASIROC, …) with industry collaboration; Prototyping of module improvement/development of newer ones for single MPPC with HVPS, DAC without the amplification stages • FPGAs (depending on timing resolution, data transfer speed, …) under development specifications study to be done in the near future

Acknowledgements to : My Supervisor Dr. Bipul Bhuyan The Dept. of Physics, IIT-Guwahati Thank You

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.