Efficient Sum of Absolute Difference Computation on FPGAs - PowerPoint PPT Presentation

Efficient Sum of Absolute Difference Computation on FPGAs International Conference on Field Programmable Logic and Application (FPL) 2016 Martin Kumm, Marco Kleinlein and Peter Zipf University of Kassel, Germany Sum of Absolute

Efficient Sum of Absolute Difference Computation on FPGAs International Conference on Field Programmable Logic and Application (FPL) 2016 Martin Kumm, Marco Kleinlein and Peter Zipf University of Kassel, Germany

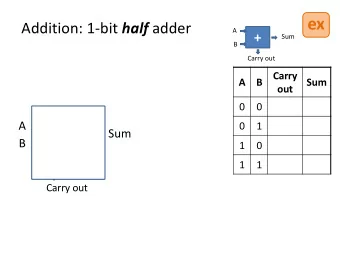

Sum of Absolute Difference (SAD) SAD is an important operation in image and video processing Metric to measure the distance between two blocks of an image Applications are, e.g., motion estimation or stereo matching An R × C SAD operation of two matrices and is defined as: A B R C X X SAD( A , B ) = | a i,j − b i,j | i =1 j =1 2

Previous Work CPA MSB CPA CPA MSB CPA CPA Sequential AD [1] Parallel AD [2] FPGA optimized [3] • SAD is computed with N absolute difference (AD) units • N -input adder tree/compressor tree required • LUTs of best reported circuit grow with 2.5 NB ( B : word size) 3

Proposed SAD CPA CPA MSB MSB Proposed 1 × 2 SAD • SAD is computed with N/2 1x2 SAD units • N/2 -input adder tree/compressor tree required • LUTs of proposed SAD grow with 2.0 NB ( B : word size) 4

Results · 10 4 2 SAD sequential [1] SAD parallel [2] 1 . 5 #LUTs SAD Perri [3] SAD proposed 1 Estimations 0 . 5 0 2 4 6 8 10 12 14 16 18 20 22 24 √ N (a) Required and estimated LUTs 30 LUT reduction (%) actual LUT reduction limit for N → ∞ 20 10 0 2 4 6 8 10 12 14 16 18 20 22 24 √ N (b) Relative LUT reduction compared to [3] 5

Check out uni_ks git branch of https://scm.gforge.inria.fr/anonscm/git/flopoco/flopoco.git See you at the poster at 3:30! Literature: [1] Kanoh, Absolute Value Calculating Circuit Having a Single Adder , US Patent US 4,953,115, 1990 [2] Chirila-Rus (Xilinx Inc.), Determining Sum of Absolute Differences in Parallel , US Patent US 8,131,788, 2012 [3] Perri, Zicari & Corsonello, Efficient Absolute Difference Circuits in Virtex-5 FPGAs , MELECON 2010 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.