Double Drift in DUNE: Ideas for SP vertical drift CERN, 20/6/2019 - PowerPoint PPT Presentation

Double Drift in DUNE: Ideas for SP vertical drift CERN, 20/6/2019 F. Pietropaolo ThGEM-like readout in LAr Motivation: - In the past years a dedicated R&D program was started aiming at replacing the LAr-TPC wire chamber with perforated

Double Drift in DUNE: Ideas for SP vertical drift CERN, 20/6/2019 F. Pietropaolo

ThGEM-like readout in LAr • Motivation: - In the past years a dedicated R&D program was started aiming at replacing the LAr-TPC wire chamber with perforated Multilayer Printer circuit Board, where wires are replaced by copper strips: • Electrons are 2D focused in the PCB holes • Strips in the intermediate layer sense an “induction” signal; • Strips on last plane collect the ionization electrons. - The idea was driven by several possible improvements wrt wire chambers: • the possibility to obtain sharper and better localized induction signals • the possibility of integrating the FE electronics on the PCB • the segmentation / modularity • the possibility to test the full readout before installation. - The design took advantage of the technological development of wide area Thick-Gems at CERN.

The concept • Working principle – Electron trajectories are funneled into holes in plane not in a “slice” like for wires • PRO: – Electric field in the hole is uniform. – Bipolar shape of induction signal is more symmetric. – Induction signal is intrinsically larger than with wires and less blurred because the all the weighting field is limited to a single strip and not distributed on several wires – signals shapes are the same on all successive induction layers (same drift field in the holes) Induction signal • CONS: – focusing EF ratio is high (> ratio of hole Unshielded area to full area) induction – Capacitance of strips is high (PCB dielectric constant and strip width): higher Collection signal el. noise wrt same length wire 3 4 June 2019 HVS-SP PDR Meeting

The reference wire case Signal vs distance from wire Electric field and equi-induction contours Induction from electron trajectories 30 100 Trajectory closest 25 to sense wire 80 20 induction (%) 60 z-coordinate (0-30 mm) Drift distance (mm) 1 mm displacement 40 15 20 Trajectory closest 10 to adjecent wire 0 0 5 10 15 20 25 30 5 Drift time (us) y-coordinate (12 mm) m ) m 4 1 e ( t a n d i r o o 0 c - x 0 5 10 horizontal coordinate (mm) 4 4 June 2019 HVS-SP PDR Meeting

The perforated MultiLayer PCB • Several prototypes have been realized at CERN for signal test and optimization purposes: - 1 Screen plane (not read-out) - 1 induction plane - 1 collection plane • Few mm pitch of the read-out strips • Holes to surface ratio: 30 - 50 % • Hole positioning not critical (many holes per strip) • Hole rim also not critical due to operation in LAr and absence of amplification Ø 0.7 mm 1 mm Grid layer Ø 0.5 mm FR4 ... ... Ind. 3.2 mm strip Drilled Collection Induction hole layer layer

Early tests B. Baibussinov et al, 2018 JINST 13 T03001 • A ML-PCB readout plane was installed and operated, exposed at cosmic rays, in a ICARUS 30 l LAr-TPC at LNL (Italy), 30 cm drift distance: • Characteristics: – 96 collection strips + 96 induction strips + a shielding/focusing plane – 3 mm strip pitch – Hole diameter 0.7mm; hole pitch 1mm – Layer separation thickness: 1.6 mm • It replaced a wire plane with similar pitch for performance comparison purposes • The sensing strips read-out: – ICARUS LNGS version of the warm front end electronics () – through 2m long cables (the dominating input capacitance for the Front End Electronics). 6 4 June 2019 HVS-SP PDR Meeting

Performance from the test run at LNL Collection Indiction • Analysis of cosmic muon tracks: – Collection signal shape similar to that of wires – Similar S/N (dominated Drift time by cable length) – Sharp bipolar Induction signal but too fast for Wire coordinate the ICARUS Preamplifier bandwidth and sampling time (0.4 us) • Further tesr were envisaged to better optimize induction signals: – PCB thickness – New FE electronics Typical signals on a collection (top) and induction (bottom) strips. 7 4 June 2019 HVS-SP PDR Meeting

Performance from the test run at LNL • dE/dx measurement performed wit cosmic muons with the same LAr-TPC, V Grid (V) V Ind (V) V Coll (V) MPV signal (e - equipped with a standard wire chamber /mm) gave a reference Most Probable Value -220 80 380 4550 -220 130 480 4800 value of 5500 e - /mm. -220 180 580 5000 • Scan of voltage across wire planes was performed to study the electrostatic transparency of the perforated ML-PCB • The best value of ~5000 e - /mm was reached at D V=400 V electric bias (limit of the decoupling capacitors) • For the planned further tests new decoupling capacitors were foreseen 8 4 June 2019 HVS-SP PDR Meeting

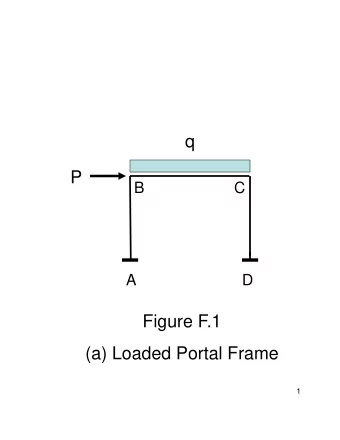

Possible application in DUNE vertical drift • Vertical 6 m Drift LAr-TPC: – horizontal Cathode at the center of the 12 m long vertical direction, – read-out planes at top and bottom • The ML-PCB readout could be accommodated in a simplified supporting structure of the DP CRP detector: – The ML-PCB replaces the full CRP package – No adjustment motors are required: ML-PCB are in Liquid Phase – Electronics and cabling can sit on the upper surface of the PCB – Connections among adjacent tiles can be performed • A similar supporting structure could be implemented for the bottom plane – Electronic cables could be routed to the top of the cryostat along the membrane walls (far from the HV Field Cage) – Possible issues to be investigated concern the evacuation of the heat of the FE • The Field cage could be built similarly to the DP case 9 4 June 2019 HVS-SP PDR Meeting

Design optimization for large surface LAr-TPC • Profiting of the ongoing technological evolution of Thich GEM design and performance, the CERN PCB workshop can easily produce reliable ML-PCB readout planes with size up to 1m x 0.5 m • Larger size could be possible from external producers • The less strict requirements on hole size and rim quality make the production faster and maybe less expensive that for a ThGEM (presently ~ 2kEuro for a 0.5x 0.5 m2) • A careful design of the Front End Connectors and location is however required to minimized dead space at the borders of the plane. • ML-PCB thickness need optimization mainly focusing on signal shape and strip capacitance optimization • The possibility to include a photodetection system, either behind the PCB (Arapuca?) or integrated in some of the PCB holes (direct SiPM) is also under evaluation • In the following months we plan to perform a dedicated R&D with the goal of testing some large size prototypes in the DP cold box at CERN B182, possibly equipped with the present DUNE-SP FE-CE and read-out chain. 10 4 June 2019 HVS-SP PDR Meeting

Thick-GEM vs perforated ML-PBC

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.