Digital Systems 00/100 00/0-- 00/0-- A B F to state A 01/0-- - PowerPoint PPT Presentation

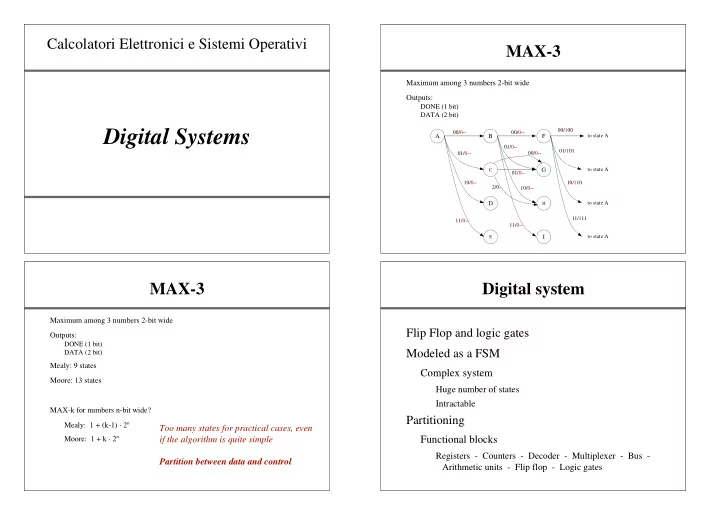

Calcolatori Elettronici e Sistemi Operativi MAX-3 Maximum among 3 numbers 2-bit wide Outputs: DONE (1 bit) DATA (2 bit) Digital Systems 00/100 00/0-- 00/0-- A B F to state A 01/0-- 01/101 00/0-- 01/0-- G to state A C 01/0--

Calcolatori Elettronici e Sistemi Operativi MAX-3 Maximum among 3 numbers 2-bit wide Outputs: DONE (1 bit) DATA (2 bit) Digital Systems 00/100 00/0-- 00/0-- A B F to state A 01/0-- 01/101 00/0-- 01/0-- G to state A C 01/0-- 10/0-- 10/110 2/0- 10/0-- to state A D H 11/111 11/0-- 11/0-- I to state A E MAX-3 Digital system Maximum among 3 numbers 2-bit wide Flip Flop and logic gates Outputs: DONE (1 bit) Modeled as a FSM DATA (2 bit) Mealy: 9 states Complex system Moore: 13 states Huge number of states Intractable MAX-k for numbers n-bit wide? Partitioning Mealy: 1 + (k-1) · 2 n Too many states for practical cases, even Moore: 1 + k · 2 n if the algorithm is quite simple Functional blocks Registers - Counters - Decoder - Multiplexer - Bus - Partition between data and control Arithmetic units - Flip flop - Logic gates

Partitioning Max-3 Datapath n IN Operations on data n 0/10 Control Unit 0/01 0/00 n IN STORE STORE A B C REG CLK Control signals 1/01 1/01 MAJ OUT 1/11 To drive the datapath Control DONE Signals n > Input: MAJ Status signals Control Control Datapath Datapath Outputs: DONE, STORE Unit Unit The control unit varies Status OUT MAJ the flow of the CTRL-Unit Signals Datapath algorithm Control Control Data Data Inputs Outputs Inputs Outputs Calcolatori Elettronici e Sistemi Operativi Datapath Registers Basic components: memory elements Datapath Operations on data stored in registers Register Transfer operations Description at “ Register Transfer Level ” (RTL)

RTL Description n-bit register n Registers set n-1 2 1 0 load Available operations on data stored in registers n Controller that manages the execution flow D D D load Register Register Requirements: load IN OUT D Component that stores data for unlimited clock cycles CLK The store operation is regulated by a dedicated control signal ( load ) load=1 store input data load=0 keep the data already stored Simple Basic block: IN OUT D Timing issues: load Logic gate on the clock tree Flip flop D (with load input) CLK Requirement: load 0 � 1 only when clk=0 Flip flop D (without load input) load Stores data at each clock cycle No timing issues Use a gate to mask the flip-flop's clock (clock-gating) M D U A multiplexer is needed IN OUT Store in the register its own output (feedback) X CLK

Notation Operations operation symbol VHDL equivalent Identifier with only uppercase letters and numbers: registers combinatorial assignment <- <= data transfer between registers <= <= R0, R1, ... , IR sum + + subtraction - - Parentheses: register or signal portion bitwise AND ∧ and Examples: R2(1) : bit 1 of register R2 ∨ bitwise OR or R0 <= R1 + R2 bitwise XOR ⊕ xor R3(3:0) : the 4 least significant bits of R3 bitwise NOT not out <- R1 + R2 + 1 left shift sl sll Square brackets: memory (or register bank) reference right shift sr srl R1 <= R1 + 1 M[0x100] : memory location at address 0x100 portion of data A(3:0) A(3 downto 0) data concatenation || & M[R1] : memory location at address indicated by R1 No multiply and division REGS[12]: register 12 in a register bank called REGS RTL operations Arithmetic operations Actions to transfer the value stored in a register in another register Sum, Subtraction, Increment, Decrement, Complement Example: Implemented by arithmetic circuits R0 <= R1 load R0 with the content of R1 Usually, subtractions are implemented through an adder (2- complement) Increment and decrement, are often implemented using specialized hardware (improved efficiency) The operation involves the whole register content

Arithmetic operations Logical operations Sum, Subtraction, Increment, Decrement, Operations on individual bits of a register Complement and, or, xor, not, ... Examples: R0 <= R1+R2 sum of the content of two registers example: R1 ∧ R2 R0 <= R1 1-complement R0 <= R1+1 2-complement R1 0 1 1 0 0 0 1 1 1 0 1 0 0 1 1 R0 <= -R1 2-complement and R0 <= R1+1 increment R2 0 0 1 1 1 0 0 1 1 1 1 1 0 1 1 R0 <= R1-1 decrement = R0 <-= R1+R2+1 subtraction (through an adder and 2-complement) 0 0 1 0 0 0 0 1 1 0 1 0 0 1 1 R0 <-= R1-R2 subtraction (through an adder and 2-complement) Shift Operations RT structures Shift of the register content Example 1: Operations to be performed: A+B and C+D example: left shift of 2 bits Not concurrently (not in the same cycle) � share adder R1 0 1 1 0 0 0 1 1 1 0 1 0 0 1 1 0 0 A C B D n n n n R1 sel 1 sel 2 0 1 1 0 0 0 1 1 1 0 1 0 0 1 1 0 0 n n Sometimes the last bit “dropped” by the register is stored in another flip-flop. + Bits “entering” in the register sel 1 , sel 2 : left shift: always 0 right shift control signals logical shift: 0 n (form the ctrl-unit) arithmetic shift aritmetico: equal to the most significant bit (MSB) of the register

RT structures RT structures Example 2: Example 3: Operations to be performed: R <= A , R <= X+Y Operations to be performed: R1 <= A , R2 <= A , R3 <= A A A n n n X Y sel n n load 1 load 2 load 3 R1 R2 R3 load R + sel , load: load 1 , load 2 , load 3 : DECO control signals control signals (from the ctrl-unit) 2 Eventually encoded (from the ctrl-unit) load (thus, using a decoder in datapath) RT structures RT through bus Available transfers: all Registers can receive input data from more sources Source and destination are selected through signals S and D Multiplexer Di Sj : Ri <- Rj D0 D1 D2 n Input data are selected through a multiplexer LOAD Bus S0 S1 S2 n R0 A single multiplexer drives a bus which is input of more registers bus Tri-state bus S0 LOAD The bus is driven by tri-state buffers M n n R1 S1 U Other: X S2 Several multiplexer n More buses LOAD Composition of different structures n R2 n

RT through tri-state bus RT through tri-state bus Available transfers: all Available transfers: all Source and destination are selected through signals S and D Source and destination are selected through signals S and D Di Sj : Ri <- Rj Di Sj : Ri <- Rj D2 D1 D0 S0 S1 S2 D2 D1 D0 S0 S1 S2 LOAD EN LOAD L E n n n n R0 R0 LOAD n R bus n E LOAD L n n n n R1 R1 LOAD EN L E LOAD L E n bus R n n n n R2 R2

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.