Di Digi gital tal Ci Circui cuits ts ECS S 371 Dr. Prapun - PowerPoint PPT Presentation

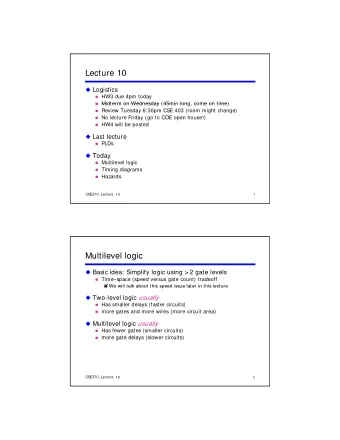

Di Digi gital tal Ci Circui cuits ts ECS S 371 Dr. Prapun Suksompong prapun@siit.tu.ac.th Lecture 10 Office Hours: BKD 3601-7 Monday 9:00-10:30, 1:30-3:30 Tuesday 10:30-11:30 1 Announcement HW4 posted on the course web site

Di Digi gital tal Ci Circui cuits ts ECS S 371 Dr. Prapun Suksompong prapun@siit.tu.ac.th Lecture 10 Office Hours: BKD 3601-7 Monday 9:00-10:30, 1:30-3:30 Tuesday 10:30-11:30 1

Announcement HW4 posted on the course web site Chapter 5: 4(b,c,e), 20a, 22a, 56 Write down all the steps that you have done to obtain your answers. Due date: July 16, 2009 (Thursday) There will be a quiz today. 2

Review NAND gate is a universal gate. NOR gate is a universal gate. 3

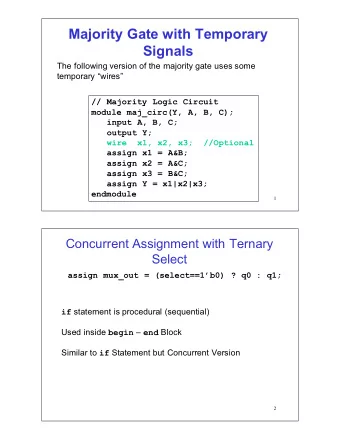

NAND Gate as a Universal Gate NAND gates are sometimes called universal gates because they can be used to produce the other basic Boolean functions. A A A AB B Inverter AND gate A A A + B A + B B B OR gate NOR gate 4

Example Implement the following logic circuit using only NAND gates: C Solution: C Negative-OR NAND C 5

Example Implement the following logic circuit using only NAND gates: It is easy to turn Negative-OR NAND AND-OR Solution: configuration into a NAND- gate-only circuit 6

NOR Gate as a Universal Gate NOR gates are also universal gates and can form all of the basic gates. A A A A + B B Inverter OR gate A A AB AB B B AND gate NAND gate 7

Example Implement the following logic circuit using only NOR gates: Solution: 8

Combinational Logic We studied the theoretical principles used in combinational logic design. We will build on that foundation and describe many of the devices, structures, and methods used by engineers to solve practical digital design problems. A complex circuit or system is conceived as a collection of smaller subsystems, each of which has a much simpler description. 9

Digital System Concept A digital system is an arrangement of the individual logic functions connected to perform a specified operation or produce a defined output. 10

Combinational Building Blocks There are several straightforward structures that turn up quite regularly as building blocks in larger systems. Encoder Decoders Comparators Multiplexers Where can we find these building blocks? 11

Fixed-function IC An integrated circuit (IC) is an electronic circuit that is constructed entirely on a single small chip of silicon. Two broad categories of digital ICs. Fixed-function logic 1. Programmable logic 2. In fixed-function logic , the logic functions are set by the manufacturer and cannot be changed. 12

Fixed-function IC package 13 Cutaway view of DIP (Dual-In-line Pins) chip

Complexity Classifications Fixed-function digital lCs are classified according to their complexity. Small-scale integration (SSI) up to ten equivalent gate circuits on a single chip basic gates and flip-flops. Medium-scale integration (MSI) from 10 to 100 equivalent gates on a chip. encoders, decoders, counters, registers, multiplexers, arithmetic circuits, small memories Large-scale integration (LSI) Very large-scale integration (VLSI) Ultra large-scale integration (ULSI) 14

SSI 74x00 15

MSI For the next couple lectures, we will study most of these 74-series MSI. 16

7447 7442 7485 A OA A0 O 0N B OB O 1N B0 MSI C OC O 2N A1 D OD O 3N A B1 LT N OE O 4N ALB O B A2 R B I N OF O 5N AE B O C B2 B I N OG O 6N AG B O D A3 R B O N O 7N B3 B C D T O 7S E G O 8N ALB I inst2 O 9N AE B I BCD TO DEC AG B I inst1 C O M P AR AT O R inst3 74138 74139 74147 74148 Y10N 1N Y0N 0N A1 Y11N 2N A Y1N 1N B Y2N B1 Y12N 3N 2N E O N A2 Y13N 4N AN C Y3N 3N G S N G1 Y4N B2 Y20N 5N BN 4N A0N G 1N Y21N 6N CN G 2AN Y5N 5N A1N G 2B N Y6N G 2N Y22N 7N DN 6N A2N Y23N 8N Y7N 7N 9N 3:8 D E C O D E R 2:4 D E C O D E R E I N inst4 inst5 E N C O D E R E N C O D E R inst6 inst7 74151 74154 74157 74280 74283 O 0N A S E L A C I N O 1N A1 A1 B B O 2N C B1 C B1 S U M 1 O 3N A2 A2 S U M 2 D0 D O D D Y1 O 4N D1 B2 E E VE N B2 S U M 3 Y2 O 5N A3 A3 S U M 4 D2 Y A F Y3 O 6N B3 B3 C O U T D3 WN B Y4 G O 7N A4 A4 D4 C H O 8N B4 B4 D5 D I O 9N D6 G 1N GN P AR I T Y G E N . 4 B T I AD D E R inst10 inst11 O 10N D7 G 2N M U LT P I LE X E R inst9 O 11N GN O 12N M U LT I P LE X E R inst8 O 13N O 14N O 15N 17 D E C O D E R in s t

Simple Decoder A decoder is a logic circuit that detects the presence of a specific combination of bits at its input. Two simple decoders that detect the presence of the binary code 0011 are shown below. The first has an active HIGH output; the second has an active LOW output. A 0 A 0 X X A 1 A 1 A 2 A 2 A 3 A 3 Active HIGH decoder for 0011 Active LOW decoder for 0011 (A 0 is the LSB and A 3 is the MSB) 18

Exercise Assume the output of the decoder shown below is a logic 1. What are the inputs to the decoder? A 0 = 0 A 1 = 1 1 A 2 = 0 A 3 = 1 19

Binary-to-Decimal Decoder The binary-to-decimal decoder shown here has 16 outputs – one for each combination of binary inputs. The bubbles indicate active- LOW outputs. Bin/Dec 0 1 1 1 2 1 3 1 4 1 5 1 A 0 1 6 1 A 1 4-bit binary Decimal 1 7 1 outputs input 8 1 A 2 0 9 1 A 3 1 10 1 11 0 12 1 13 1 14 1 15 1 20

Application: Port Address Decoder Decoder can be used in computers for input/output selection. Computers communicate with peripherals by sending and/or receiving data through what is known as input/output (I/O) ports. A decoder can be used to select the I/O port so that data can be sent or received from a specific external device. 21

2:4 decoder 2-to-4 line decoder with enable input 22

Exercise Find the truth table of the 1-to-2 line decoder below. Then, implement the 1-to-2 line decoder. Y0 I Y1 23

Most MSI decoders were originally 74x139: Dual 2:4 Decoder designed with active- LOW output. Two independent 2:4 decoders The outputs and the enable (E) input are active-LOW . When E is HIGH all outputs are forced HIGH. E O 3 Notice that all of the signal names inside the symbol outline are active-HIGH, and that bubbles indicate 24 active-LOW inputs and outputs.

74x139 25

74x139: Logic diagram Active- LOW Enable This is a usual 2:4 decoder. 26 Active-LOW output because NAND gates are used instead of AND gates

Example: Building a larger decoder Construct a 3-to-8 decoder from two 2-to-4 decoders Notice that this part is equivalent to a 1:2 decoder. How can we add an active-HIGH enable input? Low order bits (A 1 , A 0 ) select within decoders. High order bit (A 2 ) controls which decoder is active. 27

Building larger decoder from smaller ones To construct ( k + n )-to-2 n + k decoders, can use 2 n of k -to-2 k decoders with enable input and 1. one n -to-2 n decoders. 2. The connections are: For each of the k -to-2 k decoder with enable input, all have k input we put in A 0 …A k-1 . The enable line of the r th decoder is connected to D r of the n -to-2 n decoders. The inputs of the n -to-2 n decoder get A k to A n+k-1 . Basically, each k -to-2 k decoder works on the last k bits. We use the first n bit, via the n -to-2 n decoder, to select which one (and only one) of the k -to-2 k decoders will be enabled. 28

Example Construct a 4:16 decoder with an active-LOW enable from three 2:4 decoders. 29

74x138: 3:8 Decoder Active-LOW outputs Three enable inputs. 30

Example Construct a 4:16 decoder with an active-LOW enable (EN) from two 74x138 decoder. 31

Example Construct a 5:32 decoder with two active- low enable and one active-high enable from four 74x138 and one 74x139. 32

74x154: A LOW level on each 4:16 Decoder chip select input is required to make the enable gate output (EN) HIGH. Alternative logic symbol 74154 O0N O1N O2N O3N O4N O5N A O6N B O7N C O8N D O9N G1N Include two active-LOW chip select (CS) O10N G2N O11N lines which must be at the active level to O12N O13N enable the outputs. These lines can be used O14N O15N to expand the decoder to larger inputs. 33 DECODER inst

5:32 Decoder 34

Decoder as general purpose logic Any combinational circuit with n inputs and m outputs can be implemented with an n -to-2 n -line decoder and m OR gate Observe that the 3:8 decoder generates all possible minterms. 35

Example Implement a full adder circuit with a decoder and OR gates S = X,Y,Z (1,2,4,7) C = X,Y,Z (3,5,6,7) Inputs Outputs S X Y Z A B C C S C in out 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 36

Other Decoders In general, a decoder converts coded information, such as binary number, into non-coded form. Later, (if time permitted) we will talk about other types of decoder. 37

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.