Unit 7 Minterm and Canonical Sums 2- and 3-Variable Boolean Algebra - PowerPoint PPT Presentation

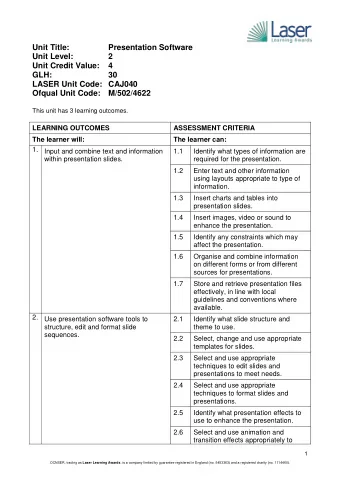

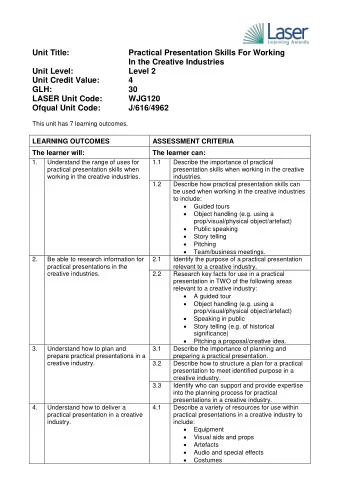

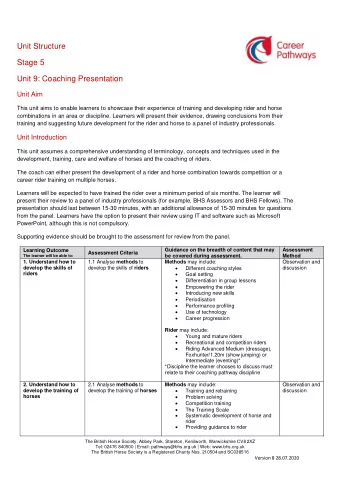

7.1 Unit 7 Minterm and Canonical Sums 2- and 3-Variable Boolean Algebra Theorems DeMorgan's Theorem Simplification using Boolean Algebra 7.2 Duality As we progress in this unit, remember and look for the idea of duality at work

7.1 Unit 7 Minterm and Canonical Sums 2- and 3-Variable Boolean Algebra Theorems DeMorgan's Theorem Simplification using Boolean Algebra

7.2 Duality • As we progress in this unit, remember and look for the idea of duality at work • Duality said a new, true statement could be found from another by swapping: – 0 1 and – AND OR X • 0 = 0 X + 1 = 1 Original equation Dual

7.3 CHECKERS / DECODERS

7.4 Gates • Gates can have more than 2 inputs but the functions stay the same – AND = output = 1 if ALL inputs are 1 • Outputs 1 for only 1 input combination – OR = output = 1 if ANY input is 1 • Outputs 0 for only 1 input combination X Y Z F X Y Z F 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 x x F y F y 0 1 1 0 0 1 1 1 z z 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 1 1 1 1 1 3-input AND 3-input OR

7.5 Checkers / Decoders • An AND gate only outputs ‘1’ for 1 combination – That combination can be changed by adding inverters to the inputs – We can think of the AND gate as “checking” or “decoding” a specific combination and outputting a ‘1’ when it matches. X Y Z F X Y Z F 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 x x F F y y 0 1 1 0 0 1 1 0 z z 1 0 0 0 1 0 0 0 1 0 1 1 1 0 1 0 AND gate decoding AND gate decoding 1 1 0 0 1 1 0 0 (checking for) (checking for) combination 000 combination 101 1 1 1 0 1 1 1 0

7.6 Checkers / Decoders • Place inverters at the input of the AND gates such that – F produces ‘1’ only for input combination {x,y,z} = {010} – G produces ‘1’ only for input combination {x,y,z} = {110} X Y Z F X Y Z G 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 1 0 1 0 0 x x F G y y 0 1 1 0 0 1 1 0 z z 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 AND gate decoding AND gate decoding 1 1 0 0 1 1 0 1 (checking for) (checking for) combination 110 combination 010 1 1 1 0 1 1 1 0

7.7 Checkers / Decoders • An OR gate only outputs ‘0’ for 1 combination – That combination can be changed by adding inverters to the inputs – We can think of the OR gate as “checking” or “decoding” a specific combination and outputting a ‘0’ when it matches. X Y Z F X Y Z F 0 0 0 1 0 0 0 1 0 0 1 1 0 0 1 1 0 1 0 0 x 0 1 0 1 x F y F y 0 1 1 1 0 1 1 1 z z 1 0 0 1 1 0 0 1 1 0 1 1 1 0 1 1 1 1 0 1 1 1 0 0 OR gate decoding OR gate decoding (checking for) 1 1 1 1 (checking for) 1 1 1 1 combination 010 combination 110

7.8 Circuit Design and Analysis • There are two basic tasks as a digital design engineer… – Circuit Design/Synthesis: Take a set of requirements or functional descriptions and arrive at a logic circuit – Circuit Analysis: Given a logic circuit, find or verify the logic function it implements Circuit Design Boolean Algebra Problem specification and Canonical Sums/Products Circuits and requirements Equations x A Karnaugh Maps y z Truth Tables x B F CAD tools y z x C y z Circuit Analysis

7.9 SYNTHESIZING LOGIC FUNCTIONS

7.10 The Problem • The goal of this unit is to teach you how you can take ANY logic function expressed as a truth table and design a digital circuit to implement that logic function How can I find a circuit that implements this truth table? I3 I2 I1 C1 C0 X Y Z P 0 0 0 0 0 0 0 0 0 ? ? (Addition) of Inputs Primes between 0-7 0 0 1 0 1 0 0 1 0 1’s Count 0 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 x z 1 0 0 0 1 1 0 0 0 P x 1 0 1 1 0 1 0 1 1 y 1 1 0 1 0 1 1 0 0 1 1 1 1 1 1 1 1 1 This Photo by Unknown Author is licensed under CC BY-SA-NC

7.11 Two Approaches: Minterms & Maxterms • Because of the binary nature of signals, there are at least two ways to implement any circuit • Using AND gate checkers (aka " minterms ") – Then combining their results with a single OR gate • Using OR gate checkers (aka " maxterms ") and AND'ing their results – Then combining their results with a single AND gate

7.12 Using AND Gates (Minterms) to Implement Functions • Given an any logic function, it can be implemented with the superposition of AND gate decoders/checkers X Y Z F 0 0 0 0 0 0 1 0 0 1 0 1 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1

7.13 Using AND Gates (Minterms) to Implement Functions • Generate an AND gate checker ("minterm") for each combination where the output of the logic function evaluates to 1 (i.e. F=1) X Y Z F X Y Z A x A y 0 0 0 0 0 0 0 0 z 0 0 1 0 0 0 1 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 0 1 1 1 1 1 1 1 0

7.14 Using AND Gates (Minterms) to Implement Functions • Generate an AND gate checker ("minterm") for each combination where the output of the logic function evaluates to 1 (i.e. F=1) X Y Z F X Y Z A B x A y 0 0 0 0 0 0 0 0 0 z 0 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 x B 0 1 1 0 y 0 1 1 0 0 z 1 0 0 1 1 0 0 0 1 1 0 1 0 1 0 1 0 0 1 1 0 0 1 1 0 0 0 1 1 1 1 1 1 1 0 0

7.15 Using AND Gates (Minterms) to Implement Functions • Generate an AND gate checker ("minterm") for each combination where the output of the logic function evaluates to 1 (i.e. F=1) X Y Z F X Y Z A B C x A y 0 0 0 0 0 0 0 0 0 0 z 0 0 1 0 0 0 1 0 0 0 0 1 0 1 0 1 0 1 0 0 x B 0 1 1 0 y 0 1 1 0 0 0 z 1 0 0 1 1 0 0 0 1 0 1 0 1 0 1 0 1 0 0 0 x C 1 1 0 0 1 1 0 0 0 0 y z 1 1 1 1 1 1 1 0 0 1

7.16 Using AND Gates (Minterms) to Implement Functions • Then, OR together all outputs of the AND gate checkers to form the overall function output X Y Z F X Y Z A B C F x A y 0 0 0 0 0 0 0 0 0 0 0 z 0 0 1 0 0 0 1 0 0 0 0 0 1 0 1 0 1 0 1 0 0 1 x F B 0 1 1 0 y 0 1 1 0 0 0 0 z 1 0 0 1 1 0 0 0 1 0 1 1 0 1 0 1 0 1 0 0 0 0 x C 1 1 0 0 1 1 0 0 0 0 0 y z 1 1 1 1 1 1 1 0 0 1 1

7.17 Using AND Gates (Minterms) to Implement Functions • Test it by plugging in combinations that should cause F=1 – As long as one AND gate outputs 1, the output will be 1 X Y Z F X Y Z A B C F x 1 A y 0 0 0 0 0 0 0 0 0 0 0 0 0 0 z 0 0 1 0 0 0 1 0 0 0 0 0 1 0 1 0 1 0 1 0 0 1 1 x F B 0 1 1 0 y 0 1 1 0 0 0 0 0 1 1 0 z 1 0 0 1 1 0 0 0 1 0 1 1 0 1 0 1 0 1 0 0 0 0 x 1 C 1 1 0 0 1 1 0 0 0 0 0 0 y 0 z 0 1 1 1 1 1 1 1 0 0 1 1 F(1,0,0) = 1

7.18 Using AND Gates (Minterms) to Implement Functions • Test it by plugging in combinations that should cause F=1 – As long as one AND gate outputs 1, the output will be 1 X Y Z F X Y Z A B C F x 0 A y 0 0 0 0 1 0 0 0 0 0 0 0 1 0 z 0 0 1 0 0 0 1 0 0 0 0 0 1 0 1 0 1 0 1 0 0 1 0 x F B 0 1 1 0 y 0 1 1 0 0 0 0 1 1 0 0 z 1 0 0 1 1 0 0 0 1 0 1 1 0 1 0 1 0 1 0 0 0 0 x 0 C 1 1 0 0 1 1 0 0 0 0 0 1 y 0 z 0 1 1 1 1 1 1 1 0 0 1 1 F(0,1,0) = 1

7.19 Using AND Gates (Minterms) to Implement Functions • Test it by plugging in combinations that should cause F=0 – All AND gates output 0, thus the OR gate will output 0 X Y Z F X Y Z A B C F x 0 A y 0 0 0 0 1 0 0 0 0 0 0 0 0 1 z 0 0 1 0 0 0 1 0 0 0 0 0 1 0 1 0 1 0 1 0 0 1 0 x F B 0 1 1 0 y 0 1 1 0 0 0 0 1 0 0 1 z 1 0 0 1 1 0 0 0 1 0 1 1 0 1 0 1 0 1 0 0 0 0 x 0 C 1 1 0 0 1 1 0 0 0 0 0 1 y 0 z 1 1 1 1 1 1 1 1 0 0 1 1 F(0,1,1) = 0

7.20 Minterms • An n-input combinational function can be described with 2 n row truth table • Each row in the truth table (input combination) has a unique logic expression that only evaluates to '1' for that combination – This logic expression is known as a minterm n Circuit inputs ഥ 𝒚 ∙ 𝒛 ∙ ത 𝒜 2 n row truth table 𝒚 ∙ 𝒛 ∙ 𝒜

7.21 Defining Minterms • An AND gate checking for one input combination of a function (i.e. one row of the truth table) is called a minterm – If the function has 3 variables, f(x,y,z), then each AND gate requires 3 inputs • Write the expression for each minterm of 3 variables: x,y,z Minterms Row # Abbrev Minterm Expression x y z m 0 m 1 m 2 m 3 m 4 m 5 m 6 m 7 0 m 0 0 0 0 1 0 0 0 0 0 0 0 1 m 1 0 0 1 0 1 0 0 0 0 0 0 2 m 2 0 1 0 0 0 1 0 0 0 0 0 3 m 3 0 1 1 0 0 0 1 0 0 0 0 4 m 4 1 0 0 0 0 0 0 1 0 0 0 5 m 5 1 0 1 0 0 0 0 0 1 0 0 6 m 6 1 1 0 0 0 0 0 0 0 1 0 7 m 7 1 1 1 0 0 0 0 0 0 0 1

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.