Design Methodologies Power Consumption Power Consumption Area - PowerPoint PPT Presentation

Digital IC Design Digital IC Design Design Trade-offs Speed (throughput and clock frequency) Design Methodologies Power Consumption Power Consumption Area Viktor wall Viktor wall and Dept. of Electrical and Infomation

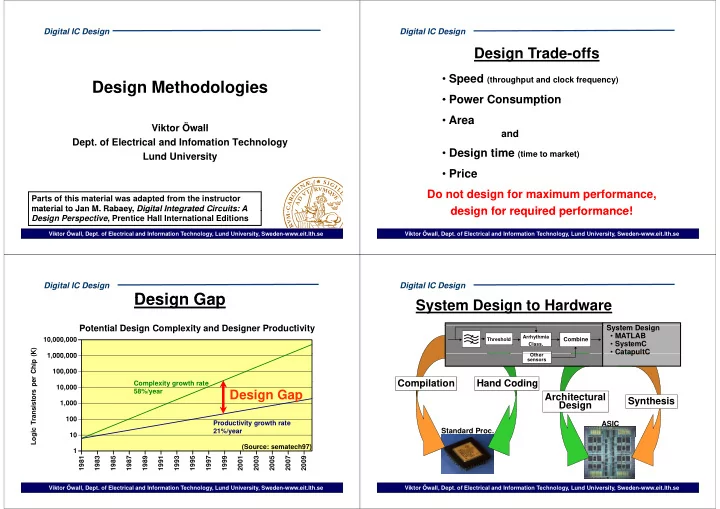

Digital IC Design Digital IC Design Design Trade-offs • Speed (throughput and clock frequency) Design Methodologies • Power Consumption • Power Consumption • Area Viktor Öwall Viktor Öwall and Dept. of Electrical and Infomation Technology • Design time (time to market) Design time (time to market) Lund University Lund University • Price Do not design for maximum performance, Parts of this material was adapted from the instructor material to Jan M. Rabaey, Digital Integrated Circuits: A material to Jan M. Rabaey, Digital Integrated Circuits: A design for required performance! design for required performance! Design Perspective , Prentice Hall International Editions Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Digital IC Design Digital IC Design Design Gap Design Gap System Design to Hardware P t Potential Design Complexity and Designer Productivity ti l D i C l it d D i P d ti it System Design S t D i • MATLAB Arrhythmia 10,000,000 Combine Threshold • SystemC Class. K) • CatapultC CatapultC er Chip (K 1,000,000 1 000 000 Other Oth sensors 100,000 Compilation Compilation Hand Coding Hand Coding sistors pe Complexity growth rate C l it th t 10,000 58%/year Design Gap Architectural Synthesis 1,000 Design g ogic Trans 100 Productivity growth rate ASIC Standard Proc. 21%/year 10 0 Lo (Source: sematech97) 1 981 983 985 987 989 991 993 995 997 999 001 003 005 007 009 19 19 19 19 19 19 19 19 19 19 20 20 20 20 20 Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se

Digital IC Design Digital IC Design System Design to Hardware S System Design t D i • MATLAB Arrhythmia Combine Threshold • SystemC Class. • CatapultC CatapultC Oth Other sensors “Early” Design GAP! Design Design Methodology ASIC ? Standard Proc. Evolution Next, i.e. now: Design Reuse, IP Reuse, Platform based design etc Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Digital IC Design Digital IC Design Design Analysis, Specification and V Verification ifi ti • Accounts for Largest fraction of Design time Accounts for Largest fraction of Design time (or at least should) Design g Methodology • More effective on higher levels of abstraction Three abstractions: Three abstractions: • Most design failures due to error in spec. Behavioral, structural and geometrical and geometrical Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se

Digital IC Design Digital IC Design Design Methodology, contnd. Moving betwen the domains “Standard” Amount of Automatization Amount of Automatization Design Flow of increase T d Today Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Digital IC Design Digital IC Design Standard Processors vs. Special Purpose Software or Hardware? • Flexibility Algorithm • Performance Requirements • Performance Requirements – Power Consumption – Throughput Th h t Special Standard • Cost Processor Purpose Processor Cores Domain Specific D i S ifi – Volume • Flexible Architecture Processors • Programmable – Know how • High Calculation Capacity etc. • Low Design cost Low Design cost • Low Power L P – Time to Market • Standard Interface • User defined Interface • Good supply of tools • Variable Wordlength • Low Price at Volume Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se

Digital IC Design Digital IC Design E Energy Efficiency Effi i Energy/Area efficiency E /A ffi i Energy efficiency Energy Efficiency (MOPS/mW) Area Efficiency (MOPS/mm2) (MIPS/mW) (MIPS/mW) 10000 10000 ? 100 1000 ies ea Efficienci 10 100 4 orders of 4 orders of rgy and Are 10 10 1 magnitude 1 0.1 0 1 Microprocessors p D di Dedicated t d Ene General Designs 0.1 Purpose 0.01 DSP’s 0.01 Pentium StrongARM TI-DSP Dedicated 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 High Low Chip Number (see Table II) Flexibility Flexibility Courtesy: Professor Bob Brodersen, UC Berkeley Acknowledgement: Bob Brodersen Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Digital IC Design Digital IC Design Results in fully parallel solutions Results in fully parallel solutions Reducing supply voltage saves energy: E = CV 2 Energy Area 64-point FFT 16-State Viterbi 64-point FFT 16-State Viterbi Decoder Decoder Decoder Decoder E Energy per Transforms per second T f d To reach efficient solutions Transform (nJ) Energy per per unit area Decode rate per unit Decoded bit (nJ) (Trans/ms/mm 2 ) area (kb/s/mm 2 ) algorithm/hardware codesign Direct-Mapped Hardware 1.78 0.022 2,200 200,000 FPGA 683 5.5 1.8 100 Low-Power DSP 436 19.6 4.3 50 is crucial! High-Performance DSP 1700 108 10 150 (numbers taken from vendor-published benchmarks) 1000 Orders of magnitude lower efficiency 5000 even for an optimized processor architecture even for an optimized processor architecture Courtesy Ning Zhang, Berkeley Wireless Research Center (BWRC) Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se

Digital IC Design Digital IC Design Scope How to get from a signal processing algorithm to an EFFICIENT This is an Advertisement implementation using – Different numbering systems DSP Design – Pipelining – Parallelism P ll li – Strength reduction, i.e. complexity of operations. 6 credits 6 credits – etc, etc,... in a structured way! P Period 2, Fall i d 2 F ll Case studies: FFT, image filtering, acoustic echo cancellation, p pacemakers,... , Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Digital IC Design Digital IC Design From Algorithm to Implementation g p From Algorithm to Implementation g p Many paths! How do we get there? Many paths! How do we get there? FIR-filter FIR-filter Time-multiplexed Time-multiplexed x(n) ( ) x(n) ( ) architecture architecture D D D D D D MUX MUX c c h0 h1 h2 h3 h0 h1 h2 h3 y(n) y(n) in Signal Processing book in Signal Processing book processor REG REG x(2k+1) x(2k) x(2k+1) x(2k) D D x(2k-1) D D x(2k-1) x(2k-2) x(2k-2) D D b 0 b 0 b 1 b 2 b 1 b 2 y(2k) y(2k) y(2k) y(2k) ”ASIC” b 0 b 1 b 2 b 0 b 1 b 2 y(2k+1) y(2k+1) Parallel architecture Parallel architecture FPGA Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se

Digital IC Design Digital IC Design Architectural Design Architectural Design Problems in DSP Design (contd) Allocation - determine architectural resources Supplying the MIPS is not the biggest Assignment binding operations to hardware Assignment - binding operations to hardware problem but how to get problem but how to get the correct data, Scheduling - determine execution order to the correct processing element to the correct processing element, plus transformations at the right time pipelining, software pipelining, loop unrolling, etc... at and parallelism, hierarchy, etc... Low Power Low Power Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Digital IC Design Digital IC Design Implementation Techniques Implementation Techniques Virtex Virtex Block RAM BANK 0 BANK 1 Special Special Purpose NK 7 NK 2 IOB IOB BAN BAN CLB CLB FPGA FPGA ASIC ASIC Gate Array y BANK 6 BANK 3 Field Programmable Application/Algorithm Gate Arrays Specific Integrated Circuit Routing Routing • Reconfigurable R fi bl • High Calculation Capacity • Fast Turn Around • High Utilization • Prototyping • Low Power Timing g BANK 5 BANK 4 • Low Price at Volume Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.