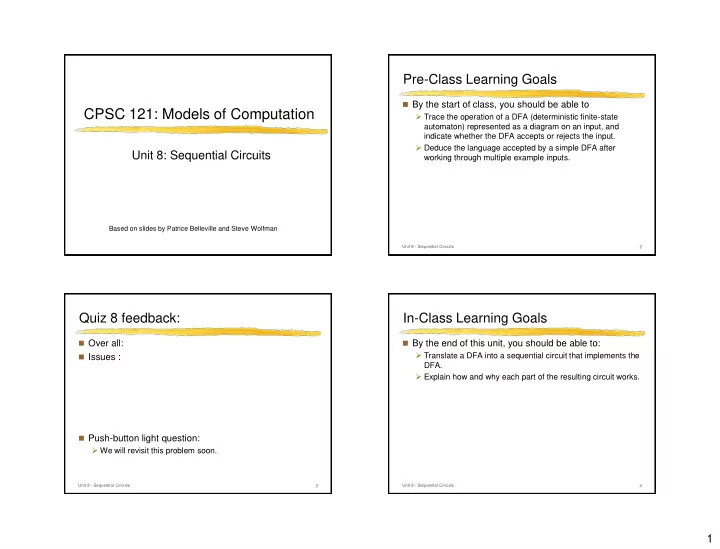

CPSC 121: Models of Computation Trace the operation of a DFA - PowerPoint PPT Presentation

Pre-Class Learning Goals By the start of class, you should be able to CPSC 121: Models of Computation Trace the operation of a DFA (deterministic finite-state automaton) represented as a diagram on an input, and indicate whether the DFA

Pre-Class Learning Goals By the start of class, you should be able to CPSC 121: Models of Computation Trace the operation of a DFA (deterministic finite-state automaton) represented as a diagram on an input, and indicate whether the DFA accepts or rejects the input. Deduce the language accepted by a simple DFA after Unit 8: Sequential Circuits working through multiple example inputs. Based on slides by Patrice Belleville and Steve Wolfman Unit 8 - Sequential Circuits 2 Quiz 8 feedback: In-Class Learning Goals Over all: By the end of this unit, you should be able to: Translate a DFA into a sequential circuit that implements the Issues : DFA. Explain how and why each part of the resulting circuit works. Push-button light question: We will revisit this problem soon. Unit 8 - Sequential Circuits Unit 8 - Sequential Circuits 3 4 1

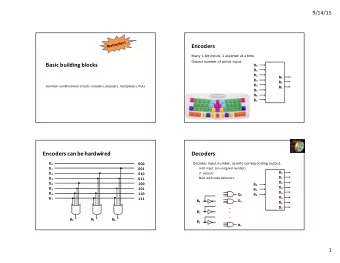

? ? Related to CPSC 121 Bib Questions Unit Outline How can we build a computer that is able to Sequential Circuits :Latches, and flip-flops. execute a user-defined program? Computers execute instructions one at a time. DFA Example They need to remember values, unlike the circuits you designed in labs 1, 2, 3 and 4. Implementing DFAs How Powerful are DFAs? NOW: We are learning to build a new kind of circuits with memory that will be the key new Other problems and exercises. feature we need to build full-blown computers! Unit 8 - Sequential Circuits 5 Unit 8 - Sequential Circuits 6 Problem: Light Switch DFA for Push-Button Switch ? Problem: Design a circuit to control a light so that the light changes state any time its “push - button” switch is pressed. pressed light light off on ? pressed This Deterministic Finite Automaton (DFA) isn’t really about accepting/rejecting; its current state is the state of the light. Unit 8 - Sequential Circuits 7 8 2

Problem : Light Switch Departures from Combinational Circuits ? MEMORY: Problem : Design a circuit to control a light so that the light We need to “remember” changes state any time its “push - button” switch is pressed. the light’s state. Identifying inputs/outputs: consider Which are most useful for these possible inputs and outputs: EVENTS: this problem? We need to act on Input 1 : the button was pressed a. Input 1 and Output 1 a button push rather Input 2 : the button is down b. Input 1 and Output 2 than in response Output 1 : the light is on c. Input 2 and Output 1 Output 2 : the light changed states to an input value. d. Input 2 and Output 2 e. None of these 9 10 “Mux Memory” How Do We Remember? We want a circuit that: How do we use a mux to store a bit of memory? Sometimes… remembers its current state. We choose to remember on a control value of 0 and to Other times… loads a new state and remembers it. load a new state on a 1. Sounds like a choice . What circuit element do we have for modelling ??? 0 choices? output 1 new data control We use “0” and “1” because that’s how MUXes are usually labelled. 11 12 3

“ Mux Memory” Truth Table for “Muxy Memory” How do we use a mux to store a bit of memory? Fill in the MM’s truth table: We choose to remember on a control value of 0 and to a. b. c. d. e. load a new state on a 1. None G D Q' Q Q Q Q of 0 0 0 0 0 0 0 these 0 0 1 1 1 1 0 old output (Q’) 0 0 1 0 0 0 0 0 output (Q) 0 1 1 1 1 1 1 new data 1 (D) 1 0 0 0 0 0 1 1 0 1 1 0 X 1 control (G) 1 1 0 0 1 X 0 This violates our basic combinational constraint: no cycles. 1 1 1 1 1 1 1 13 14 Truth Table for “ Muxy Memory” Truth Table for “ Muxy Memory” Worked Problem: Write a truth table for the MM: Worked Problem: Write a truth table for the MM: G D Q' Q G D Q' Q 0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 1 0 1 0 0 0 1 0 0 0 1 1 1 0 1 1 1 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 1 1 1 0 1 1 1 1 1 1 1 1 1 Like a “normal” mux table, but what happens when Q' Q? Q' “takes on” Q’s value at the “next step”. 15 16 4

D Latches D Latch We call a "mux-memory" a D-latch ( recall from lab #5) When G is 0, the latch maintains its memory. When G is 0, the latch retains its current value. When G is 1, the latch loads a new value from D. When G is 1, the latch loads a new value from D. old output (Q’) new data (D) D 0 output (Q) output (Q) Q new data (D) 1 control (G) G control (G) Unit 8 - Sequential Circuits 17 18 Using the D Latch D-Latch for Circuits with Memory A D-latch looks like new data (D) D Problem : What goes in the cloud? What do we send Q output (Q) into G? G control (G) Why does the D Latch have two inputs and one output when the mux inside has THREE inputs and one D output? Q Combinational A. The D Latch is broken as is; it should have three inputs. ?? G Circuit to calculate next state B. A circuit can always ignore one of its inputs. input C. One of the inputs is always true. D. One of the inputs is always false. We assume we just want Q as the output. E. None of these (but the D Latch is not broken as is). 19 20 5

Using the D Latch Push-Button Switch for Our Light Switch What signal does the button generate? Problem : What do we send into G? D current light state Q ?? G output high a. T if the button is down, F if it’s up. b. T if the button is up, F if it’s down. low c. Neither of these. Unit 8 - Sequential Circuits 21 22 Using the D Latch Using the D Latch for Our Light Switch for Our Light Switch Problem : What should be the next state of the light? Problem : Will this work? D D current light state current light state Q “pulse” when Q “pulse” when button is button is ?? G ?? G pressed pressed output output button button pressed pressed 23 24 6

A Timing Problem Push-Button Switch This toll booth has a similar problem. What is wrong with our solution? What is wrong with this booth? A. We should have used XOR instead of NOT. B. As long as the button is down, D flows to Q, and it flows through the NOT gate and back to D...which is bad! C. The delay introduced by the NOT gate is too long. D. As long as the button is down, Q flows to D, and it flows back to Q... and Q (the output) does not change! P.S. Call this a “bar”, not a “gate”, or E. There is some other problem with the circuit. we'll tie ourselves in (k)nots. From MIT 6.004, Fall 2002 Unit 8 - Sequential Circuits 25 Unit 8 - Sequential Circuits 26 A Timing Solution A Timing Problem Problem : What do we send into G? Is this OK? D current light state “pulse” when Q button is G pressed output button As long as the button is down, D flows to Q flows pressed through the NOT gate and back to D... From MIT 6.004, Fall 2002 which is bad! Unit 8 - Sequential Circuits 28 27 7

A Timing Solution (Almost) A Timing Solution D D D D Q Q Q Q G G G G Never raise both “bars” at ?? output output the same time. The two latches are never enabled at the same time (except for the moment needed for the NOT gate on the left to compute, which is so short that no “cars” get through). button pressed 29 30 A Timing Solution Button/Clock is LO (unpressed) 1 1 D D D D Q Q 0 Q Q 1 G G G G button output press output LO 0 signal We’re assuming the circuit has been set up and is “running normally”. Right now, the light is off (i.e., the output of the right latch is 0). button pressed 31 32 8

Propagating signal.. Button goes HI (is pressed) left NOT, right latch 1 1 1 1 D D D D 0 Q Q 1 Q Q 0 1 G G G G output output HI 1 HI 1 This stuff is processing a new signal. This stuff is processing a new signal. 33 34 Propagating signal.. right NOT (steady state) Button goes LO (released) 0 0 1 1 D D D D 1 Q Q 1 Q Q 0 0 G G G G output output LO 0 HI 1 Why doesn’t the left latch update? a. Its D input is 0. b. Its G input is 0. c. Its Q output is 1. This stuff is processing a new signal. d. It should update! 35 36 9

Propagating signal.. Propagating signal.. left NOT left latch (steady state) 0 0 1 D D 0 D D Q Q 1 1 Q Q 1 G G 1 G G output LO 0 output LO 0 This stuff is processing a new signal. And, we’re done with one cycle. How does this compare to our initial state? 37 38 Master/Slave D Flip-Flop Master/Slave D Flip-Flop Symbol + Semantics Symbol + Semantics When CLK goes from 0 (low) to 1 (high), the flip-flop loads a When CLK goes from 0 (low) to 1 (high), the flip-flop loads a new value from D. new value from D. Otherwise, it maintains its current value. Otherwise, it maintains its current value. new new data D D data D D (D) (D) output output Q Q Q Q (Q) (Q) G G G G control control or or “clock” “clock” signal signal (CLK) (CLK) 39 40 10

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.