Ch. 1 Interlude Review of Architecture, Threading, and the C - PowerPoint PPT Presentation

1 CSCI 350 Ch. 1 Interlude Review of Architecture, Threading, and the C Language Mark Redekopp Michael Shindler 2 Recall An OS is a piece of software that manages a computers resources User App User App User mode Resources

1 CSCI 350 Ch. 1 Interlude – Review of Architecture, Threading, and the C Language Mark Redekopp Michael Shindler

2 Recall • An OS is a piece of software that manages a computer’s resources User App User App User mode • Resources needing management: System System Library Library – CPU (threads and processes) – Memory (Virtual memory, Processes & File Scheduling Systems protection) Kernel Mode – I/O (Abstraction, interrupts, I/O Drivers Memory & Protocols Translation protection) • Let's look a bit deeper at some of Processor Network Hardware the hardware DISK Mem. Graphics Management Unit

3 PC Architecture (~10 years ago) • Place component with the Processor highest data needs closest to Cache the processor • Memory controller System Bus – DRAM requires dedicated Mem. controller to interpret system bus DRAM Graphics transactions to memory control Ctrl. signals – High bandwidth connection via I/O Bus system bus Hard Disk, PCI-Express • ICH (I/O Controller Hub) ICH CD-ROM Expansion Drives Bus – Implements USB controller, Hard Drive, CD-ROM and PCI expansion interfaces along with other I/O USB ports interfaces – Provides lower bandwidth capabilities over I/O bus

4 Modern PC Architecture Processor • Moore's Law has allowed greater integration levels Core Core Core Core Display – Multiple cores and greater Graphics Cache levels of cache PCI Ctrl. Mem Ctrl. DRAM – Memory controller, graphics, and high-speed I/O are System integrated onto the Bus processor die Ethernet ICH SATA Ports Audio More PCI USB ports

5 CS 201/356 REVIEW

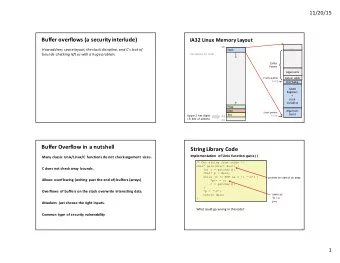

6 Assembly • High-level code is broken into basic instructions • Programmer's model of a machine (CPU and memory) is everything the programmer needs to know to write and translate software code to 1's and 0's – Registers – Program Counter (Instruction Pointer) – Status/mode flags – Data sizes – I/O addressing (memory-mapped I/O) – Various cache/TLB instructions/settings

7 Intel (IA-32) Architectures Data/Offset Registers Pointer/Index Registers Segment Registers 31 16 8 0 AX EIP CS + EAX AH AL (Instruction Pointer) (Code Segment) ESP EBX BH BL (Stack Pointer) SS + (Stack Segment) EBP ECX CH CL (Base “Frame” Ptr.) ESI DS EDX DH DL + (Source Index) (Data Segment) EDI ES + (Dest. Index) (Extended Segment) Status Register EFLAGS

8 Real Mode Addressing • How to make 20-bit addr. w/ 16-bit reg’s ??? – Use two 16-bit registers – (Segment register * 16) + Index Reg. • Format: – Seg Reg:Index Reg (e.g. CS:IP) 16-bit Segment Reg. 0 0 0 0 + 16-bit Index Reg. 20-bit Memory Address Examples: 0x1A5C0 0x74AB0 0x1A5C:0x405E 0x74AB:0xE892 + 0x405E + 0xE892 0x1E61E 0x83345

9 Protected Mode Addressing • Segment Register value selects a segment (area of memory) Memory Data • EA (Effective Address) = Index reg. + Segment segment start addr. Stack Segment Segment Reg. Segment Start Addr. Memory Management Unit Text + Segment EA Index Reg.

10 IA-32 Addressing Modes Name Example Effective Address Immediate MOV EAX,5 R[d] = immed. Direct MOV EAX,[100] R[d] = M[100] Register MOV EAX,EDX R[d] = R[s] Register indirect MOV EAX,[EBX] R[d] = M[R[s]] MOV EAX,[EBP+60] Base w/ Disp. R[d] = M[R[s]+d] MOV EAX,[EBP + ESI*4] R[d] = Base w/ Index M[(Reg1)+(Reg2)*S] MOV EAX,[EBP+ESI*4+100] R[d] = Base w/ Index & M[(Reg1)+(Reg2)*S + d] Disp.

11 IA-32 Instructions • Stack aware instructions – ‘call’ / ‘ret’ automatically push/pop return address onto stack – ‘push’ / ‘pop’ instructions for performing these operations • Memory / Register architecture – One operand can be located in memory • add eax, [ebp] # adds reg. EAX to value pointed at by EBP • Specialized Instructions – xchg src1, src2 # exchanges/swaps operands – string copy and compare instructions

12 STACK FRAMES & FUNCTION CALLS

13 Stack Frame Organization ... Main's Data Main’s Stack • Arg. n Args. for SUB1 (or any other routine called by Frame main) ... Arg. 1 • Return Address Return address pushed by 'call' instruc. Saved regs. • ABI requires specific registers be saved (those $ebx, $ebp, shown to the left). Others are allowed to be $esi, $edi) overwritten (i.e. caller needed to save them if he/she wanted them) Padding/Empty • Empty slot if needed because local data space must be double-word aligned (multiple of 8) SUB1’s Stack Local variables • Frame Space for any local/automatic declared variables in a routine • Space for any “non - preserved” registers that need Other saved regs to be saved when SUB1 calls another routine Padding/Empty Arg. n • Args. for any other routine called by SUB1 Stack Growth ... Arg. 1

14 Building a Stack Frame • Caller routine… – Save/push caller’s "unpreserved" registers (use 'push' instruction) – Push arguments onto stack – Execute 'call' (Saves return address onto stack [i.e. CS:IP]) • Callee routine… – Save/push "preserved" registers ($ebx, $ebp, $edi, $esi) – Allocate space for local variables by moving $esp down – Save/push "non-preserved registers" (e.g. $ecx, if needed) – Execute Code – Place return value in $eax – Restore/pop "non-preserved registers" – Deallocate local variables by moving $esp up – Restore/pop "preserved registers" – Return using 'ret' (Pops the return address off the stack) • Caller routine… – Pop arguments – Restore/pop "non-preserved registers"

15 Accessing Values on the Stack • Stack pointer ($esp) is usually used to Saved Regs. access only the top value on the stack • To access arguments and local variables, Local Vars. we need to access values buried in the (ans) stack Args. • We can use an offset from $esp Saved Regs. • However if $esp moves (due to additional Local Vars. push/pops) then we have to use a (ans) different offset to get the same data from + offset the stack Args. $esp – This can make readying the code harder • Possible improvement: Use a pointer that To access parameters we could try to use won't change during function execution some displacement (aka the base/frame pointer, $ebp) [i.e. ($esp,8) ]

16 Base/Frame Pointer • Use a new pointer called Saved Regs. Base/Frame Pointer ($ebp) to point to the base of the current routines Local Vars. frame (i.e. the first word of the stack (ans) frame) + offset Args. • $ebp will not change during the $fp Saved Regs. course of subroutine execution - offset • Can use constant offsets from $ebp Local Vars. (ans) to access parameters or local variables Args. – Key 1: $ebp doesn’t change during $sp subroutine execution – Key 2: Number of arguments, local variables, and saved registers is a known value

17 THREAD BASICS

18 What is a Thread? • Registers + PC + Stack representing a single execution 0xffffffff Memory sequence • Independently scheduled unit of code Kernel 0x80000000 0x7ffffc80 T1 Stack 0x7ffff400 eax T2 Stack esp 0xbff70c44 eip 0x800011c8 Code 0x080a4 dec ECX eflags jnz done --- --- done: CPU ret 0x0

19 Atomic Operations Code Thread 1: Thread 2: • Operation appears to be x++; x++; indivisible load x load x • Given int x=0; and multiple add 1,x add 1,x store x store x threads Ordering Ordering • Is x++; atomic? Option 1 Option 2 • No…it translates to: Thread 1: Thread 2: Thread 1: Thread 2: load x load x – load/move load x add 1,x add 1,x store x – add store x load x – store/move add 1,x add 1,x store x store x Result 1 Result 2

20 Synchronization Primitives • What are the key operations for these primitives? • Locks • Condition Variables • Semaphores

21 Caching & Virtual Memory • What do you remember about caching and virtual memory?

22 Memory Hierarchy & Caching • Lower levels act as a cache for upper levels Registers L1 Cache ~ 1ns L1/L2 is a “cache” for L2 Cache main memory ~ 10ns Main Memory Virtual memory ~ 100 ns provides each Disk / Secondary Storage process its own ~1-10 ms address space in secondary storage and uses main memory as a cache

23 Cache Example Proc. Access data i • When processor attempts to Cache does Cache access data it will first check not have desired the cache data Spend full – If the cache does not have the time to get Mem. data, it must go to the main from RAM Ctrl. memory memory (RAM) to access it – If the cache has the desired Proc. data, it can supply it quickly Susequent Access to Cache data i Get data quickly from cache Mem. RAM Ctrl.

24 Address Spaces • Physical address spaces Program/Process corresponds to the actual system 1,2,3,… address bus width and range (i.e. 0xffff ffff 0xffff ffff main memory and I/O) Not Mem used • Each process/program runs in its 0xbfffffff own private “virtual” address I/O I/O 0x80000000 space – Virtual address space can be larger Not used (or smaller) than physical memory 0x3fffffff Mem. – Virtual address spaces are protected Mem. from each other 0x00000000 0x00000000 • Process (def.): Address Space + 32-bit Physical 32-bit Fictitious Virtual Threads Address Space w/ Address Spaces only 1 GB of Mem ( > 1GB Mem)

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Course Overview, Python Basics [Andersen, Gries, Lee, Marschner, Van Loan, White] Interlude: Why](https://c.sambuz.com/408788/course-overview-python-basics-s.webp)