Body Effect (Back Bias) Body Effect (Back Bias) Drain 2 qN 2 - PowerPoint PPT Presentation

Remember the Standard V t Equation? Short Channel MOS Transistor 2 qN 2 = + + a si B 2 V V t fb B C ox Y. Taur, T. Ning, Fundamentals of Modern VLSI Devices, Professor Chris H. Kim Cambridge University Press,

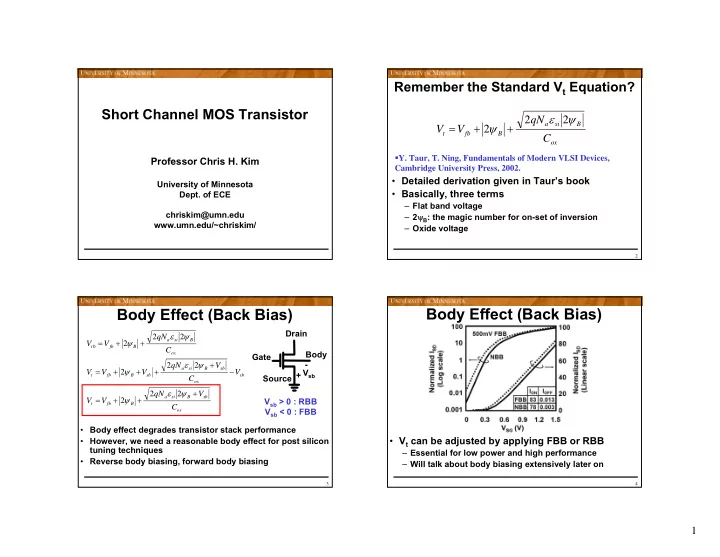

Remember the Standard V t Equation? Short Channel MOS Transistor ε ψ 2 qN 2 = + ψ + a si B 2 V V t fb B C ox � Y. Taur, T. Ning, Fundamentals of Modern VLSI Devices, Professor Chris H. Kim Cambridge University Press, 2002. • Detailed derivation given in Taur’s book University of Minnesota • Basically, three terms Dept. of ECE – Flat band voltage chriskim@umn.edu – 2 ψ B : the magic number for on-set of inversion www.umn.edu/~chriskim/ – Oxide voltage 2 Body Effect (Back Bias) Body Effect (Back Bias) Drain ε ψ 2 qN 2 = + ψ + a si B V V 2 t 0 fb B C Body ox Gate ε ψ + - 2 qN 2 V = + ψ + + − a si B sb V sb V V 2 V V + t fb B sb sb Source C ox ε ψ + 2 qN 2 V = + ψ + a si B sb V V 2 V sb > 0 : RBB t fb B C V sb < 0 : FBB ox • Body effect degrades transistor stack performance • V t can be adjusted by applying FBB or RBB • However, we need a reasonable body effect for post silicon tuning techniques – Essential for low power and high performance • Reverse body biasing, forward body biasing – Will talk about body biasing extensively later on 3 4 1

Body Biasing for Process Compensation Short Channel Effect: V t roll-off 100% Accepted 110C Die count 80% Long Channel Short Channel dies: 1.1V 60% NBB 40% n+ poly gate n+ poly gate 20% ABB 0% 6 0% n+ source n+ drain n+ source n+ drain Normalized leakage 5 ABB depletion Charge sharing Charge sharing 4 p-type body p-type body 3 Body bias: 2 controllability Ec Ec NBB 1 to V t • Ability of gate & body to control channel charge diminishes 0 as L decreases, resulting in Vt-roll-off and body effect 0.925 1 1.075 1.15 1.225 reduction Normalized frequency 5 6 Short Channel Effect: Drain Induced Short Channel Effect: V t roll-off Barrier Lowering (DIBL) Long Channel Short Channel n+ poly gate n+ poly gate V t n+ source n+ source n+ drain n+ drain depletion 3 σ L variation p-type body p-type body Ec Ec L eff Vds ↑ Vds ↑ • 3 σ V t variation increases in short channel devices • Increase in V DS reduces V t and increases V t -roll-off: DIBL 8 2

Short Channel Effect: DIBL Short Channel Effect: Drain Induced Barrier Lowering (DIBL) V ds =2.0V V ds =0.1V V t roll-off (V ds ~0V) log(I ds ) log(I ds ) V t DIBL+V t roll-off (V ds =V dd ) V gs (NMOS) V gs (PMOS) Δ V λ = t • DIBL coefficient d Δ V ds L eff • DIBL increases leakage current • Dynamic V dd can reduce leakage because of DIBL 9 10 Short Channel V t Equation Transistor Scaling Challenges - X j 0.8 0.5 0.2 130 λ = + ψ + ε ψ + − λ LMET b V V 2 2 qN ( 2 V ) V IDN (mA/ μ m) t fb B a s B sb d ds 0.7 0.4 NMOS 0.15 120 C IDP (mA/ μ m) R EXT ( Ω μ m) LMET ( μ m) ox 0.6 0.3 REXT 0.1 110 ε ψ 2 qN 2 = + ψ + a si B (Long channel V t equation) PMOS V V 2 0.5 0.2 t fb B 0.05 100 C ox S. Thompson et al., 1998. S. Thompson et al., 1998. 0.4 0.1 [Poon, IEDM, 1973] 0 90 0 50 100 150 200 0 50 100 150 200 ⎛ ⎞ Junction Depth (nm) X 2 W ⎜ ⎟ Junction Depth (nm) λ = − + − j 1 1 1 ⎜ ⎟ b X L ⎝ ⎠ j Salicide S. Asai et al., 1997. Salicide [Ng, TED, 1993] Poly-Si − ⎡ ⎤ 2 . 7 L λ = ⎢ ⎥ R C μ − + μ + μ + μ d 2 ⎢ ⎥ ⎣ 2 . 2 m ( T 0 . 012 m )( W 0 . 15 m )( X 2 . 9 m ) ⎦ ox sd j R SE Rsalicide 11 12 3

Effect of Series Resistance Leakage Components (10nm Device) Weak Inversion Current, Gate Oxide Tunneling Drain Induced Barrier Lowering Gate and Narrow Width Effect Source Drain n+ n+ Punchthrough Reverse Bias Diode & BTBT Gate Induced Drain p-sub Leakage (GIDL) Bulk [Keshavarzi, Roy, and Hawkins, ITC 1997] 13 14 Sub-Threshold Current Sub-Threshold Current ( ) 2 ⎛ ⎞ − − q V V W k T ( ) qV gs t ds = μ ⎜ ⎟ − − B I C m 1 e mkT ( 1 e kT ) ⎜ ⎟ d eff ox ⎝ ⎠ L q • NPN BJT is formed in sub-threshold region • Only difference with a real BJT is that the base voltage is controlled through a capacitive divider, and not directly by a electrode • Like in a BJT, current is exponential to V be 15 16 4

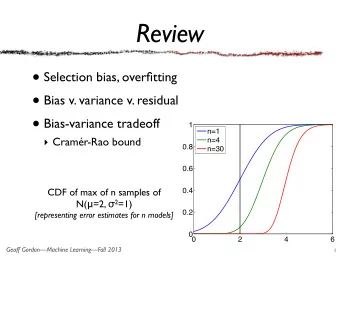

V dd and V t Scaling Sub-Threshold Swing Performance vs Leakage: C kT = mV = + dep S m ln 10 ( ) , m 1 log(I DS ) V T ↓ I OFF ↑ I D (SAT) ↑ dec q C ox − W V T ∝ • Smaller S-swing is better eff mkT / q I K e OFF 1 L • Ideal case: m=1 (C ox >>C sub ) eff I OFFL – Fundamental limit = 1 * 26mV * ln10 W ∝ eff − 2 I ( SAT ) K ( V V ) D 2 GS T I OFFH = 60 mV/dec @ RT L eff – Can only be achieve by device geometry (FD-SOI) V TL V TH ∝ υ − I ( SAT ) K W C ( V V ) V GS • Typical case: m ≈ 1.3 D 3 eff ox SAT GS T – S = 1.3 * 26mV * ln10 ≈ 80 mV/dec @ RT � As V t decreases, sub-threshold leakage increases – At worst case temperature (T=110C), S ≈ 100 mV/dec � Leakage is a barrier to voltage scaling 17 18 V dd and V t Scaling Gate Oxide Tunneling Leakage • V t cannot be scaled indefinitely due to increasing leakage power (constant sub-threshold swing) 3 10 3 2.5nm 2 I GATE • Example 3.5nm 5.1nm 7.6nm CMOS device with S=100mV/dec has I ds =10 μ A/ μ m 0 10 0 I GATE (A/cm 2 ) @ V t =500mV 2 3.0nm I OFF I off =10 μ A/ μ m x 10 -5 = 0.1 nA/ μ m 3 4 5 C. Hu, 1996. Now, consider we scale the V t to 100mV 6 e - 10 -7 7 I off =10 μ A/ μ m x 10 -1 = 1 μ A/ μ m 0 2 4 6 8 10 12 Gate Voltage (V) N + Gate P - Substrate Suppose we have 1B transistors of width 1 μ m I sub =1 μ A/ μ m x 1B x 1 μ m = 100 A !! 19 20 5

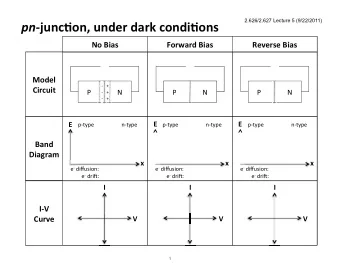

Gate Oxide Tunneling Leakage Band-to-Band Tunneling Leakage E C • Quantum mechanics tells us that there is a finite probability for electrons to tunnel through oxide q(V bi +V app ) • Probability of tunneling is higher for very thin E V oxides E C • NMOS gate leakage is much larger than PMOS p(+)-side • Gate leakage has the potential to become one of E V the main showstoppers in device scaling n(+)-side S/D junction BTBT Leakage − − B V V = = 2 E dd t • Reversed biased diode band-to-band tunneling I AE e , E ox gate ox ox t – High junction doping: “Halo” profiles ox – Large electric field and small depletion width at the junctions 21 22 Narrow Width Effect Gate Induced Drain Leakage (GIDL) • Appears in high E-field region under gate/drain Gate overlap causing deep depletion V t • Occurs at low V g and high V d bias width • Generates carriers into substrate from surface traps, band-to-band tunneling W • Localized along channel width between gate and drain Extra depletion • Depletion region extends Channel region • Thinner oxide, higher V dd , lightly-doped drain outside of gate controlled enhance GIDL region Side view of MOS transistor • Opposite to V t roll-off • High field between gate and drain increases • Depends on isolation injection of carriers into substrate technology 23 24 6

Leakage Components [IEEE press, 2000] 25 7

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.