Barrel Calorimeter (EB + HB) Off-detector electronics Bob Hirosky - PowerPoint PPT Presentation

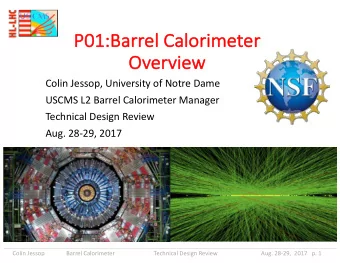

Barrel Calorimeter (EB + HB) Off-detector electronics Bob Hirosky HL-LHC Barrel Calorimeter L3 Manager Pre-FDR Review Fermilab, 13 th 14 th December 2018 Bob Hirosky, 13-14 Dec 2018 Pre-FDR || BCAL 1 Outline Motivation

Barrel Calorimeter (EB + HB) Off-detector electronics Bob Hirosky HL-LHC Barrel Calorimeter L3 Manager Pre-FDR Review Fermilab, 13 th – 14 th December 2018 Bob Hirosky, 13-14 Dec 2018 Pre-FDR || BCAL 1

Outline ● Motivation ● Overview of off detector / back end (BE) electronics ● Personnel ● Requirements ● Barrel calorimeter processor design ● Schedule ● Risks ● QA/QC ● Costs Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 2

Motivation: ECAL + HCAL barrel BE electronics Both ECAL and HCAL require updates to back end electronics to accommodate increased latency/buffer requirements for L1 trigger decisions at HL-LHC In addition ECAL will require significantly more data bandwidth than the present system to support required L1 trigger performance at high luminosity running: ● Reduce granularity / improve resolution of data for L1 trigger decision ● Enhanced suppression of spurious signals (increasing with luminosity) ● Better pulse reconstruction => energy resolution for trigger ● Flexibility in future algorithms to optimize future detector performance Full details given in L2 talk Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 3

EB HL-LHC upgrade – Barrel Calorimeter Processor (BCP) ● Concentrate detector raw data, build trigger primitives and transmit to L1 Trigger. ● Receive LHC clock and distribute with high precision to the on detector electronics. ● Buffer and send event data to the DAQ after L1 Accept signal received by the TCDS interface. ● Handle slow-control of the on-detector electronics via the lpGBT interfaces. Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 4

HB HL-LHC upgrade – BCP Back-End ● Concentrate detector EB and HB raw data, build trigger use common primitives and transmit ATCA to L1 Trigger. platform ● Receive LHC clock and distribute to on detector electronics. ● Buffer and send event data to the DAQ after L1 Accept signal received by the TCDS interface. ● Handle slow-control of the on-detector electronics Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 5

Engineering team Engineers: ● Tom Gorksi , Electronic Engineer, Wisconsin. 20 years experience. Designer of phase 1 Calo trigger board (CTP7) ● Stephen Goadhouse , Electronic engineer, Virginia. 18 years experience. Designer of HCAL phase 1 FE board (ngCCM) Nikitas Loukis , Electronic engineer, Notre Dame. CMS member for 6 years. Barrel Muon Trigger development ● Eric Frahm , Electronic engineer, Minnesota. 20 years of experience. Designer of HCAL phase 1 BE board (μHTR) ● Tulio Grassi , Electronic engineer, Maryland. 15 years of experience. Designer of HCAL phase 0 (and 1) board (HTR) Physicists: ● Faculty: Jessop (ND), Hirosky (UVa), Rusack (UMN), Belloni (UMD), Orimoto (NEU) ● Post-docs and students from each group ● Technicians from the groups as required Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 6

Engineering requirements Engineering requirements specify technical details needed to achieve physics performance requirements ... Barrel Calorimeter Requirements CMS-doc-13317 Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 7

BCP design specifications (Barrel ECAL+HCAL) Specifications driven by CMS Document 13317: ● Science-Engineering (physics mission) requirements ● Engineering (technical) requirements ● Interface control requirements Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 8

BCP baseline design ● ATCA form factor BE system 2.5k 2.5 Gbps FE control links 10k 10 Gbps data links ● 108 BCP modules for EB Trigger primitive generation and Level 1 trigger interface Common CMS interface ● TCDS, DAQ ● 18 BCP for HB Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 9

EB: Processing region per FPGA Barrel: |η| < 1.48 36 Supermodules, 61200 crystals ECAL Barrel Calo. (supermodule) Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 10

EB: Data flow and tasks ● On BCP each FPGA concentrates FE-data from lpGBT links ● 300 channels are decompressed using FIFOs ● Single crystal energy deposit is calculated ● Linearization ● FIR filter ● Peak finder ● Amplitude to energy LUT ● Lateral sharing ● Spike rejection though swiss cross or other algorithm(s) ● Additional clustering is under consideration ● Data are transmitted to calo L1T Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 11

Barrel calorimeter schedule summary MREFC Funding Start MREFC Completion CDR PDR FDR CY17 17 CY18 18 CY19 19 CY20 20 CY21 CY22 22 CY23 23 CY24 24 CY26 CY16 16 CY25 25 Des esign gn and and Dev evel elopm opmen ent (under under op oper erat ations ons pr progr ogram am) Pre- e-Produc oduction on Produc oduction on BCP Construction Testing ng and and Int ntegr egrat ation on Project Pre- e-Produc oduction on Schedu edule e Float oat (MREFC) Produc oduction on FE Testing ng and nd Integr egrat ation on Sche hedu dule e Float oat Need- eed- Int’l by by-dat date FE TDR BCP-PRR EDR FE-PRR CMS BCP LHC LS 2 LS Run un 4 Run un 2 Run un 3 LS LS 3 HL-LHC Operations V1.1 Nov 19 , 2017 Start TDR – Technical Design Report (Reviewed & Approved by LHCC 2018) EDR – Engineering Design Review PRR – Production Readiness Review 12 months of float from delivery to need by date= 20% of baseline duration Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 12

BCAL Near term milestones Milestone Date Comment Complete testjng of VFE V1 Q1 2019 CATIA V1 + commercial ASIC Complete testjng of LVR V1 Q1 2019 Compatjble with VFE V1 and FE V1 Complete testjng of FE V1 Q4 2018 GBTx version completed * Decision on data compression Q1 2019 Cooling study Q1 2019 Complete testjng of BCP V1 Q2 2019 Single FPGA version Complete testjng of VFE V2 Q4 2019 CATIA V1 + LiTE-DTU V1 Complete testjng of LVR V2 Q4 2019 Compatjble with VFE V2 and FE V2 Complete testjng of FE V2 Q4 2019 lpGBT version * This is driven by schedule of FE electronics. For BE, affects number of boards for production, no impact on BE design Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 13

Preconstruction Schedule Use multiple levels of FW and HW tests for risk mitigation ● Clock distribution and FW/FPGA simulation ● Demonstrator chains ● Single FPGA prorotype ● Full prototype ● Preproduction board tests (included in construction project) Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 14

CMS Document 12897 Summary from risk register Risk Description Impact Description RT-402- lGBTX optical links do not meet Design of FE cards, maximum sampling rate, number of 3-01-N requirements required back end cards RT-402- Firmware release does not meet Add firmware engineer for 1-3 months to accelerate 3-03-N requirements development RT-402- lpGBT cannot meet clock jitter Plan alternate design of system to accommodate 3-06-N specification additional clock fiber RT-402- ECAL data compression fails Redesign of FE board. Increase the order of BCP 3-07-N requirements boards to accommodate the additional inputs HCAL requirements are modest compared to performance requirements for ECAL. Therefore risks are associated with ECAL BE system. Extensive technical studies and prototype cycles to verify that baseline design is capable of satisfying all performance requirements Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 15

Partially addresses RT-402-3-03-N EB evaluation chain FE => BE data flow ● Use μTCA based demonstrator (CTP7): test GBT links (FE board) will communicate properly w/ the BCP using GBT protocol (bottom picture) ● Use (CTP7) to evaluate FE-2018 version hosting 5 GBTx chips (right picture) ● Count transmission errors for a week w/ none recorded ● Inject patterns to adapter boards (VICE board) and capture them on the CTP7 (left picture) – VICE -> FE -> CTP7 ● Evaluate the jitter of the distributed clock by the CTP7 on the FE side Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 16

Partially addresses RT-402-3-03-N HCAL evaluation chain FE => BE data flow • The CTP7 has been CTP7 uHTR successfully used to read out data from one HB FE box • FE-Data acquired by the CTP7 were compared both to expected data, and to data acquired by a Phase 1 Optjcal readout: splituer • Acquired data were compatible and in line 5 Gbps data link on with expectations. ~20 meter MultiMode • Required clock optical fibers. manager functions demonstrated HB FE RBX: RM1 RM2 RM3 RM4 Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 17

Partially addresses RT-402-3-07-N Resource/latency studies Test of compression scheme Post-synthesis analysis of 300 single-crystal Trigger Primitive Generator (TGP), based on FENIX logic, indicates the KCU115 as a reasonable choice. Latency study including data transmission times, simulation of decompression and TGP generation. Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 18

BCP demonstrator (BCPd) Single-FPGA demonstrator Fully functional demonstrator card, with reduced channel count for first system- level testing purposes <= include support for multiple clock distribution schemes Partially addresses RT-402-3-06-N Test of clock distribution Pre-FDR || BCAL Bob Hirosky, 13-14 Dec 2018 19

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.