Background memCellsF09 Allen Tanner built an SRAM/ROM generator - PDF document

Background memCellsF09 Allen Tanner built an SRAM/ROM generator program back in 2004 Single- and Double-port SRAM the ROM seems to work fine there are building blocks fabricated examples that work the SRAM isnt as good

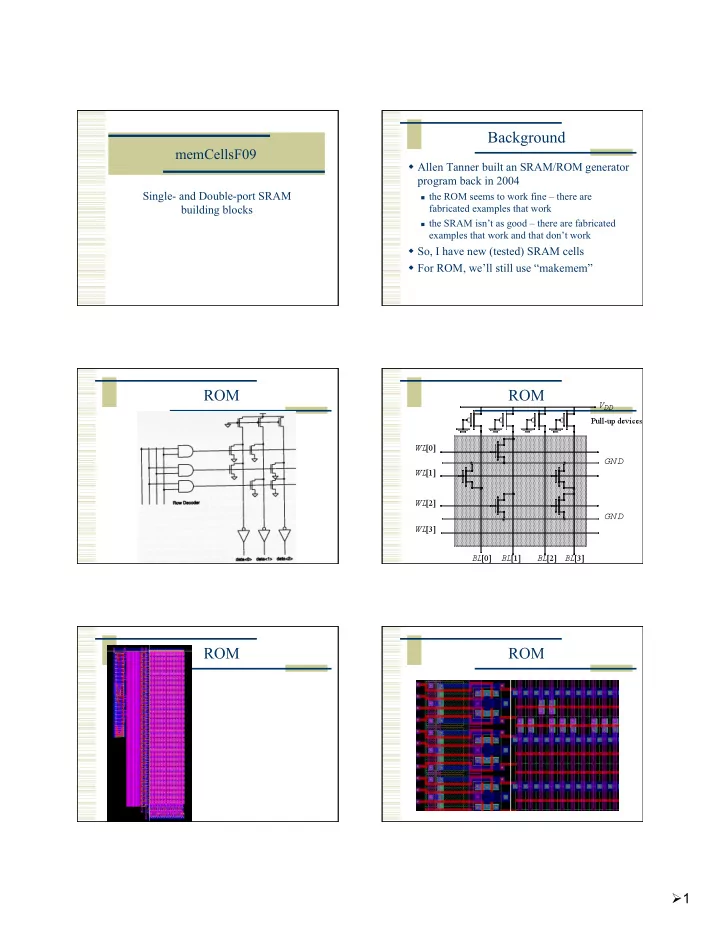

Background memCellsF09 Allen Tanner built an SRAM/ROM generator program back in 2004 Single- and Double-port SRAM the ROM seems to work fine – there are building blocks fabricated examples that work the SRAM isn’t as good – there are fabricated examples that work and that don’t work So, I have new (tested) SRAM cells For ROM, we’ll still use “makemem” ROM ROM ROM ROM 1

ROM Layout ROM Layout makemem makemem Limits 102 vladimir:~> java -cp /uusoc/facility/cad_common/local/Cadence/lib/mem/j makemem -h Number of rows is limited to 64 by address makemem v2.2 Nov 8, 2004 Allen Tanner University of Utah CS6710 decoder design Enter the following: Columns are not restricted java makemem choice options Where: choice selects the creation of either ROM or SRAM. for ROM enter:-r rname : rname.rom is the file name. For ROM you can add a tristate bus at the : for SRAM enter:-s r c : Version 1 SRAM single port. output which is another level of decoding for SRAM enter:-s1 r c : Version 2 SRAM single port. for SRAM enter:-s2 r c : Version 2 SRAM dual port. width must be an even number for SRAM enter:-s3 r c : Version 2 SRAM triple port. : r is the number of rows (decimal). SRAM has single, dual, and triple port : c is the number of columns (decimal). : options :-h -H : help (no processing occurs when help is requested). :-f fname : output file name. Used with .cif, .v & .il files. :-n sname rname : sname for array top cell name. : : rname for ROM (only) dockable ROM array top cell name :-t n : use tristate buffers on the outputs of ROM. :-q : output hello.txt file to find the working file directory. ROM vs. Verilog ROM vs. Verilog 2

ROM vs. Verilog ROM vs. Verilog ROM vs. Verilog ROM vs. Verilog ROM vs. Verilog SRAM Can be tricky Make the SRAM bit cells as small as possible assembled into “columns” A column is bunch of bit cells and the associated support for writing (big drivers) and reading (pullups, sense amps, or inverters) those bits Column “height” is number of words in the memory Columns are tiled in “width” to make the number of bits in a word addressing hardware on the side convert binary addresses into unary row addresses 3

SRAM example (4x8) SRAM Cell SRAM cells R/W circuits Address Column decoder SRAM Cell SRAM Cell (4x4) SRAM Column Support SRAM Column Support 4

Double-port SRAM Double-port SRAM One RW port, one R-only port One RW port, one R-only port duplicates the read circuits for a second port duplicates the read circuits for a second port 2-port column support 2-port column support 2-port example (32x16) memCellsF09 Building blocks for these SRAMs /uusoc/facility/cad_common/local/Cadence/lib/OA/memCellsF09 Make sure to turn “categories” on Things are separated into categories to keep things organized Both 8t (single-port) and 10t (double-port) columns are available in 4, 8, 16, 32, and 64 rows Tile them horizontally to get bits in a word Must be even (columns are two-bits wide) 5

Address Decoders memCellsF09 Library two kinds: static and pseudoNMOS static burns less power, but is slower pseudoNMOS uses more power, but is faster I have speed numbers, but couldn’t find them this morning – I’ll report them next week Memory Size Comparison 4rows by 8bits 32rows by 16bits 32rows by 16bits Dual port 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.