An Adiabatic Power-Supply Controller for An Adiabatic Power-Supply - PowerPoint PPT Presentation

An Adiabatic Power-Supply Controller for An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits Asynchronous Logic Circuits P. Asimakopoulos and A. Yakovlev The 20th UK Asynchronous Forum - The University of Manchester, 1st-2nd

An Adiabatic Power-Supply Controller for An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits Asynchronous Logic Circuits P. Asimakopoulos and A. Yakovlev The 20th UK Asynchronous Forum - The University of Manchester, 1st-2nd September 2008

Summary Summary ● Adiabatic logic background. ● Asynchronous adiabatic implementation. ● Simulations / Evaluation. ● Conclusions. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 2 P Asimakopoulos and A Yakovlev

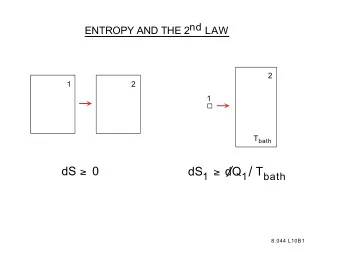

Standard CMOS Energetics Standard CMOS Energetics 1. Charging 2. Discharging V DD V DD Q = CV DD + 2 => E d = QV DD = CV DD C C Q = CV DD The only ways to reduce energy consumption are: 1. Reduce supply voltage V DD . 2. Reduce load capacitance C . An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 3 P Asimakopoulos and A Yakovlev

Adiabatic Logic Adiabatic Logic 1. Charging 2. Discharging Supply Supply 2 2 Q = CV DD Q = CV DD 1 3 1 3 => E d = very small + C C 1. Charge Q is recovered back to the power supply. 2. Charging current becomes uniform and small over ramp time T → energy dissipation is minimized. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 4 P Asimakopoulos and A Yakovlev

Adiabatic Logic Adiabatic Logic I(mA) Voltage/Current/Energy measurements. V(V) Dotted line: Conventional Inverter. Solid line: Adiabatic Inverter. E(pJ) Time J S Denker, “A Review of Adiabatic Computing”, 1994, IEEE Symposium on Low Power Electronics, pp.94-97. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 5 P Asimakopoulos and A Yakovlev

Adiabatic Logic Adiabatic Logic Supply Evaluate Hold “1” Reset Wait Wait Supply IN+ OUT+ OUT- } Dual-rail IN- IN- IN+ OUT+ } Dual-rail OUT- 2N-2P Timing Diagram. Basic 2N-2P Adiabatic Circuit. Kramer A., Denker J.S. et al, “2nd order adiabatic computation with 2N-2P and 2N-2N2P logic circuits”, Proc.1995 Int. Symp. Low power design, pp. 191-196. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 6 P Asimakopoulos and A Yakovlev

Synchronous Adiabatic Logic Synchronous Adiabatic Logic L CLK OUT1+ OUT1- VDD/2 ● One fixed frequency IN1- IN1+ - one global power Power Supply supply. Combinational Logic ● Might require multiple phases of the power supply. OUT3+ OUT3- OUT2+ OUT2- IN2- IN2+ IN3- IN3+ Combinational Combinational Logic Logic An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 7 P Asimakopoulos and A Yakovlev

Asynchronous Adiabatic Logic Asynchronous Adiabatic Logic L CLK REQ VDD/2 Asynchronous ACK OUTPUTS Combinational Logic INPUTS Power Supply ● Multiple frequencies – L many power supplies. CLK REQ VDD/2 ● Space consuming Asynchronous ACK OUTPUTS Combinational Logic design approach. INPUTS Power Supply L CLK REQ VDD/2 Asynchronous ACK OUTPUTS Combinational Logic INPUTS Power Supply An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 8 P Asimakopoulos and A Yakovlev

Asynchronous Adiabatic Logic Asynchronous Adiabatic Logic ( ) VDD SW1 REQ SW3 SW2 SW4 Asynchronous ACK OUTPUTS Combinational ● Using a stepwise charging Logic C1 C2 INPUTS Stepwise Charging Circuit circuit, inductors are ( ) VDD eliminated. SW1 ● Charging/discharging is no REQ SW2 SW3 SW4 Asynchronous ACK OUTPUTS longer ramp-like. Combinational Logic C1 C2 INPUTS Stepwise Charging ● Capacitors still occupy large Circuit ( ) area on chip. VDD SW1 REQ SW2 SW3 SW4 Asynchronous ACK OUTPUTS Combinational Logic C1 C2 INPUTS Stepwise Charging Circuit Willingham D.J. and Kale I., “Asynchronous, quasi-Adiabatic (Asynchrobatic) logic for low-power very wide data width applications”, Circuits and Systems, 2004, Proceedings of the 2004 International Symposium on Volume 2, 23-26 May 2004 pp. II - 257-60 Vol.2. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 9 P Asimakopoulos and A Yakovlev

Proposed Circuit Proposed Circuit Adiabatic Supply Controller Hold “1” ● Only one inductor- Supply Adiabatic based supply. ACK Inputs Evaluate/ Asynchronous Wait Reset Logic ● Ramp-like power Peak H supply generated by individual Peak L Adiabatic Supply adiabatic supply Controller Hold “1” controllers. Supply Adiabatic ACK Inputs Evaluate/ Asynchronous Wait Reset Logic An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 10 P Asimakopoulos and A Yakovlev

Adiabatic Supply Controller Adiabatic Supply Controller Global Supply High Peak 4 Low Peak 2 Request Acknowledge 1 3 Circuit topology. EVALUATE/ 5 RESET WAIT 4 Peak H HOLD “1” 6 Adiabatic 2 Supply Peak L Adiabatic Supply 6 Controller Adiabatic supply controller Hold “1” timing diagram. Supply 1 3 Adiabatic ACK Inputs Evaluate/ Asynchronous Wait Reset Logic 5 An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 11 P Asimakopoulos and A Yakovlev

Adiabatic Supply Controller Adiabatic Supply Controller Global Supply High Peak 2 Low Peak 4 Request Acknowledge 1 3 Circuit topology. EVALUATE/ 5 RESET WAIT 6 2 Peak H HOLD “1” Adiabatic 4 Supply Peak L Adiabatic Supply Controller Adiabatic supply controller Hold “1” timing diagram. Supply 1 3 6 Adiabatic ACK Inputs Evaluate/ Asynchronous Wait Reset Logic 5 An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 12 P Asimakopoulos and A Yakovlev

Adiabatic Supply Controller Adiabatic Supply Controller Acknowledge C HOLD “1” C Peak L EVALUATE / Peak H RESET WAIT C Adiabatic supply controller logic. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 13 P Asimakopoulos and A Yakovlev

Evaluation Evaluation X1 X0 Y0 ● Performance is X0 X1 Y1 evaluated by comparing Z0 2,4,5 -bit asynchronous multipliers implemented in both conventional and adiabatic logic. Half- Half- Z3 Adder Adder Z2 Z1 2-bit Multiplier. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 14 P Asimakopoulos and A Yakovlev

Evaluation Evaluation Acknowledge C A.t S.t S.f C A.f Asynchronous C C Function Block C.t C B.t C.f C B.f ● The dual-rail pipeline handles asynchronous handshaking. ● Is the same for both conventional asynchronous and adiabatic asynchronous logic. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 15 P Asimakopoulos and A Yakovlev

Evaluation Evaluation VDD Acknowledge Supply OUT.f OUT.t PULSE PULSE OUT+ OUT- INPUTS N Transistor Network INPUTS N Transistor Network Acknowledge Modified 2N-2P Circuit. Precharged Differential CMOS Logic. Yeh C.C., Lou J.H. and Kuo J.B., “1.5 V CMOS full-swing energy efficient logic (EEL) circuit suitablefor low-voltage and low-power VLSI applications”, Electronics Letters Volume 33, Issue 16, 31 Jul 1997 pp. 1375 - 1376. J Sparso and S Furber, ”Principles of asynchronous circuit design - A systems perspective”, Kluwer Academic Publishers, 2001. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 16 P Asimakopoulos and A Yakovlev

Simulation Results Simulation Results 16 70 14 60 12 50 Power (uW) 10 Power (uW) 40 8 30 6 4 20 2 10 0 0 0 20 40 60 80 100 120 0 20 40 60 80 100 120 Frequency (MHz) 2-bit multiplier Adiabatic 2-bit multiplier Non-Adiabatic 4-bit multiplier Adiabatic 4-bit multiplier Non-Adiabatic Frequency (MHz) 2-bit Multiplier. 4-bit Multiplier. 120 100 80 Power (uW) 60 40 20 0 0 20 40 60 80 100 120 5-bit multiplier Adiabatic 5-bit multiplier Non-Adiabatic Frequency (MHz) 5-bit Multiplier. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 17 P Asimakopoulos and A Yakovlev

Simulation Results Simulation Results 80 60 40 Improvement (%) 20 0 -20 -40 -60 -80 -100 -120 0 20 40 60 80 100 120 Frequency (MHz) 2-bit multiplier 4-bit multiplier 5-bit multiplier 2,4,5-bit Adiabatic Multipliers power improvement over conventional circuit. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 18 P Asimakopoulos and A Yakovlev

Circuit Weaknesses Circuit Weaknesses ● The operating frequency of the asynchronous logic blocks is limited by the sine-wave supply frequency (can introduce to the handshaking, an additional delay of 3 times the sine-wave period). ● The adiabatic supply controller induces a power consumption overhead. This makes the circuit inefficient for simple logic implementations. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 19 P Asimakopoulos and A Yakovlev

Future Future Acknowledge Peak H C HOLD “1” C Peak L Peak L EVALUATE / Peak H RESET WAIT C Metastability. Peak detectors/sine-wave generator are ideal. An Adiabatic Power-Supply Controller for Asynchronous Logic Circuits 20 P Asimakopoulos and A Yakovlev

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.