All-Digital PLL Frequency and Phase Noise Degradation Measurements - PowerPoint PPT Presentation

All-Digital PLL Frequency and Phase Noise Degradation Measurements Using Simple On-Chip Monitoring Circuits Gyusung Park, Bongjin Kim*, Minsu Kim, Vijay Reddy** and Chris H. Kim University of Minnesota, Minneapolis, MN, USA *Nanyang

All-Digital PLL Frequency and Phase Noise Degradation Measurements Using Simple On-Chip Monitoring Circuits Gyusung Park, Bongjin Kim*, Minsu Kim, Vijay Reddy** and Chris H. Kim University of Minnesota, Minneapolis, MN, USA *Nanyang Technological University, Singapore **Texas Instruments, Dallas, TX, USA park1582@umn.edu chriskim.umn.edu

Purpose • Experimental study of all-digital PLL (ADPLL) reliability issues • ADPLL frequency and phase window measurements using on-chip monitors 2

Outline • Motivation • Proposed on-chip monitors • 65nm ADPLL chip test setup • Stress, recovery, annealing results • Conclusions 3

Target Circuit: All-Digital Phase Locked Loop (ADPLL) Control 0 or 1 output F ref Digitally Phase PI Controlled Detector Controller Oscillator F out =N*F ref Freq. Divider ÷ N Key building block for processor clock • generation and wireless communication No prior work on ADPLL reliability behavior • 4

ADPLL Reliability Figure-of-Merit V. Reddy, et al., IEDM 2009 DCO: Digitally Controlled Oscillator Frequency: open-loop and closed-loop • Phase noise, jitter degradation • 5

Drawback of Conventional Off-chip Measurement • Requires high speed probes or packages, off- chip drivers and connectors • Each of these components introduces inaccuracy in the measurement 6

Outline • Motivation • Proposed on-chip monitors • 65nm ADPLL chip test setup • Stress, recovery, annealing results • Conclusions 7

Beat Frequency Monitor Reset Counter “Silicon Odometer”, T. Kim, et al., JSSC 2008 “Silicon odometer” beat frequency detection circuit • adopted for frequency measurements Higher precision (~ps) and shorter measurement time (~ μ s) • compared to simple counter based scheme 8

Beat Frequency Monitor Before Stress 9

Beat Frequency Monitor Under Stress 10

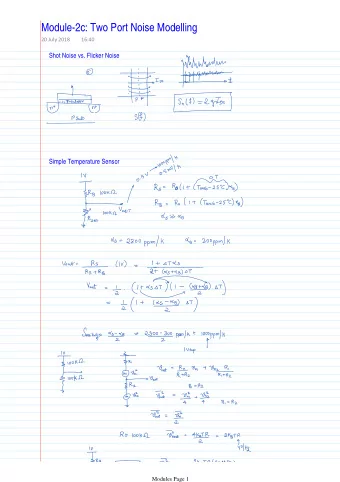

Phase Window Monitor D. Jiao, JSSC 2012 • Clock period (including jitter) compared with tunable delay • Indirectly measure phase noise by sweeping tunable delay 11

Phase Window Measurement As tunable delay approaches • the clock period, error rate increases 12

Phase Window Measurement As tunable delay increases • beyond the clock period, error rate decreases Phase window in right • figure = a measure of phase noise 13

Outline • Motivation • Proposed on-chip monitors • 65nm ADPLL chip test setup • Stress, recovery, annealing results • Conclusions 14

Die Photo and Chip Description Process 65nm CMOS System All-Digital PLL Nominal supply 1.2V Stress supply 2.4V Annealing temp. 110°C, 240°C DCO frequency 720MHz @1.2V (free running) 1.54GHz @2.4V 0.08mm 2 Circuit area 15

Measurement Setup Oscilloscope DUT Hot Plate Control software Power Supply Pattern Generation & Acquisition No power Equipment @ 110 ° ° ° C, 240 ° ° ° ° C ° 16

Open-loop and Closed-loop Configurations • Stress mode: Stress supply (2.4V) for stressed DCO, 0V for reference DCO • Measurement mode: Nominal supply (1.2V) for both stressed and reference DCOs 17

Outline • Motivation • Proposed on-chip monitors • 65nm ADPLL chip test setup • Stress, recovery, annealing results • Conclusions 18

Open-Loop Results: Frequency (a) Stressed @ 27°C, 2.4V, 1.54GHz (b) Natural recovery @ 27°C, 0V (c) Annealing @ 110°C, 0V (d) Annealing @ 240°C, 0V • Stress BTI, HCI frequency degradation • Natural recovery and annealing • Cool down the chip after annealing remove any residual heat 19

Open-Loop Results: Frequency (a) Stressed @ 27°C, 2.4V, 1.54GHz (b) Natural recovery @ 27°C, 0V (c) Annealing @ 110°C, 0V (d) Annealing @ 240°C, 0V • Stress BTI, HCI frequency degradation • Natural recovery and annealing • Cool down the chip after annealing remove any residual heat 20

Open-Loop Results: Phase Window Phase window @ error rate = 1E-8 • More degradation larger phase window • 21

Closed-Loop Results: Frequency 65nm, 1.2V, 27°C (MHz, closed loop) PLL Frequency DCO Frequency Degradation (%) (open loop) • Feedback loop ensures that output frequency is constant 22

Closed-Loop Results: Phase Window Error rate curves all centered around same frequency due • to feedback loop Longer stress larger phase window • 23

Phase Window Recovery Open-loop Closed-loop • Phase window almost fully recovered after annealing @ 240 ° ° C ° ° 24

Outline • Motivation • Proposed on-chip monitors • 65nm ADPLL chip test setup • Stress, recovery, annealing results • Conclusions 25

Conclusions • ADPLL frequency and phase noise characterized for the first time using on-chip monitors • Phase noise increases with stress for both open-loop and closed-loop configurations • High temperature annealing can be used to recover most of the degradation • Post-stress phase noise measurements critical for reliability assurance 26

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.