A Timing Model for Synchronous Language Implementations in Simulink - PowerPoint PPT Presentation

1 A Timing Model for Synchronous Language Implementations in Simulink Timothy Bourke and Arcot Sowmya School of Computer Science and Engineering University of New South Wales, Sydney and National ICT Australia tbourke@cse.unsw.edu.au

� 1 A Timing Model for Synchronous Language Implementations in Simulink Timothy Bourke and Arcot Sowmya School of Computer Science and Engineering University of New South Wales, Sydney and National ICT Australia tbourke@cse.unsw.edu.au EMSOFT 2006 20061125-1244

2 Outline Simulink and Stateflow ⇒ An Argos block Timing Model Embedding within Simulink Concluding remarks

3 Simulink and Stateflow cycle 1 warmup on every(3, TICK).send(step) [feed==1]/step unsynced • Popular tools [(feed==1) & (print==1)] TICK every(10, TICK)[feed==0] after(48, TICK) print go [feed==1] / step slowup rushstart stopped • Practical focus TICK [feed==1] paperfeed TICK [feed=0] [(feed==1) & (print==0)]/step • Several shortcomings TICK [feed==0] after(10, TICK) [print==0] rushstop stepper 2 step11 step01 step00 step10 STEP STEP STEP entry: pin1=1; pin2=1 entry: pin1=0; pin2=1 entry: pin1=0; pin2=0 entry: pin1=1; pin2=0 STEP feed pin2 pin2 output two pulses shaky pulses Signal Builder print pin1 pin1 output print motor system clock controller Simulation � Model-driven Development

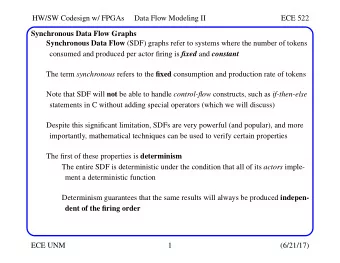

4 Reasoning about Stateflow designs is complicated: 1. intricate ordering rules 2. queued event processing 3. stacking of communications 4. implicit assumption of synchrony Synchronous languages have better underlying models (assumption)

5 An Argos [Mar91, MR01] block: syncblock [BS05] • Our first attempt at combining step11 warmup synchronous languages and unsynced feed / step step / pin1 , pin2 / step [3 tick ] step / pin2 Simulink. [48 tick ] step01 rushstart step / pin2 stopped go . feed go . feed / step slowup tick . feed . print print • Simulate with Argos step / go · · · [10 tick ] tick . feed . print / step step00 feed controllers. tick . feed paperfeed paperfeed . print / step tick . feed step step / pin1 tick . feed . print print tick . feed step10 rushstop [10 tick ] step / pin1 step / pin1 , pin2 tick pin2 pin2 output feed two pulses shaky pulses aside: [CCM + 03, SSC + 04] print Signal Builder pin1 (clock) pin1 output • integrate rather than extract print motor controller system clock • simulate sync. programs

6 syncblock: simulating embedded controllers • Original Prototype : perfect synchrony – Block outputs appear simultaneously with inputs. – i.e. in the same Simulink step. • But , Simulink normally models timing detail. consider: dedicated embedded controllers aim : provide simulation runs with low-level timing detail.

7 syncblock: simulating synchrony perfect e.g. syncblock synchrony Stateflow internal: (semantics) external: (observable) • Revised approach : simulate implementation delays. – Internally: synchronous semantics. – Externally: delay between inputs and outputs. • Necessary to latch inputs and outputs, and to schedule reactions. – Effectively modelling part of the platform (if abstractly).

8 reaction reaction instant computation output τ instant t i +1 t i t i +1 + δ out t i + δ out Idealised parameters • event-driven or sample-driven: mode aside: TAXYS [STY03] • Delay between input and output: δ out • Minimum pause between reactions: τ • Program + Limitations = Simulation (block) = Implementation (model)

9 Outline √ Simulink and Stateflow √ An Argos block Timing Model ⇒ Embedding within Simulink Concluding remarks

10 Transformation to Timed Automata τ ∈ Q + A B = � S, s 0 , I, O, T � fix : 0 δ out ∈ Q + trigger ∈ { sample , event } 0 trigger = event ∨ τ > 0 δ out ≤ τ requiring : A trigger = � Σ , L, L 0 , C, E � : [AD94] then define: τ,δ out . . • Σ = I ∪ O ∪ { react } . • L = ( S ∪ { startup } ) × P ( I ) × P ( O ) × B • L 0 = { ( startup , ∅ , ∅ , ff ) } • C = { x } • E is the smallest set defined by the conjunction of 9 transition rules.

11 (almost) ABRO [Ber00]: in Argos ABRO ( a , b , r )( o ) r a / l 1 b / l 2 / l 1 / l 2 r l 1 · l 2 · ¬ r / o l 1 , l 2

11-a (almost) ABRO [Ber00]: in Argos ABRO ( a , b , r )( o ) r a / l 1 b / l 2 1 loop 2 [ / l 1 / l 2 3 await a 4 || r l 1 · l 2 · ¬ r / o 5 await b 6 ]; 7 emit o 8 each r l 1 , l 2

12 (almost) ABRO: Labelled Transition System r ¬ b · ¬ r r b · ¬ r / o a · ¬ b · ¬ r a · b · ¬ r / o ¬ a · b · ¬ r a · ¬ r / o r , ¬ a · ¬ b ¬ r r ¬ a · ¬ r

13 (almost) ABRO: Timed Transition System r ¬ b · ¬ r r b · ¬ r / o a · ¬ b · ¬ r a · b · ¬ r / o ¬ a · b · ¬ r a · ¬ r / o r , ¬ a · ¬ b ¬ r r ¬ a · ¬ r

13-a (almost) ABRO: Timed Transition System r a ¬ b · ¬ r r b r ab a r r b b · ¬ r / o a · ¬ b · ¬ r a a a b r r r b b a · b · ¬ r / o ab a ab a r r r r b b ¬ a · b · ¬ r a · ¬ r / o r , ¬ a · ¬ b ¬ r a r a b r a b r b r ab a r r b x > 0 ¬ a · ¬ r r a b

14 (almost) ABRO: Timed Transition System trigger = sample a r b ab a r r b a a a b r r r b b ab a ab a r r r r b b a r a b r a b r b ab a r r b x > 0 r a b

14-a (almost) ABRO: Timed Transition System trigger = sample a r b ab a r r b a a a b r r r b b ab a ab a r r r r b b a r a b r a b r b ab a r r b x > 0 r a b react , x = τ, x := 0

14-b (almost) ABRO: Timed Transition System trigger = sample a r b ab a r r b o a a a a b r r r r o b b b o o ab a ab a ab a r r r r r r o b b b o a o r a b r a b r a b r b o ab a r r b x > 0 r a b react , x = τ, x := 0 x = δ out

14-c (almost) ABRO: Timed Transition System trigger = sample a r b ab a r r b o a a a a b r r r r o b b b o o ab a ab a ab a r r r r r r o b b b o a o r a b r a b r a b r b o ab a r r b x > 0 r a b react , x = τ, x := 0 x = δ out

15 Event-driven triggering trigger = event react , x = τ, x := 0 react , x = 0 a a r r b b x ≤ τ x = 0 ab a ab a r r r r b b r a b r a x > τ, x := 0 b • Input events during a reaction must wait until x = τ • Otherwise, they trigger a reaction urgently [BST97]

16 Outline √ Simulink and Stateflow √ An Argos block √ Timing Model Embedding within Simulink ⇒ Concluding remarks

17 Embedding within Simulink simulation time reset triggering latch input react sync. kernel output latch simulation outputs simulation inputs input latch detection sustain output event latch t One block or many?

18 Embedding within Simulink Adopt a semantics for Simulink – Simulation Engine – Intent of models Translate models e.g. to Lustre Interactions of block mix conceptual and low-level operations

19 Mathworks Bang-bang temperature controller [5 SEC] [40 SEC] / LED RED 3 / LED RED [5 SEC] temp / onOk < = + 1 2 + COLD COLD.onOk / BOILER ON ¬ COLD syncblock reference LED + 1 2 SEC boiler syncblock SEC SEC / LED GREEN / BOILER ON [20 SEC] ¬ SEC / LED GREEN 1 sec Timer SEC LED { OFF=0, RED=1, GREEN=2 } LED BOILER CMD { OFF=0, ON=1 } 20 reference TEMP (deg C) actual temp temperature set point boiler on/off temp digital temp Boiler Argos bang-bang controller Plant model

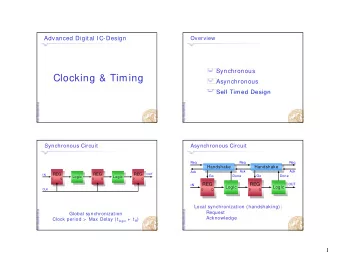

20 Simulink simulation engine: initialization 1 sec Timer SEC LED { OFF=0, RED=1, GREEN=2 } LED BOILER CMD { OFF=0, ON=1 } 20 reference TEMP (deg C) actual temp temperature set point boiler on/off temp digital temp Boiler Argos bang-bang controller Plant model 1. Flatten model

21 Simulink simulation engine: initialization 20 temperature set point + < = + syncblock COLD + 1 sec Timer syncblock heating rate 1 1 (boolean) temp digital temp 1/25 s Data Type digital Conversion 1 Switch thermometer cooling rate -0.1 1. Flatten model

21-a Simulink simulation engine: initialization 10 20 temperature 1 set point 11 0 3 + < = + syncblock COLD + 1 sec Timer 4 syncblock 13 heating rate 1 1 12 15 16 2 5–9 (boolean) temp digital temp 1/25 s Data Type digital Conversion 1 Switch thermometer 14 cooling rate -0.1 1. Flatten model 2. Order by signal dependencies.

21-b Simulink simulation engine: initialization 10 20 temperature 1 set point 11 0 3 + < = + syncblock COLD + 1 sec Timer 4 syncblock 13 heating rate 1 1 12 15 16 2 5–9 (boolean) temp digital temp 1/25 s Data Type digital Conversion 1 Switch thermometer 14 cooling rate -0.1 5. Visit each block—maybe several times. 1. Flatten model 6. Increase t —depends on solver . 2. Order by signal dependencies. 3. Start at t = 0 . 7. repeat from step 5

22 Behaviour of syncblock y = f o ( t, x, u ) outputs syncblock x ′ d = f u ( t, x, u ) update x c previous clock value x t p previous sample time • Two predicates: react and emit . • Instants of interest: δ out = τ [ τ, 0] – sample-driven: [ τ, 0] and [ τ, δ out ] otherwise τ = 0 inherited – event-driven: otherwise zero-crossings

23 Effect of parameters Bang-bang Controller: Stateflow Temperature LED 20 BOILER 15 10 5 0 0 100 200 300 400 500 600 700 800 simulation time

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.