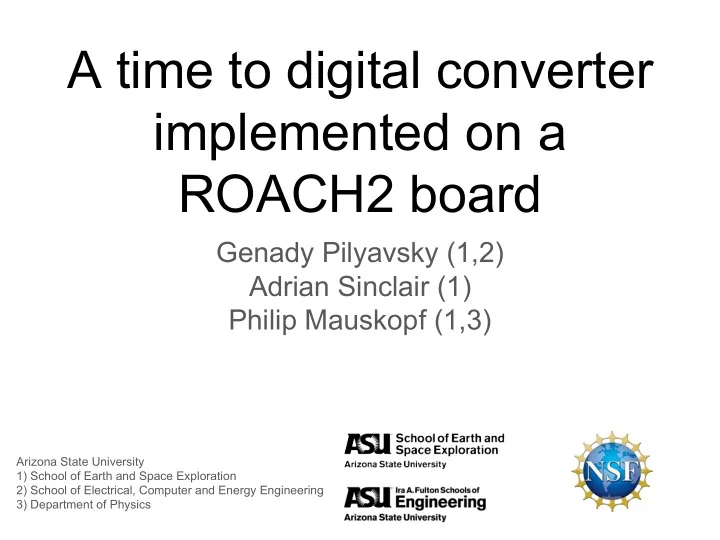

A time to digital converter implemented on a ROACH2 board Genady - PowerPoint PPT Presentation

A time to digital converter implemented on a ROACH2 board Genady Pilyavsky (1,2) Adrian Sinclair (1) Philip Mauskopf (1,3) Arizona State University 1) School of Earth and Space Exploration 2) School of Electrical, Computer and Energy

A time to digital converter implemented on a ROACH2 board Genady Pilyavsky (1,2) Adrian Sinclair (1) Philip Mauskopf (1,3) Arizona State University 1) School of Earth and Space Exploration 2) School of Electrical, Computer and Energy Engineering 3) Department of Physics

Ongoing projects Intensity interferometry ○ - Modern take on Hanbury Brown and Twiss ○ - Single photon detection ○ - km++ baseline ○ - Sub micro-arcsecond resolution

Ongoing projects

Ongoing projects Image Inversion Interferometer ○ - Modified Mach Zehnder Interferometer ○ - Exoplanet Imaging ○ - Contrast reduction ○ - Sub-Rayleigh Resolution

Ongoing projects ● Gravitational Wave Measurement ○ - Piggyback on other projects (Free space optical com) ○ - See Sam Gordon ● Quantum Key Distribution ○ - Modified Mach Zehnder Interferometer, again ○ - One time pad generator ● SNSPD Readout ○ - Multi-dimensional nanowire array ○ - One dimensional “parallel”

Time to digital converter ● What does it do? ○ - Accurate stop watch ○ - Less data vs ADC * ● What do we want? ○ - Continuous data stream ○ - Multiple channels ○ - High timing precision (~100 ps) ○ - Minimal cross talk ○ - Raw output ○ - Cheap

Commercial test ● HydraHarp 400 ● YVX-657 ● TTM8000 ○ Good timing (1ps) ○ Good timing (32ps) ○ 82 ps ○ Continuous ○ Cheap ○ Cheap ○ Black-boxed ○ Not continuous ○ Continuous ○ Expensive ○ Duty cycle ○ Crosstalk ○ Low # of Ch. ○ Crosstalk ○ Low # of Ch.

Commercial test: Cross talk ● TTM8000 ○ Cheap, 82 ps, continuous ○ Crosstalk

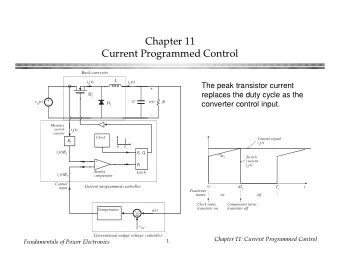

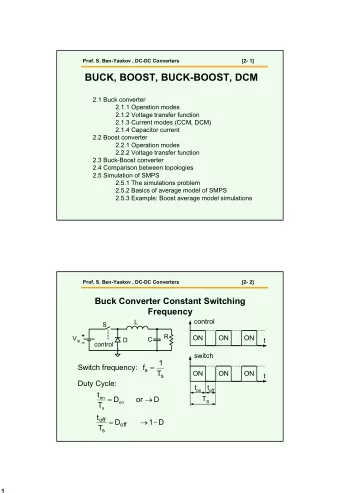

Delay line approach : Overview ● Asynchronous input (GPIO) ● Based on the work by Harald Homulle ○ Series of CARRY4 Primitives ● Bubble filter ● 512 → 9 bit converter ● Dual-ported RAM ● Gigabit Ethernet output

Delay line approach : CARRY4 ● Low resource usage ○ Reg, LUT, DSP48 ~1% ● Room to add more channels ● PBlock for further time constr.?

Delay line approach : CARRY4 ● 4-elements ○ Instantiated to ‘0000’ ● Pulse goes in ○ ‘0000’ flips to ‘1111’ ■ Or ‘1110’ ● Or ‘1100’ ○ Or ‘1000’ ■ Or ‘0000’ ● Output to FDR block ○ Synchronized

Delay line approach : Bubble Correction ● CARRY4 Bubbles ○ ‘1110’ shows up as ‘1101’ ● Fixed with LUT6 ○ ‘1101’ to ‘1110’ ○ ‘1001’ to ‘1100’ ○ etc.

Delay line approach: 512 to 9 bit converter ● Split the data, find the zero ○ - 512 bits to 3 & 64 bits ○ - 64 bits to 3 & 8 bits ○ - 8 bits to 3 bits

Delay line approach: Data Output 00 000000000 000000000000000000000 Channel # Course Counter ~8.4 msec Sub-Clock Rollover allowed 8bit / Clock cycle: 16 ns / photon

Delay line approach : Discontinuities ● Long line ○ - 512 elements ○ - ~240 used ● Different clock regions ● Another gap, same clock region

Preliminary Data: Differential nonlinearity (N/N o -1) Bin #

Preliminary Data: Time delay between channels STD ~ 2.35 bins ( ~40 ps)

Time to digital summery ● What did we get? ○ - Continuous data stream (sort of) ○ - High timing precision (~100 ps) ○ - Minimal cross talk (more tests req.) ○ - Raw output ○ - Cheap

Future development: ● More channels ○ Z-Dock+ ● 2D Delay line tests ● Implementation on series 7 FPGA ○ Manual routing via Vivado

Thank you ● Questions ? ● Comments ?

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.