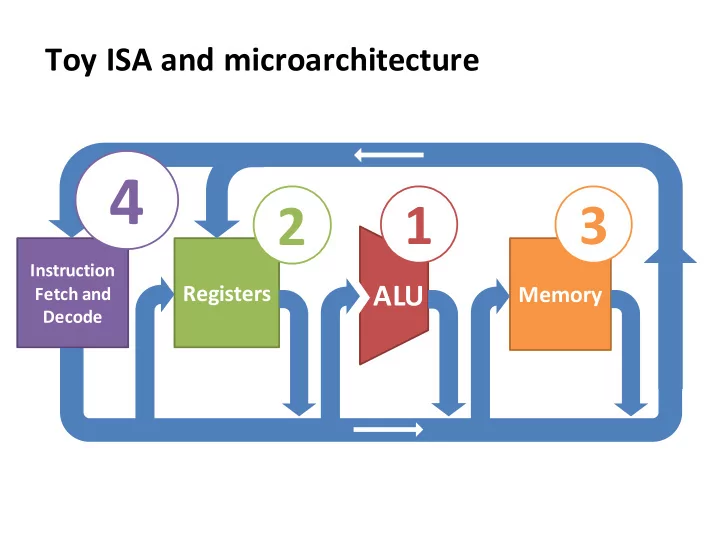

4 1 3 2 Instruction ALU Registers Memory Fetch and Decode - PowerPoint PPT Presentation

Toy ISA and microarchitecture 4 1 3 2 Instruction ALU Registers Memory Fetch and Decode Instruction Set Architecture (HW/SW Interface ) processor memory Instructions Instruction Encoded Names, Encodings Logic Instructions

Toy ISA and microarchitecture 4 1 3 2 Instruction ALU Registers Memory Fetch and Decode

Instruction Set Architecture (HW/SW Interface ) processor memory Instructions Instruction Encoded Names, Encodings • Logic Instructions Effects • Arguments, Results • Registers Data Local storage Names, Size • How many • Large storage Addresses, Locations • Computer

Toy Instruction Set Architecture (a.k.a. Mini-MIPS) • Word size = 16 bits, data bus = 16 bits. • Register size = 16 bits. • ALU computes on 16-bit values. • Memory is byte-addressable , also access words (byte pairs). • 16 registers: R0 - R15 • R0 always holds hardcoded 0 Address Contents • R1 always holds hardcoded 1 0 First instruction, • R2 – R15: general purpose low-order byte • Instructions are 1 word in size. 1 First instruction, high-order byte • Separate instruction memory . 2 Second instruction, • Each instruction executes in low-order byte a single clock cycle. ... ... • Special Program Counter (PC) register • holds address of next instruction to execute. 3

16-bit Encoding Instruction Set MSB LSB Mnemonic Meaning Opcode Rs Rt Rd ADD R s, R t, R d R[ d ] ß R[ s ] + R[ t ] 0010 s t d SUB R s, R t, R d R[ d ] ß R[ s ] - R[ t ] 0011 s t d AND R s, R t, R d R[ d ] ß R[ s ] & R[ t ] 0100 s t d OR R s, R t, R d R[ d ] ß R[ s ] | R[ t ] 0101 s t d LW R t, offset (R s ) R[ t ] ß M[R[ s ] + offset ] 0000 s t offset SW R t, offset (R s ) M[R[ s ] + offset ] ß R[ t ] 0001 s t offset If R[ s ] == R[ t ] then [PC] ß [PC]+2 + offset *2 BEQ R s, R t, offset 0111 s t offset Else [PC] ß [PC]+2 JMP offset [PC] ß offset *2 1000 o f f s e t (R = register file, M = memory) 4

Instruction Encoding: 3 formats All have 4-bit opcode in MSBs Arithmetic instructions: 15:12 11:8 7:4 3:0 - 2 source register IDs (Rs,Rt) - 1 destination register ID (Rd) Op Rs Rt Rd Memory/branch instructions: 15:12 11:8 7:4 3:0 - address/source register ID (Rs) - data/source register ID (Rt) Op Rs Rt offset - 4-bit offset Jump instruction: 15:12 11:0 - 12-bit offset Op offset 5

Instruction Fetch Fetch instruction from memory. Increment program counter (PC) to point to the next instruction. Add 2 Instruction Memory Read PC Address Instruction 6

Arithmetic Instructions Op Rs Rt Rd ADD R3, R6, R8 0010 0011 0110 1000 16-bit Encoding Instruction Meaning Opcode Rs Rt Rd ADD Rs, Rt, Rd R[d] ß R[s] + R[t] 0010 0-15 0-15 0-15 SUB Rs, Rt, Rd R[d] ß R[s] – R[t] 0011 0-15 0-15 0-15 AND Rs, Rt, Rd R[d] ß R[s] & R[t] 0100 0-15 0-15 0-15 OR Rs, Rt, Rd Rd ß R[s] | R[t] 0101 0-15 0-15 0-15 ... 7

Instruction Decode, Register Access, ALU Control 4 Op Unit Write Enable ALU control 4 Read Addr 1 16 Read Rs 16 4 Data 1 Read Addr 2 overflow Rt Register File ALU Instruction zero 4 Write Addr Rd 16 Read ALU result 16 Data 2 Write Data 8

Memory Instructions Op Rs Rt Rd SW R6, 8(R3) 0001 0011 0110 1000 Instruction Meaning Op Rs Rt Rd LW Rt, offset(Rs) R[t] ß Mem[R[s] + offset] 0000 0-15 0-15 offset SW Rt, offset(Rs) Mem[R[s] + offset] ß R[t] 0001 0-15 0-15 offset ... 9

How can we support arithmetic Memory access and memory instructions? What's shared? Control 4 Op Unit Write Enable ALU control 4 MemWrite Read Addr 1 16 Read Rs 16 Data 1 4 Address Read Addr 2 16 Rt ALU Register File Inst 32 Data Memory Write Addr 16 Read Rt Data 2 Read Write 16 Write Data Data Data 4 4 16 Sign Rd extend (offset) 10

MUXes to the rescue! Mem Op Control 4 Op Unit Write Enable ALU control 4 MemWrite Read Addr 1 16 Read Rs 16 Data 1 4 Address Read Addr 2 16 Rt ALU Register File Inst 32 Data Memory Rt MUX 4 Write Addr 16 Read MUX Data 2 Rd Read Write 16 Write Data Data Data 4 16 Rd Sign (offset) extend MUX 11

Control-flow Instructions Op Rs Rt Rd BEQ R1, R2, 28 0111 0001 0010 1110 16-bit Encoding Instruction Meaning Op Rs Rt Rd If R[s] == R[t] then PC ß PC+2 + offset*2 BEQ Rs, Rt, offset 0111 0-15 0-15 offset Else PC ß PC+2 JMP offset PC ß offset*2 1000 o f f s e t ... Use these to implement: conditionals, loops, etc. 12

Compute branch target + Shift left by 1 Control 4 ALU control Unit Write Enable + 2 4 Read Addr 1 Read 16 Instruction Memory Data 1 16 4 Read Addr 2 Read 16 PC ALU Address Register File Inst 32 MUX 4 Write Addr 16 Read MUX Data 2 Write Data 4 Sign 16 extend 13

ex Make branch decision MUX + Shift left by 1 Branch? Control 4 ALU control Unit Write Enable + 2 4 Read Addr 1 Read 16 Instruction Memory Data 1 16 4 Read Addr 2 Read 16 PC ALU Address Register File Inst 32 MUX 4 Write Addr 16 Read MUX Data 2 Write Data 4 Sign 16 extend 14

All together now... MUX + Shift left by 1 Branch? Control 4 ALU control Unit Write Enable + 2 MemWrite 4 Read Addr 1 Read 16 Instruction Memory Data 1 16 4 Address Read Addr 2 Read 16 PC ALU Address Register File Inst 32 Data Memory MUX 4 Write Addr 16 Read MUX Data 2 Read Write 16 Write Data Data Data 4 Sign 16 extend MUX 15

Microarchitecture Single-cycle architecture • Simple, "easily" fits on a slide (and in your head). • One instruction takes one clock cycle. • Slowest instruction determines minimum clock cycle. • Inefficient. Could it be better? • How? Performance, energy, debugging, security, reconfigurability, … • Pipelining • OoO: out-of-order execution • SIMD: single instruction multiple data • Caching • Microcode vs. direct hardware implementation • … enormous, interesting design space of Computer Architecture 16

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.