11/05/2016 R3TOS IN A N UTSHELL R3TOS is a Reliable Reconfigurable - PDF document

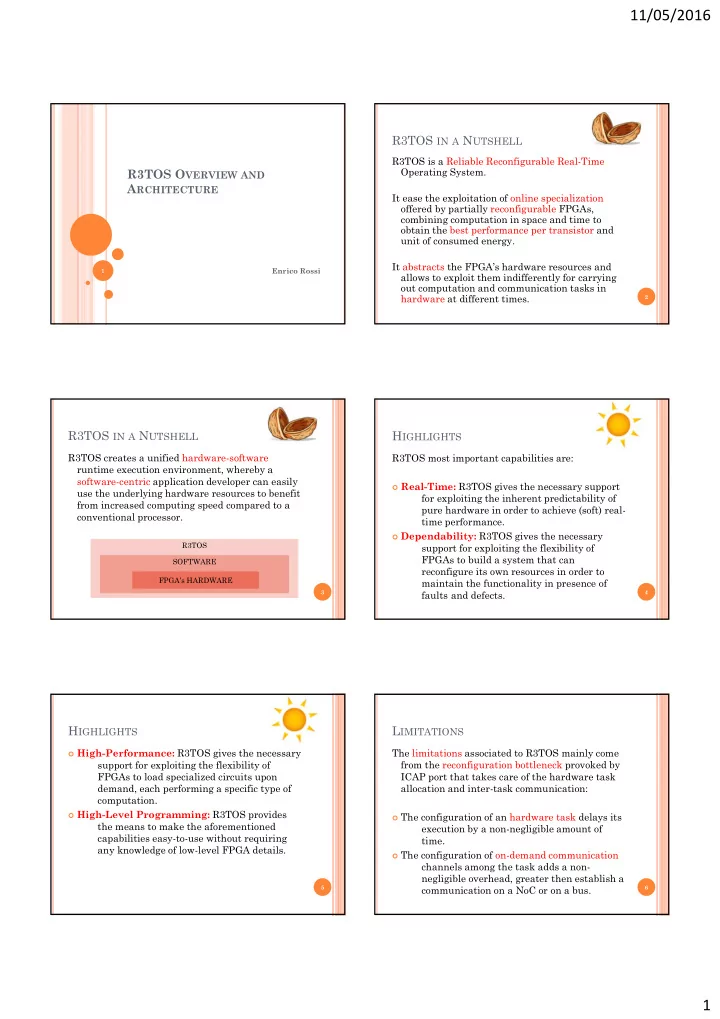

11/05/2016 R3TOS IN A N UTSHELL R3TOS is a Reliable Reconfigurable Real-Time Operating System. R3TOS O VERVIEW AND A RCHITECTURE It ease the exploitation of online specialization offered by partially reconfigurable FPGAs, combining computation

11/05/2016 R3TOS IN A N UTSHELL R3TOS is a Reliable Reconfigurable Real-Time Operating System. R3TOS O VERVIEW AND A RCHITECTURE It ease the exploitation of online specialization offered by partially reconfigurable FPGAs, combining computation in space and time to obtain the best performance per transistor and unit of consumed energy. It abstracts the FPGA’s hardware resources and Enrico Rossi 1 allows to exploit them indifferently for carrying out computation and communication tasks in hardware at different times. 2 R3TOS IN A N UTSHELL H IGHLIGHTS R3TOS creates a unified hardware-software R3TOS most important capabilities are: runtime execution environment, whereby a software-centric application developer can easily Real-Time: R3TOS gives the necessary support use the underlying hardware resources to benefit for exploiting the inherent predictability of from increased computing speed compared to a pure hardware in order to achieve (soft) real- conventional processor. time performance. Dependability: R3TOS gives the necessary R3TOS support for exploiting the flexibility of FPGAs to build a system that can SOFTWARE reconfigure its own resources in order to FPGA’s HARDWARE maintain the functionality in presence of 3 faults and defects. 4 H IGHLIGHTS L IMITATIONS High-Performance: R3TOS gives the necessary The limitations associated to R3TOS mainly come support for exploiting the flexibility of from the reconfiguration bottleneck provoked by FPGAs to load specialized circuits upon ICAP port that takes care of the hardware task demand, each performing a specific type of allocation and inter-task communication: computation. High-Level Programming: R3TOS provides The configuration of an hardware task delays its the means to make the aforementioned execution by a non-negligible amount of capabilities easy-to-use without requiring time. any knowledge of low-level FPGA details. The configuration of on-demand communication channels among the task adds a non- negligible overhead, greater then establish a 5 communication on a NoC or on a bus. 6 1

11/05/2016 B LOCK D IAGRAM H ARDWARE M ICRO K ERNEL R3TOS API Pointers to The Hardware MicroKernel (HWuK) gives the FPGA HW task’s Static support to the main CPU to deal with the bitstream R3TOS Main CPU hardware tasks serving as the substrate upon which the hardware-related services are built. Kernel Extended Features HW task’s bitstream R3TOS Hardware MicroKernel The main offered services are: Software Hardware task queues management; Scheduler Task’s Allocator FPGA Data and FPGA area management; Reconfig. Code Segment Scheduler and Bitstream configuration, allocation Allocator and relocation; Hardware Monitor Task’s Fault detection of the FPGA’s resources. ICAP 7 8 Data Segment ICAP Controller H ARDWARE M ICRO K ERNEL S OFTWARE M ICRO K ERNEL The HWuK’s internal architecture is structured The main CPU is based on a Software MicroKernel around the Xilinx PicoBlaze and has some other (SWuK) that provides the basic platform to custom hardware blocks: execute application software routines which cannot be hardware accelerated or parallelized by computation specialization. Scheduler , expressly designed to schedule hardware tasks; Allocator that manages the FPGA resources; It is based on FreeRTOS so basically executes a ICAP Controller that translates the high-level program which is conceptually similar to a operations dictated by the Scheduler and traditional RTOS but it is extended with extra Allocator into reconfiguration commands. 9 10 functionality to interact with the HWuK. S OFTWARE M ICRO K ERNEL HW U K AND SW U K C OMMUNICATION The SWuK’s extra features consist of: The communication between HWuK and SwuK occurs through a fixed, shared region of the main Scheduling and Hardware task; memory. Forwarding hardware tasks to the HWuK. Shared Memory IDB/ODB This main CPU is implemented using a Xilinx HWuK SWuK ODB/IDB MicroBlaze plus additional communication peripheral (e.g. Ethernet, UART, ecc). The POSIX-like API layer allows to interact with The HWuK cannot directly access the data the FPGA’s hardware through high-level segments of the tasks in the main memory and functions. the mainCPU cannot access the hardware tasks in the FPGA, guaranteeing no interference. 11 12 2

11/05/2016 H ARDWARE T ASK TYPES H ARDWARE T ASK TYPES The term “Hardware Task” is used to indicate that A generic hardware task is composed by the logic the task relies on specific purpose custom circuit plus a communication interface named circuitry to perform computation. TCL (Task Control Logic). Data Stream Processing Tasks: typically A TCL is made by two FIFO buffers and one these are High Bandwidth Communication hardware semaphore: tasks processing large amount of data in a TCL The FIFOs are used to share short time. ODB the data; Hardware Acceleration Tasks: typically these HW The hardware semaphore is Sem are Low Bandwidth Communication tasks used to regulate the access processing reduced amount of data in a large IDB to the hardware task. time. 13 14 H ARDWARE T ASK A LLOCATION & H ARDWARE T ASK A LLOCATION & R ELOCATION R ELOCATION The FPGA can be seen as a field of programmable We can think about this flow: connections and each connection is mapped into a bitstream-memory. Divide the reconfigurable application in tasks; Loading a specific configuration file (bitstream) in the memory would mean program the FPGA to Synthesize the hardware task together with a implement a specific hardware circuit. wrapping Task Control Logic (input and output buffers and an hardware semaphore); We can think to program only a portion of the memory in order to program only a part of the Obtain a single, relocable partial bitstream for FPGA… each of the hardware tasks that can be directly loaded into the bitstream-memory. 15 16 H ARDWARE /S OFTWARE T ASK H ARDWARE /S OFTWARE T ASK C OMMUNICATION C OMMUNICATION TCL (Task Control Logic) blocks attached to The TCL delivers the hardware (or software) tasks provide support for data to be processed Synchronization, Communication and Data from its IDB to the Buffering. task and stores the results into the ODB . HW TASK 1 In case of communication between HW and SW tasks, TCL HW the principle is the same but the TCL of the Data to be TASK ODB Results processed software task is mapped in the program memory. 2 HW HW The hardware tasks are provided with a “ghost Sem software body” which include HWuK-related Data to be IDB processed system calls with the objective of making them 17 18 manageable in SWuK. 3

11/05/2016 A PPENDICE A: FPGA L OGIC E LEMENT One Configurable Logic Block contains two SLICE_M or a SLICE_L and a SLICE_M. R3TOS Reliable Reconfigurable Real-Time Operating System 19 Marco Pagani SLICE_L SLICE_M ROS Overview R3TOS ● ROS ( Reconfigurable operating system ) is an operating ● R3TOS creates a unified HW-SW runtime execution system augmented with functions to manage environment reconfigurable hardware (FPGA) ● R3TOS main features: ● ROS hide complexity by offering a set of basic services , ○ Performance: support for exploiting the flexibility of accessible through an API , to the application developer: FPGAs to load specialized circuits upon demand , ○ task switching each performing a specific type of computation ○ intertask communication ○ Soft real-time: exploiting predictability of pure ○ synchronization hardware to achieve (soft) real-time performance (QoS) ○ etc ... ○ Dependability: exploiting the flexibility of FPGAs to ● Provides runtime support for both task management and maintain functionality in the presence of permanent reconfigurable hardware resource management . defects and spontaneous faults Reconfigurable device support ● An FPGA is a non-homogeneous computing fabric made of reconfigurable resources : ○ Logic cells (CLB) ○ Specific function blocks (BRAM / DSP /… ) ○ Input/Output blocks (IOB) ○ Routing resources (Switch Matrix) Dynamic partial reconfiguration 4

11/05/2016 Reconfigurable device support Reconfigurable device support ● Dynamic Partial Reconfiguration (DPR) allows some ● When using DRP the FPGA is partitioned in: portions of the FPGA to be reconfigured at runtime while ○ Static region (remains unchanged , host static system ) the rest continues to operate ○ Reconfigurable partitions (each can accommodate a set of reconfigurable modules in time-sharing ) ● DRP is the enabling technology for reconfigurable computing Reconfigurable device support Reconfigurable device support ● When using DRP the FPGA is partitioned in: ● A reconfigurable modules can be loaded on a ○ Static region (remains unchanged , host static system ) reconfigurable partition by an embedded ○ Reconfigurable partitions (each can accommodate a microprocessor (softcore) through the Internal set of reconfigurable modules in time-sharing ) Configuration Access Port (ICAP) ● Typically reconfigurable partitions are fixed in the area and organized as islands or slots Reconfigurable device support Reconfigurable device support ● Typically the static system contains a communication ● The static system might cross a reconfigurable partition infrastructure that interconnects all reconfigurable to carry out the routing partitions 5

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.