1 Data path basic building blocks. Register file Storage elements - - PDF document

1 Data path basic building blocks. Register file Storage elements - - PDF document

Levels in Processor Design Register transfer level Circuit design Two types of components (cf. CSE 370) Keywords: transistors, wires etc.Results in gates, flip-flops etc. Combinational : the output is a function of the input

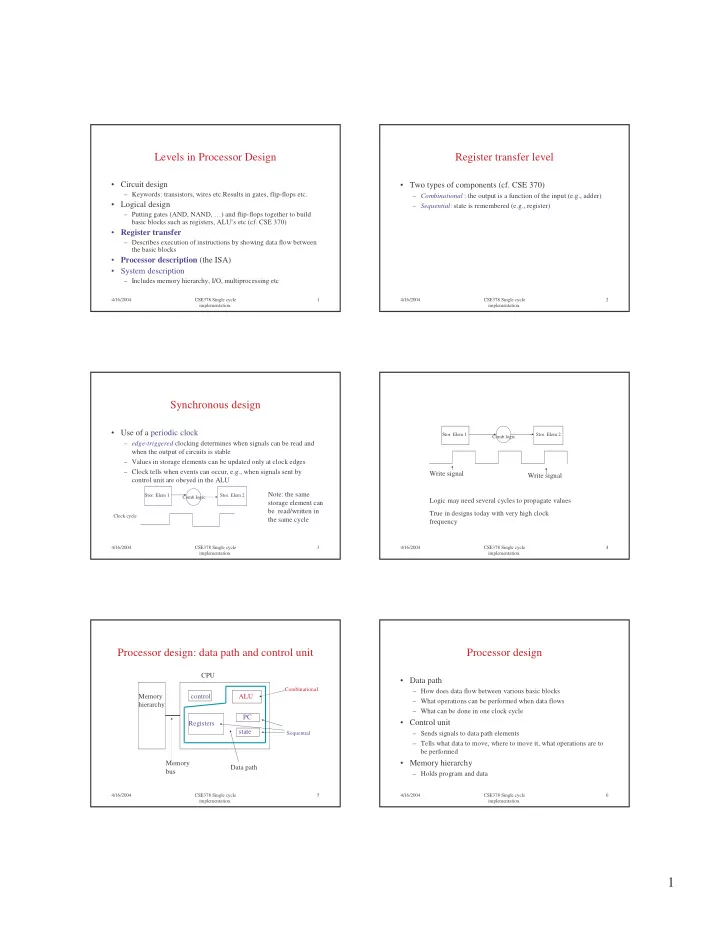

Levels in Processor Design Register transfer level • Circuit design • Two types of components (cf. CSE 370) – Keywords: transistors, wires etc.Results in gates, flip-flops etc. – Combinational : the output is a function of the input (e.g., adder) • Logical design – Sequential : state is remembered (e.g., register) – Putting gates (AND, NAND, …) and flip-flops together to build basic blocks such as registers, ALU’s etc (cf. CSE 370) • Register transfer – Describes execution of instructions by showing data flow between the basic blocks • Processor description (the ISA) • System description – Includes memory hierarchy, I/O, multiprocessing etc 4/16/2004 CSE378 Single cycle 1 4/16/2004 CSE378 Single cycle 2 implementation. implementation. Synchronous design • Use of a periodic clock Stor. Elem 1 Stor. Elem 2 Comb.logic – edge-triggered clocking determines when signals can be read and when the output of circuits is stable – Values in storage elements can be updated only at clock edges – Clock tells when events can occur, e.g., when signals sent by Write signal Write signal control unit are obeyed in the ALU Note: the same Stor. Elem 1 Stor. Elem 2 Comb.logic Logic may need several cycles to propagate values storage element can be read/written in True in designs today with very high clock Clock cycle the same cycle frequency 4/16/2004 CSE378 Single cycle 3 4/16/2004 CSE378 Single cycle 4 implementation. implementation. Processor design: data path and control unit Processor design CPU • Data path Combinational – How does data flow between various basic blocks Memory control ALU – What operations can be performed when data flows hierarchy – What can be done in one clock cycle PC • Control unit Registers state Sequential – Sends signals to data path elements – Tells what data to move, where to move it, what operations are to be performed • Memory hierarchy Memory Data path bus – Holds program and data 4/16/2004 CSE378 Single cycle 5 4/16/2004 CSE378 Single cycle 6 implementation. implementation. 1

Data path basic building blocks. Register file Storage elements • Basic building block (at the RT level) is a register • Array of registers (32 for the integer registers in MIPS) • In our mini-MIPS implementation registers will be 32-bits • ISA tells us that we should be able to: – read 2 registers, write one register in a given instruction (at this • A register can be read or written point we want one instruction per cycle) – Register file needs to know which registers to read/write Input bus Read register number bus 0 Write register number Read register number bus 1 Write enable Register Write enable signal Read data output bus 0 Write data input bus Register file Read data output bus 1 Output bus 4/16/2004 CSE378 Single cycle 7 4/16/2004 CSE378 Single cycle 8 implementation. implementation. Memory Combinational elements • Conceptually, like register file but much larger Multiplexor (MUX): selects the value of one of its Input busses inputs to be routed to the output • Can only read one location or write to one location per cycle Read memory address Mux Select control signal Write memory address Read control signal Write enable Output bus Demultiplexor (deMUX or SEL): routes its input Memory Read data bus Write data bus to one of its outputs Output busses Sel Select control signal Input bus 4/16/2004 CSE378 Single cycle 9 4/16/2004 CSE378 Single cycle 10 implementation. implementation. Arithmetic and Logic Unit (ALU - Putting basic blocks together (skeleton of data combinational) path for arith/logical operations) • Computes (arithmetic or logical operation) output from its Zero result bit Read register number bus 0 Write register number two inputs Read register number bus 1 Write enable Zero result bit Read data 0 ALU Input bus 0 Register file ALU Output bus Read data 1 ALU control Input bus 1 (opcode/function) Write data input bus ALU control (opcode/function) 4/16/2004 CSE378 Single cycle 11 4/16/2004 CSE378 Single cycle 12 implementation. implementation. 2

Introducing instruction fetch PC has to be incremented (assume no branch) Zero result bit Read Reg #0 Read data 0 Read Reg #1 ALU Write Reg # Reg. File Read data 1 ALU control 4 (opcode/function) Adder Write data Instruction address Instruction address Instruction Instr. memory Instr. memory PC PC 4/16/2004 CSE378 Single cycle 13 4/16/2004 CSE378 Single cycle 14 implementation. implementation. Data path for straight code Load-Store instructions Read enable (reg-reg,imm,load/store) Read enable Instruction Instruction Read data 0 Read data 0 Read Reg #0 Read Reg #0 Read Reg #1 Read Reg #1 ALU ALU Data Read data 1 Data Write Reg # Write Reg # R/W address R/W address memory memory Reg. File Reg. File 32-bit “store” data 32-bit Sign Sign. “store” data extend ext 16-bit offset Write enable 16-bit offset Write enable Data from “load” Data for result register Mux 4/16/2004 CSE378 Single cycle 15 4/16/2004 CSE378 Single cycle 16 implementation. implementation. Branch data path ALU 4 Sftl 2 Adder 32-bit Instruction Inst. PC 16-bit memory Sign. ext 4/16/2004 CSE378 Single cycle 17 implementation. 3