1.5. I/O 128 Serial Communication Simplex Duplex Half-Duplex - PowerPoint PPT Presentation

1.5. I/O 128 Serial Communication Simplex Duplex Half-Duplex 129 Serial Communication Master-Slave (Multi-)Master Multi-Slave Master Slave Master Master-Multi-Slave Slave Master Slave Slave Slave Slave 130 Serial Communication

1.5. I/O 128

Serial Communication Simplex Duplex Half-Duplex 129

Serial Communication Master-Slave (Multi-)Master Multi-Slave Master Slave Master Master-Multi-Slave Slave Master Slave Slave Slave Slave 130

Serial Communication Synchronous Master Slave Asynchronous Master Slave 131

Some Bus Types Wires Directionality Synchrony Distance Speed typ. Remarks (+Gnd) typ. RS-232 3/5 – 8 full duplex asynchronous 10 m 115kbps / Point-to-Point +synchronous 1Mbps Interference prone RS-485 3/5 half/full duplex asynchronous 1000 m Mbps Differential Signalling SPI [aka SSP, 4 full duplex synchronous few cm 10 Mbps Master-Multi-Slave Microwire] with Slave select I 2 C 2 half duplex synchronous few m 100kbps- Addressed Multi-Master [SMBus] 3Mbps 1-Wire 1 half duplex time-slot tens of m 15kbps/ Master-Multi-Slave based, 125kbps Parasitic power synchronous USB 2.0 3/5 half-duplex asynchronous few m 12Mbits/ isochronous/ bulk/ 480 MBits interrupt transfers USB 3.0 5 full-duplex asynchronous few m 5/10 GBits 132

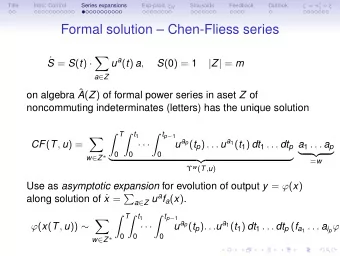

SPI SCLK MOSI shift shift Master Slave MISO register register SS SS SCLK : Serial bit-rate Clock MOSI : Master data Output, Slave data Input shift Slave register MISO : Master data Input, Slave data Output SS : Slave Select 133

SPI Four wire serial bus invented / named by Motorola Serial connection between two or more devices (microprocessors, D/A converters) Configurations 1 Master, 1 Slave (single slave mode) 1 Master, N Slaves (multiple slave mode) Synchronous bidirectional data transfer Data transfer initiated by Master Bandwidth some KBits/s up to several MBits/s Simple implementation in software Used in a variety of devices, such as memory (flash, EEPROM), LCD displays and in all MMC / SD cards 134

Communication sampling SCLK SS MOSI Bit[7] Bit[6] Bit[5] Bit[1] Bit[0] End of transfer data state undefined Bit[7] Bit[6] Bit[5] Bit[1] Bit[0] undefined MISO MSB 8 bits LSB 135

Polarity Polarity = 0 SCLK Polarity = 1 Bit[7] Bit[6] Bit[5] Bit[1] Bit[0] End of transfer data state 136

Phase Phase = 0 SCLK Phase = 1 Bit[7] Bit[6] Bit[5] Bit[1] Bit[0] End of transfer data state 137

SPI – Data Transfer Master configures the clock Master selects slave (SS), followed by waiting period (if required by slave) Full duplex data transmission in each cycle Master sends bit over MOSI line, slave reads bit Slave sends bit over MISO line, master reads bit Two shift registers, one in slave, one in master for transfer When no data is to be transmitted any more, master stops toggling the clock No acknowledgement mechanism No device interrupts 138

Programming SPI 1. Bit-Banging Master GPIO Pins 139

Programming SPI 1. Bit-Banging FOR i := 7 TO 0 BY -1 DO IF ODD(ASH(data,-i)) THEN Platform.WriteBits(Platform.GPSET0, MOSI); ELSE Platform.WriteBits(Platform.GPCLR0, MOSI); END; Kernel.MicroWait(HalfClock); Platform.WriteBits(Platform.GPSET0, CLOCK); Kernel.MicroWait(HalfClock); Platform.WriteBits(Platform.GPCLR0, CLOCK); END; 140

Programming SPI 2. Using a Controller Master SPI Controller 141

Programming SPI 2. Using a Controller (* start transition *) Platform.SetBits(Platform.SPI_CS, {TA}); REPEAT UNTIL TXD IN Platform.ReadBits(Platform.SPI_CS); Platform.WriteWord(Platform.SPI_FIFO, data); junk := Platform.ReadWord(Platform.SPI_FIFO); REPEAT UNTIL DONE IN Platform.ReadBits(Platform.SPI_CS); (* transfer inactive *) Platform.ClearBits(Platform.SPI_CS, {TA}); 142

BCM 2835 Registers CLK CS -- Control and Status FIFO Register Clock Divider Chip Select Data FIFO Status Transfer Progress Other Interrupts Read: Write: DMA Control Polarity & Phase RX Fifo TX Fifo Special Mode Control 143

MAX7219 8-Digit LED Display Driver Max7219 Specification, p.5 144

MAX7219 8-Digit LED Display Driver Max7219 Specification, p.6 145

MMC and SD Cards Low cost memory system for persistent data on „solid state mass storage “ ( for example flash memory cards) Separate bus system 1 master, N slaves (cards) typically 1 master for one card Serial & synchronous transfer of commands and data Sequential read/ write Power Bus Block read/ write Supply Master Multi Media Card Bus Card Card Card (I/O) (ROM) (Flash) 146

MMC System Interaction Command and Clock for Response synchronous Channel transfer Host (BCM 2835) SD Card CLK CPU CMD Core EMMC SD Card Pins GPIO Pins DAT Controller SD Card Interface Controller Memory Bidirectional Data Channels 147

SD Card V DD CLK DAT0 DAT2 CMD DAT3 DAT1 OCR[31:0] CID[127:0] Power On Detection RCA[15:0] DSR[15:0] Card Interface Controller CSD[127:0] reset SCR[63:0] SSR[511:0] CSR[31:0] Memory Core Interface reset Memory Core SD Physical Layer Spec. P. 12 148

SD Mode vs SPI Mode Dat2Dat3CMD VDD GNDDat0 Dat1 CLK CS DI VDD CLK GND DO (Micro) SD Card Header SPI-MODE 149

Block Read/ Write Operation Read stop command from host to card from card to host data from card to host stops data transfer command response command response CMD data block crc data block crc data block crc DAT[0-7] block read operation data stop operation multiple block read Write data from host to card stop command from host to card from card to host stops data transfer busy from card to host command response command response CMD data block crc busy data block crc busy DAT[0-7] data stop operation block write operation multiple block write SD Physical Layer Spec. P. 6ff 150

Packet Formats Command and Response end bit, transmitter Command content: command and address information of Command bit, 1=host always 1 parameter, protected by 7 bit CRC checksum Token 0 1 Content CRC 1 48 bits start bit, always 0 Response 0 0 Content CRC 1 Response types R1, R3. R4, R5 * Tokens Response content, mirrored command and status transmitter information (R1 response), OCR register (R3 respone) or bit, 0=client RCA (R4 and R5), protected by 7-bit checksum 0 0 Content = CID or CSD CRC 1 Response type R2 * 136 bits 151

Example: MMC Memory Card State Diagram (boot mode) Idle State CMD0 from all states card busy Power or missing voltage range go idle state on CMD1 Inactive State CMD15 send op cond Ready State non compatible voltage range cards card looses bus CMD2 all send CID card wins bus Identification State set relative adr CMD3 card identification mode data transfer mode Wait IRQ Stand-by CMD40 State State from all states except set irq mode sleep state in data transfer more any start bit detected on the bus 152 interrupt mode

RS232 Terminal [ DTE ] Data Set [ DCE ] (Modem) TxD UART RxD UART GND + RTS/RTR CTS if Hardware Flow Control 153

RS232 Signalling Sampling in the middle of bit intervals Time [+3v , +15 v] 0 v MSB LSB [-3v ,-15 v] start bit 8 data bits 1-2 stop bit(s) starts the local clock (+parity, if applicable) 154

UART Universal Asynchronous Receiver/ Transmitter Serial transmission of individual bits in byte packets (lowest significant bit first) Configurable source: Wikipedia Number of data bits per byte: 5, 6, 7, 8 Parity: odd, even, none Number of stop bits: 1, 1.5, 2 Transfer rate in bps (bits per second): 75, 110, 300,... , 115200 155

Implementation out in Port 2. Sender Send Line 1. Sender FIFO IRQ Trigger Sender buffer Application Hardware level Receiver buffer reached in IRQ Receiver FIFO 1. Receiver Receive Line 2. Port out UART Driver UART 156

Producer Consumer Implementation Assumption: one consumer and one producer in Producer WHILE (in+1) MOD bufferSize = out DO END; buffer[in] := produced; Buffer in = (in+1) MOD bufferSize; out Consumer WHILE in = out DO END; consumed := buffer[out]; out := (out+1) MOD bufferSize; 157

Driver Method Send Put data in sender buffer; Update in (sender) Method Receive Get data from receiver buffer; Update out (receiver) Sender-Interrupt Shift data from sender buffer to sender FIFO; Update out (sender) Receiver Interrupt Shift data from receiver FIFO to receiver buffer; Update in (receiver) 158

1.6. FILE SYSTEM 159

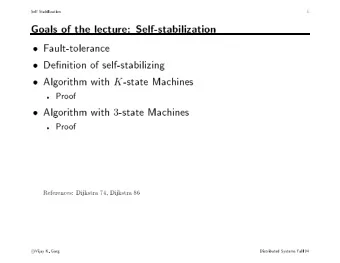

Modular Structure Sequential files Files as byte sequences Files Riders for reading/writing Buffering Flat name space B-tree representation FileDir node block Block Sequences BlockDevice Block allocation Read/ write block 160

API Abstract data types File , Rider File* = POINTER TO FileDesc; FileDesc * = RECORD … END; Open file (new or via name) Rider* = RECORD Close file eof*: BOOLEAN; … Position rider in file hint*: Buffer; file*: File; Read next byte via rider END; Write next byte via rider 161

Block Structure of Files directory d d d d 128 x 4K= 1MB 1K mark d d d d d header name d d length time 1K 0 index d 1 d d d d d d 1K x 4M= entries 4GB 127 1K 1K i 2 i 1 i 1 128 i 1 i 1 i 1 i 1 i 1 d i 1 d d d d d d file 1K x 4K= 4MB (3528 B) data index data blocks blocks 4B 162

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.