Worst-Case Analysis of Digital Control Loops with Uncertain - PowerPoint PPT Presentation

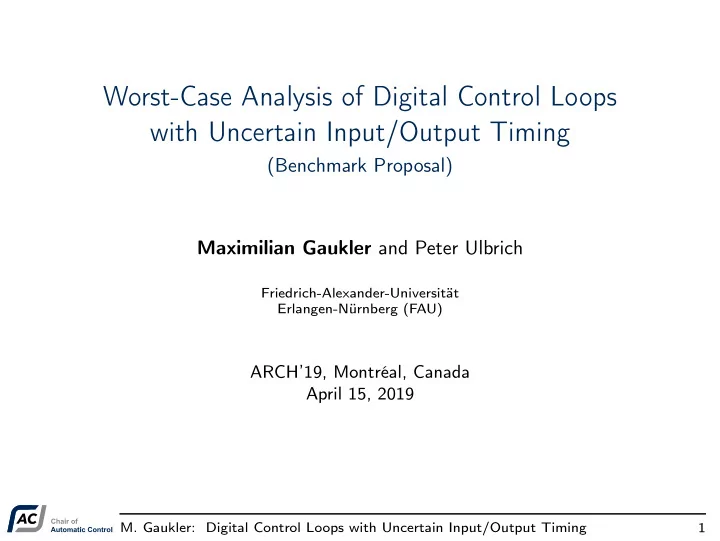

Worst-Case Analysis of Digital Control Loops with Uncertain Input/Output Timing (Benchmark Proposal) Maximilian Gaukler and Peter Ulbrich Friedrich-Alexander-Universitt Erlangen-Nrnberg (FAU) ARCH19, Montral, Canada April 15, 2019 M.

Worst-Case Analysis of Digital Control Loops with Uncertain Input/Output Timing (Benchmark Proposal) Maximilian Gaukler and Peter Ulbrich Friedrich-Alexander-Universität Erlangen-Nürnberg (FAU) ARCH’19, Montréal, Canada April 15, 2019 M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 1

Motivation M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 2

Motivation Plant Controller M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 2

Motivation Controller Design: input/output assumed periodic Plant Controller M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 2

Motivation Controller Design: input/output assumed periodic Plant Controller Other applications and controllers Real-time computing system M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 2

Motivation Controller Design: input/output assumed periodic Plant Controller Other applications and controllers Real-time computing system M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 2

Motivation Controller Design: input/output assumed periodic Plant Modern Real-Time Systems: • Network / bus systems • Smart sensors • High complexity Controller Other applications and controllers Real-time computing system M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 2

Motivation Controller Design: input/output assumed periodic Plant Modern Real-Time Systems: • Network / bus systems • Smart sensors • High complexity � Strict timing is difficult! Controller Other applications and controllers Real-time computing system M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 2

Motivation Input timing Output timing Controller Design: input/output assumed periodic Plant Modern Real-Time Systems: • Network / bus systems • Smart sensors • High complexity � Strict timing is difficult! Controller Desired Alternative: Allow some timing deviation � Formal safety guarantees? Other applications and controllers Real-time computing system M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 2

Timing Model: Periodic Timing Windows ( k − 1) T ( k + 1) T kT t Sample Sample Sample y [ k − 1] y [ k ] y [ k + 1] Compute u [ k ] Compute u [ k + 1] Actuate Actuate Actuate u [ k − 1] u [ k ] u [ k +1] dataflow M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 3

Timing Model: Periodic Timing Windows ( k − 1) T ( k + 1) T kT t Sample Sample Sample y [ k − 1] y [ k ] y [ k + 1] Compute u [ k ] Compute u [ k + 1] Actuate Actuate Actuate u [ k − 1] u [ k ] u [ k +1] dataflow M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 3

Timing Model: Periodic Timing Windows ( k − 1) T ( k + 1) T kT t 0 ∆ t Sample Sample Sample y [ k − 1] y [ k ] y [ k + 1] Compute u [ k ] Compute u [ k + 1] Actuate Actuate Actuate u [ k − 1] u [ k ] u [ k +1] dataflow M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 3

Timing Model: Periodic Timing Windows ( k − 1) T ( k + 1) T kT t ∆ t 0 ∆ t ∆ t Sample Sample Sample y [ k − 1] y [ k ] y [ k + 1] Compute u [ k ] Compute u [ k + 1] Actuate Actuate Actuate u [ k − 1] u [ k ] u [ k +1] dataflow M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 3

Formalization: Hybrid Automata clock ( τ , startOfCycle ) u next , 1 y 1 y d , 1 u 1 Sample-and-Hold Sample-and-Hold with timing uncertainty with timing uncertainty . . Controller . . . Plant . and Clock Sample-and-Hold Sample-and-Hold u next ,m u m y p y d ,p with timing uncertainty with timing uncertainty M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 4

Formalization: Hybrid Automata clock ( τ , startOfCycle ) u next , 1 y 1 y d , 1 u 1 Sample-and-Hold Sample-and-Hold with timing uncertainty with timing uncertainty . . Controller . . . Plant . and Clock Sample-and-Hold Sample-and-Hold u next ,m u m y p y d ,p with timing uncertainty with timing uncertainty Controller ( x d ) 0 startOfCycle always T τ = T/ 2 2 τ = 1 , ˙ x d = 0 ˙ τ ′ = − T/ 2 , Clock ( τ ) 0 − T/ 2 ≤ τ ≤ T/ 2 x ′ d = f d ( x d , y d ) − T 2 0 T 2 T t Controller output: u next = g d ( x d ) M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 4

Formalization: Hybrid Automata clock ( τ , startOfCycle ) u next , 1 y 1 y d , 1 u 1 Sample-and-Hold Sample-and-Hold with timing uncertainty with timing uncertainty . . Controller . . . Plant . and Clock Sample-and-Hold Sample-and-Hold u next ,m u m y p y d ,p with timing uncertainty with timing uncertainty x p ( t ) = f p ( x p ( t ) , u ( t ) , d ( t )) ˙ y ( t ) = g p ( x p ( t ) , d ( t )) d ( t ) ∈ D • Multiple inputs and outputs • Bounded disturbance and measurement noise M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 4

Formalization: Hybrid Automata clock ( τ , startOfCycle ) u next , 1 y 1 y d , 1 u 1 Sample-and-Hold Sample-and-Hold with timing uncertainty with timing uncertainty . . Controller . . . Plant . and Clock Sample-and-Hold Sample-and-Hold u next ,m u m y p y d ,p with timing uncertainty with timing uncertainty ∆ t ≤ τ ≤ ∆ t wait out ′ = in done ˙ out = 0 ˙ out = 0 startOfCycle τ ≤ ∆ t t 0 ( T + ∆ t ) T ( T + ∆ t ) 2 T M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 4

Benchmark Setup 1 System model: network of hybrid automata • Machine-readable, unambiguous M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 5

Benchmark Setup 1 System model: network of hybrid automata • Machine-readable, unambiguous 2 Verification goal: tight worst-case bounds (infinite-time reachable set) • Metric: bloating factor M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 5

Benchmark Setup 1 System model: network of hybrid automata • Machine-readable, unambiguous 2 Verification goal: tight worst-case bounds (infinite-time reachable set) • Metric: bloating factor x 2 analysis x 1 simulation a b a = “ upper bound from analysis ” K = b worst observed in simulation M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 5

Benchmark Setup 1 System model: network of hybrid automata • Machine-readable, unambiguous 2 Verification goal: tight worst-case bounds (infinite-time reachable set) • Metric: bloating factor 3 Example systems • Linear, no disturbance • From 1D examples to a simplified 3-axis quadrocopter controller M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 5

Benchmark Setup 1 System model: network of hybrid automata • Machine-readable, unambiguous 2 Verification goal: tight worst-case bounds (infinite-time reachable set) • Metric: bloating factor 3 Example systems • Linear, no disturbance • From 1D examples to a simplified 3-axis quadrocopter controller 4 Experiments with SpaceEx: Success only for trivial examples Reachable set over time: � 1D, small uncertainty � 1D, large uncertainty × 3D, perfect timing (!) M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 5

Summary and Outlook • Problem: Timing uncertainties in digital control • Hard to avoid • Verification is challenging, but of high practical relevance M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 6

Summary and Outlook • Problem: Timing uncertainties in digital control • Hard to avoid • Verification is challenging, but of high practical relevance • Is a pure hybrid-automata approach suitable here? M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 6

Summary and Outlook • Problem: Timing uncertainties in digital control • Hard to avoid • Verification is challenging, but of high practical relevance • Is a pure hybrid-automata approach suitable here? • � Future work: “non-hybrid” alternatives • Continuous-time abstraction: continuization • Discrete-time: LMI-based robust stability M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 6

Summary and Outlook • Problem: Timing uncertainties in digital control • Hard to avoid • Verification is challenging, but of high practical relevance • Is a pure hybrid-automata approach suitable here? • � Future work: “non-hybrid” alternatives • Continuous-time abstraction: continuization • Discrete-time: LMI-based robust stability Can your tool solve the benchmark? http://qronos.de → Files and code (GPLv3) M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 6

Appendix M. Gaukler: Digital Control Loops with Uncertain Input/Output Timing 7

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.